低Cgd电容功率MOSFET的制备方法与流程

低cgd电容功率mosfet的制备方法

技术领域

1.本发明涉及功率mosfet的制备方法,特别涉及低cgd电容功率mosfet的制备方法。

背景技术:

2.功率mosfet(power metal oxide semiconductor field-effect transistor,场效应晶体管)以其开关速度快、频率性能好、输入阻抗高、驱动功率小、温度特性好、无二次击穿问题等优点,大量应用在4c(即communication,computer,consumer,car:通信,电脑,消费电器,汽车)等领域中。

3.传统的功率trench mosfet器件,其栅极同漏极之间只有一层薄的栅氧化层,故栅漏电容cgd较大,也即qgd较大。

技术实现要素:

4.针对传统的功率trench mosfet器件所存在的栅漏电容cgd较大的问题,提供一种栅漏电容cgd较小的低cgd电容功率mosfet的制备方法。

5.为了实现上述发明目的,本发明的低cgd电容功率mosfet的制备方法,包括如下步骤:

6.步骤1:准备衬底及外延材料,其中外延材料位于衬底之上;

7.步骤2:在外延材料的表面上进行第一次氧化,形成一层第一氧化层;

8.步骤3:在第一氧化层上蚀刻出沟槽,该沟槽穿透第一氧化层进入外延材料中;

9.步骤4:在第一氧化层和沟槽侧壁及底部淀积一层si3n4层;

10.步骤5:etchback刻蚀掉第一氧化层上及沟槽底部的si3n4层,在沟槽的侧壁形成si3n4侧墙(spacer);

11.步骤6:对si3n4侧墙之间沟槽的槽底进行第二次氧化,形成第二氧化层;

12.步骤7:蚀刻掉si3n4侧墙,露出原先被si3n4侧墙遮盖住的外延材料;

13.步骤8:对露出原先被si3n4侧墙遮盖住的外延材料进行第三次氧化,形成第三氧化层;

14.步骤9:在第一氧化层、第二氧化层和第三氧化层表面淀积多晶硅,多晶硅填满沟槽;

15.步骤10:etchback去除第一氧化层表面上的多晶硅层,保留沟槽内的多晶硅;

16.步骤11:在外延材料表面上制作p-body层和n+/p+层,其中n+/p+层位于p-body的上表面;p+区域位于n+区域的中间;

17.步骤12;在n+/p+层的表面上淀积cvd层并在cvd层上对应每一n+/p+层中间位置进行source开孔,露出p+区域和相邻部分n+区域;

18.步骤13:在cvd层上进行金属化。

19.在本发明的一个优选实施例中,所述第二氧化层的厚度大于所述第三氧化层的厚度。

20.在本发明的一个优选实施例中,所述第三次氧化为栅极氧化,第三氧化层为栅极氧化层。

21.在本发明的一个优选实施例中,步骤9和步骤10中,所述多晶硅为栅极多晶硅。

22.由于采用了如上的技术方案,本发明的沟槽底部的中间部分是第二氧化层(厚氧化层),使得栅漏电容cgd较小,也即qgd较小。

附图说明

23.图1a至图1k为本发明低cgd电容功率mosfet的制备方法的示意图。

具体实施方式

24.以下结合附图和具体实施方式来进一步描述本发明。

25.参见图1a至图1k,本发明的低cgd电容功率mosfet的制备方法,包括如下步骤:

26.步骤1:参见图1a,准备衬底1及外延材料2,其中n-外延层2位于n+衬底1之上;

27.步骤2:参见图1b,在n-外延层2的表面2a上进行第一次氧化,形成一层第一氧化层3;

28.步骤3:参见图1c,在第一氧化层3上蚀刻出沟槽4,该沟槽4穿透第一氧化层3进入n-外延层2中;

29.步骤4:参见图1d,在第一氧化层3和沟槽4侧壁及底部淀积一层si3n4层5;

30.步骤5:参见图1e,etchback刻蚀掉第一氧化层3上及沟槽4底部的si3n4层5,在沟槽4的侧壁形成si3n4侧墙6(spacer);

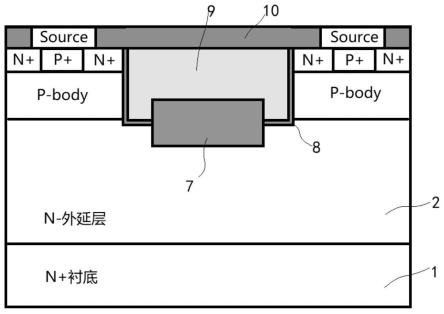

31.步骤6:参见图1f,对si3n4侧墙6之间沟槽底部进行第二次氧化,形成第二氧化层7;

32.步骤7:参见图1g,蚀刻掉si3n4侧墙6,露出原先被si3n4侧墙6遮盖住的外延材料;

33.步骤8:参见图1h,对露出原先被si3n4侧墙6遮盖住的外延材料进行第三次氧化(栅氧化),形成第三氧化层8(栅氧化层);

34.步骤9:参见图1h,在第一氧化层3、第二氧化层7和第三氧化层8(栅氧化层)表面淀积多晶硅9(栅极多晶硅),多晶硅9(栅极多晶硅)填满沟槽;

35.步骤10:参见图1i,etchback去除第一氧化层3表面上的多晶硅层9,保留沟槽内的多晶硅9(栅极多晶硅);

36.步骤11:参见图1j,在外延材料表面上制作p-body层和n+/p+层,其中n+/p+层位于p-body的上表面;p+区域位于n+区域的中间;

37.步骤12;参见图1k,在n+/p+层的表面上淀积cvd层10并在cvd层10上对应每一n+/p+层中间位置进行source开孔,露出p+区域和相邻部分n+区域;

38.步骤13:参见图1k,在cvd层10上进行金属化。

技术特征:

1.低cgd电容功率mosfet的制备方法,其特征在于,包括如下步骤:步骤1:准备衬底及外延材料,其中外延材料位于衬底之上;步骤2:在外延材料的表面上进行第一次氧化,形成一层第一氧化层;步骤3:在第一氧化层上蚀刻出沟槽,该沟槽穿透第一氧化层进入外延材料中;步骤4:在第一氧化层和沟槽侧壁及底部淀积一层si3n4层;步骤5:etchback刻蚀掉第一氧化层上及沟槽底部的si3n4层,在沟槽的侧壁形成si3n4侧墙(spacer);步骤6:对si3n4侧墙之间沟槽的槽底进行第二次氧化,形成第二氧化层;步骤7:蚀刻掉si3n4侧墙,露出原先被si3n4侧墙遮盖住的外延材料;步骤8:对露出原先被si3n4侧墙遮盖住的外延材料进行第三次氧化(栅氧化),形成第三氧化层(栅氧化层);步骤9:在第一氧化层、第二氧化层和第三氧化层表面淀积多晶硅(栅极多晶硅),多晶硅(栅极多晶硅)填满沟槽;步骤10:etchback去除第一氧化层表面上的多晶硅层,保留沟槽内的多晶硅(栅极多晶硅);步骤11:在外延材料表面上制作p-body层和n+/p+层,其中n+/p+层位于p-body的上表面;p+区域位于n+区域的中间;步骤12;在n+/p+层的表面上淀积cvd层并在cvd层上对应每一n+/p+层中间位置进行source开孔,露出p+区域和相邻部分n+区域;步骤13:在cvd层上进行金属化。2.如权利要求1所述的低cgd电容功率mosfet的制备方法,其特征在于,所述第二氧化层的厚度大于所述第三氧化层(栅氧化层)的厚度。3.如权利要求1或2所述的低cgd电容功率mosfet的制备方法,其特征在于,所述第三次氧化为栅极氧化,第三氧化层为栅极氧化层。4.如权利要求1或2所述的低cgd电容功率mosfet的制备方法,其特征在于,步骤9和步骤10中,所述多晶硅为栅极多晶硅。

技术总结

本发明公开的低Cgd电容功率MOSFET的制备方法,其在对Si3N4侧墙之间沟槽的底部进行第二次氧化,形成第二氧化层;所述第二氧化层的厚度大于所述第三氧化层(栅氧化层)的厚度。本发明的沟槽底部的中间部分是第二氧化层(厚氧化层),使得栅漏电容Cgd较小,也即Qgd较小。也即Qgd较小。也即Qgd较小。

技术研发人员:黄平 鲍利华 顾海颖

受保护的技术使用者:上海朕芯微电子科技有限公司

技术研发日:2022.05.05

技术公布日:2022/9/2

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1