基于无线高速总线的新型封装系统芯片NPSC架构的制作方法

基于无线高速总线的新型封装系统芯片npsc架构

技术领域

1.本发明涉及集成电路技术领域,具体涉及一种基于无线高速总线 的新型封装系统芯片npsc架构。

背景技术:

2.21世纪初,随着集成电路制造工艺技术的发展,集成电路设计也 逐渐进入系统芯片soc(systemonachip)。

3.系统芯片soc包含如下特性:实现复杂系统功能的超大规模集成 电路;采用超深亚微米工艺技术;使用一个或数个嵌入式cpu核或数 字信号处理器(dsp);主要采用第三方的ip核进行设计。

4.其中一般基于片上高速总线的soc芯片架构如图1所示,当前超 大规模集成电路芯片,比如人工智能soc系统芯片一般内部包含寄存 器(register)规模一般都是几千万规模级,如果按晶体管算规模一般 都是几百亿规模,这么大的芯片规模一般都需要设计人员先从功能上 将任务划分成若干子任务分别交由不同的子系统(sub-system)完成, 然后再通过片上高速总线(high-speedbus)将不同子系统连接在一起, 其架构大致如图2所示。

5.根据上面的介绍,可看出系统芯片soc的核心就是将ip核或子系 统连接在一起的片上高速(high-speed)总线,它们都是有线(wire) 方式,普遍采用铜工艺技术,在超深制造工艺技术下这种连线延时 (wiredelay)已经成为限制芯片性能关键因素。

6.根据报道,高通发布的首款5nm芯片骁龙x60最高速率达7.5gbps, 因此一般最新的5nm芯片的性能由于芯片连线延时的物理限制,数据 传送能力大致在4g~10g级别。而当前基于子系统的复杂系统芯片的规 模大到惊人程度,比如人工智能soc系统芯片一般内部包含寄存器 (register)规模一般都是几千万规模级,而晶体管规模一般都是几百 亿规模,它们所承载的人工智能任务又要求需要这些子系统之间进行 大数据交互传送,有线高速总线的物理线延时(wiredelay)也直接限 制了这种数据传送带宽。

7.传统的sip封装是一种电子器件封装方案,将多种功能芯片,包括 处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完 整的功能。传统的sip封装如图3所示。

8.这里的芯片连接都是基于点对点的端口连接。当前,基于小芯片 (chiplet)的新型封装技术方兴未艾。什么是小芯片chiplet,这里的 let是名词,指的是出租出售的意思,换句话说就是出租的芯片,就是 指已经完成cp测试(chipprobe)的被证实没有制造缺陷(fault)的 且完成切片的裸片(gooddie)。

9.chiplet至少应该包含以下含义:完成cp测试(chipprobe)且没 有制造缺陷;完成切片的裸片(gooddie);完成部分封装操作,为后 续新型封装(2.5d或3d封装)预留的封装凸点。

10.综上,复杂系统芯片csoc(complexsoc)这种超大规模集成电路 芯片对连接各子系统之间的片上高速总线的数据传送带宽需求与实际 有线高速总线的数据传送带宽能力

之间的矛盾就显得异常突出,为了 进一步提升数据传送带宽能力,本文提出一种全新的基于无线高速总 线的新型封装系统芯片(npsc:newpackagesystemchip)架构试图彻底 解决问题。

技术实现要素:

11.针对现有技术的不足,本发明公开了一种基于无线高速总线的新 型封装系统芯片npsc架构,用于解决复杂系统芯片csoc(complexsoc) 这种超大规模集成电路芯片对连接各子系统之间的片上高速总线的数 据传送带宽需求与实际有线高速总线的数据传送带宽能力之间矛盾的 问题。

12.本发明通过以下技术方案予以实现:

13.本发明提供了一种基于无线高速总线的新型封装系统芯片npsc架 构,由一个或多个小芯片相互堆叠或该一个或多个小芯片与一个或多 个存储裸片相互堆叠构成,该一个或多个小芯片或存储裸片堆叠构成 的多层平面经由穿透硅通孔tsv在z方向连接起来,并使用3dic封装 技术进行三维立体组装;其中,该一个或多个小芯片通过高速总线与 大数据备份中心进行数据交互,同时该一个或多个小芯片均集成有硅 基光收发器ip模块,且该一个或多个小芯片集成的硅基光收发器ip 模块连接同一激光发生器。

14.更进一步的,所述一个或多个小芯片相互堆叠或该一个或多个小 芯片与一个或多个存储裸片相互堆叠或并排放置在具有硅通孔的中介 层顶部,所述具有硅通孔的中介层设置于基板之上。

15.更进一步的,所述具有硅通孔的中介层设置有封装凸点,所述具 有硅通孔的中介层设置具有信号重分布互连层,并用于布线,所述具 有硅通孔的中介层的硅通孔用于与所述基板连接,所述基板设置有封 装微凸点。

16.更进一步的,所述基板的制备具体工艺步骤如下:

17.采用丙酮、乙醇、去离子水超声清洗硅片10min,然后n2吹干;

18.溅射沉积40-60nm厚的粘附层ti和450-550nm厚的种子层cu;

19.采用硫酸铜电镀液在原始基板上下表面双面电镀cu层,电镀电流 为90-110ma,电镀时间为8-12min,电镀铜膜厚约6-8μm;

20.采用光亮电镀锡溶液在基板样品表面双面镀锡,电镀电流为45-5 5ma,电镀时间为8-12min,电镀膜厚约3-5μm;

21.氮气吹干基板表面,置于氮气柜中保存。

22.更进一步的,所述微凸点的制作包含以下步骤:

23.在晶圆上通过pvd技术依次沉积ti阻挡层和cu种子层,然后在温 度为140-160℃的烤箱中烘烤1.4-1.6h;

24.旋转涂布,光刻使pr图形化,使待电镀线路区域的种子层露出;

25.光刻后,通过电镀技术形成cu线路层,然后湿法去除pr;

26.重新旋转涂布,通过光刻技术形成具有直径的圆形通孔,其中通 孔底部为cu线路层;

27.等离子清洗晶圆然后电镀微凸点,湿法去除pr,并相继湿法刻蚀 掉cu种子层和ti阻挡层后,得到具有线路连接的微凸点。

28.更进一步的,电镀的微凸点是cu柱、cu/snag或者cuni/snag;其 中,snag钎料中ag的含量约为1.8土0.5wt.%e电镀所形成微凸点的高 度误差小于1um。

29.更进一步的,使用3dic封装技术进行三维立体组装时使用粘胶键 合,在待键合面上旋涂一层液态聚合物薄膜,同时加入固化剂及助黏 剂,将键合界面上的图形对准并紧密贴合,且聚合物和键合界面接触 充分但是不溢出,最后采用加热、烧结或特殊光照方式使液态聚合物 固化,实现键合。

30.更进一步的,使用粘胶键合时,包括以下预处理步骤:

31.通过去离子水清洗晶圆,在温度为140-160℃的烤箱中烘烤 1.4-1.6h,以去除晶圆表面的水汽;

32.通过ar和oz等离子体轰击晶圆表面,以去除晶圆表面的微尘颗 粒或脏污;

33.通过异丙醇ipa清洗,并涂布助黏剂以使粘结剂层涂覆后与晶圆 表面紧密结合。

34.更进一步的,使用3dic封装技术进行三维立体组装时使用cu-sn 共晶键合,在真空环境或者保护环境下,利用低温金属sn的融化,形 成液态sn,使cu和sn充分接触形成亚稳态金属间化合物cu6sn5,并 进一步与cu反应生成稳态化合物cu3sn以实现键合。

35.更进一步的,所述激光发生器通过硅基光收发器ip模块与大数据 备份中心进行数据交互用于数据备份。

36.本发明的有益效果为:

37.本发明将小芯片堆叠在一起或与存储裸片堆叠在一起,无需构建 复杂片上系统,将大型复杂系统芯片分解为较小的小芯片chiplet,与 单颗裸片相比具有更高的良率和更低的成本,解决了超大规模集成电 路芯片对连接各子系统之间的片上高速总线的数据传送带宽需求与实 际有线高速总线的数据传送带宽能力之间矛盾的问题。

38.本发明3dic集成将芯片在垂直方向借助tsv和凸点进行堆叠以形 成高度集成的系统可以充分发挥tsv最短线互连的特点,具有高性能、 宽带宽、低功耗、低信号延迟小尺寸等优势。

附图说明

39.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面 将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而 易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域 普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些 附图获得其他的附图。

40.图1是本发明背景技术一般系统芯片soc架构图;

41.图2是本发明背景技术基于子系统的复杂系统芯片csoc图;

42.图3是本发明背景技术传统的sip封装示意图;

43.图4是本发明实施例基于小芯片chiplet的新型封装的封装系统芯 片架构图;

44.图5是本发明实施例2.5d封装技术示意图;

45.图6是本发明实施例3d封装技术示意图;

46.图7是本发明实施例粘胶键合时预处理原理图。

47.具体实施方式

48.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结 合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、 完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是 全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有 做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护 的范围。

49.实施例1

50.参照图3所示,本实施例提供一种基于无线高速总线的新型封装 系统芯片npsc架构,由一个或多个小芯片相互堆叠或该一个或多个小 芯片与一个或多个存储裸片相互堆叠构成;其中,该一个或多个小芯 片均集成有硅基光收发器ip模块,且该一个或多个小芯片集成的硅基 光收发器ip模块连接同一激光发生器。

51.本实施例的一个或多个小芯片相互堆叠或该一个或多个小芯片与 一个或多个存储裸片相互堆叠或并排放置在具有硅通孔的中介层顶 部。

52.本实施例进行优选的实施时,将具有硅通孔的中介层设置于基板 之上,更进一步的在具有硅通孔的中介层设置封装凸点。

53.本实施例具有硅通孔的中介层设置具有信号重分布互连层,并用 于布线。具有硅通孔的中介层的硅通孔用于与所述基板连接。

54.本实施例基板设置有封装微凸点,更进一步的基板两端设置有加 固器。

55.本实施例激光发生器通过硅基光收发器ip模块与大数据备份中心 进行数据交互用于数据备份。

56.本实施例无线高速总线的核心是基于硅基光收发器ip模块。且每 一个小芯片都包含一个硅基光收发器ip模块。

57.本实施例无线高速总线的新型封装系统芯片npsc架构一个系统共 享一个激光发生器。小芯片存在一个chiplet向其他多个chiplets传送 数据的可能。

58.实施例2

59.在实施例1的基础上,本实施例对基于无线高速总线的新型封装 系统芯片npsc架构使用2.5d封装技术进行封装,具体参见图4,其中 stiffener为加固器;substrate为衬底;interposer为硅中介层;bump 为凸点;u-bump为微凸点。

60.本实施例新型封装系统芯片中,小芯片(chiplet)堆叠在一起或 与存储裸片堆叠在一起,无须构建复杂片上系统。

61.本实施例2.5d封装是传统2dic封装技术的升级,可实现更精细的 线路与空间利用。

62.本实施例2.5d封装中,裸片堆叠或并排放置在具有硅通孔(tsv: throughsiliconvia)的中介层顶部。

63.本实施例在chiplet和封装基板之间存在的硅中介层上制造的die 之间具有信号重分布互连层(rdl)(这个差不多类似于常规的金属导 电层,用于布线route),而硅通孔(tsv)提供与基板的连接。

64.本实施例将大型复杂系统芯片分解为较小的小芯片chiplet,与单 颗裸片相比具

有更高的良率和更低的成本。

65.实施例3

66.在实施例2的基础上,本实施例更进一步的对基于无线高速总线 的新型封装系统芯片npsc架构使用3d封装技术进行封装,具体参见 图5,从3d封装的截面图可以看出,通过金属铜tsv实现了硅芯片之 间垂直互连。

67.本实施例3d封装主要采用金属-金属键合方式来实现多层垂直互 连,本实施例cu-sn键合原理为:温度升高后,金属sn熔化,与cu 反应生成亚稳态金属间化合物cusns(熔点415℃),随后cu,sns与cu进 一步反应生成稳态金属间化合物cuzsn251(熔点676℃)。

68.本实施例由于合金相熔点高于cu-sn共晶键合温度,因此在多层 芯片堆叠时,后续键合的加热过程不会对前面已形成的键合层造成影 响。

69.本实施例中,由于焊料sn具有良好的形变特性,cu-sn键合对键 合表面的平整度及洁净度要求不高,即使在表面起伏相对较大或存在 微小颗粒的情况下也可以形成良好键合。由于在键和过程中,sn是液 态,能够加速cu和sn之间的相互扩散过程,故cu-sn键合具有较低 条件和较高效率。

70.本实施例将大型复杂系统芯片分解为较小的小芯片chiplet,与单 颗裸片相比具有更高的良率和更低的成本。但基于硅通孔tsv (throughsiliconvia)技术的线延时的有线高速总线连接也与csoc一 样有数据传送带宽限制。

71.实施例4

72.在实施例3的基础上,本实施例更进一步的对基于无线高速总线 的新型封装系统芯片npsc架构使用3d封装技术进行封装,本实施例 使用粘胶键合,首先,在待键合面上旋涂一层液态聚合物薄膜,保证 其厚度和均匀性的同时调整好固化剂、助黏剂等添加剂的用量;然后, 将键合界面上的图形对准并紧密贴合,保证聚合物和键合界面接触充 分但是不至于溢出,以免造成污染;最后采用加热、烧结、特殊光照 等方式使液态聚合物固化,实现键合。其键合强度较强。

73.本实施例在3dic集成中,采用w2w方式将两片晶圆通过粘结剂永 久键合在一起,其中一面晶圆背部减薄(如通过背部研磨、cmp或湿法 刻蚀等)至soi晶圆中的埋氧层(buriedoxide)或刻蚀停止层,然后在相 应位置制作tsv以使堆叠晶圆之间形成垂直互连。

74.本实施例上下两晶圆先通过粘结剂永久键合在一起,然后再制作 tsv,所以制作高深宽比的tsv增加了工艺难度和成本,尤其是对于制 作小孔径的tsv。另外,粘结剂较大的变形性易引起键合后的偏移,这 也限制了粘结剂的应用。因此本实施例粘结剂键合多用于对键合后偏 移要求不苛刻的器件中,或者与其它键合技术结合在一起以提高键合 强度。

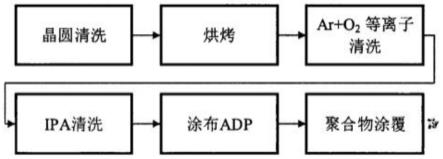

75.如图7所示,本实施例粘胶键合时,预处理主要有以下五个步骤:

76.(1)通过去离子水清洗晶圆;

77.(2)在温度为150℃的烤箱中烘烤1.5h,以去除晶圆表面的水汽;

78.(3)通过ar和oz等离子体轰击晶圆表面,以去除晶圆表面的微尘 颗粒或脏污;

79.(4)异丙醇(ipa)清洗,为涂布助黏剂做准备;

80.(5)涂布助黏剂(adp),以使粘结剂层涂覆后与晶圆表面紧密结合。

81.本实施例在表面预处理后,及时地将粘结剂层涂覆于晶圆表面。 对于pi和df粘结

剂,分别采用旋转涂布和真空压膜的方式。

82.本实施例对于pi粘结剂,先将适量的液态pi粘结剂置于晶圆表面 上,然后旋转晶圆使pi粘结剂均匀涂覆,通过调整旋转涂布的速率来 控制pi粘结剂的最终厚度。

83.本实施例对于df粘结剂先将固态df粘结剂覆盖于晶圆上,然后 在真空中通过压膜将df粘结剂填充于微凸点之间,并使df粘结剂与 晶圆表面紧密结合。其中,真空压膜的压力为4kg/cm2,温度为95℃, 时间为3min。压膜后无需软烤即可进行光刻使微凸点由df粘结剂中暴 露出来。

84.实施例5

85.在实施例3的基础上,本实施例更进一步的对基于无线高速总线 的新型封装系统芯片npsc架构使用3d封装技术进行封装,本实施例 使用cu-sn低温键合,本实施例通过低熔点金属的熔化形成液态,提 高键合介质金属间的扩散和反应速率,降低键合条件。

86.本实施例中,在cu-sn键合过程中,当温度升高使sn融化为液态 之后,cu/sn迅速反应,并生成固态金属间化合物,实现低温键合。

87.本实施例cu-sn键合原理为:温度升高后,金属sn熔化,与cu 反应生成亚稳态金属间化合物cu6sn5(熔点415℃),随后cu6sn5与 cu进一步反应生成稳态金属间化合物cu3sn(熔点676℃)。

88.本实施例中,由于合金相熔点高于cu-sn共晶键合温度,因此在 多层芯片堆叠时,后续键合的加热过程不会对前面已形成的键合层造 成影响。

89.此外,由于焊料sn具有良好的形变特性,cu-sn键合对键合表面 的平整度及洁净度要求不高,即使在表面起伏相对较大或存在微小颗 粒的情况下也可以形成良好键合。由于在键和过程中,sn是液态,能 够加速cu和sn之间的相互扩散过程,故cu-sn键合具有较低条件和 较高效率。

90.实施例6

91.在实施例1的基础上,本实施例提供一种基板的制备具体工艺步 骤如下:

92.采用丙酮、乙醇、去离子水超声清洗硅片10min,然后n2吹干;

93.溅射沉积50nm厚的粘附层ti和500nm厚的种子层cu;

94.采用硫酸铜电镀液在样品上下表面双面电镀cu层,电镀电流为 100ma,电镀时间为10min,电镀铜膜厚约7μm;

95.采用武汉材料保护所提供的光亮电镀锡溶液在样品表面双面镀 锡,电镀电流为50ma,电镀时间为10min,电镀膜厚约4μm;

96.氮气吹干样品表面,置于氮气柜中保存,防止氧化。

97.最终获得大量样品芯片,经测试,本实施例cu/sn镀层厚度符合设 计要求,镀层表面平坦,粗糙度为0.4μm。

98.实施例7

99.在实施例1的基础上,本实施例提供一种微凸点制作流程,主要 包含以下步骤:

100.在晶圆上通过pvd技术依次沉积ti阻挡层和cu种子层。首先清洗 晶圆,然后在温度为150

°

℃的烤箱中烘烤1.5h以去除晶圆表面的水 汽,最后pvdti/cu层(阻挡层/种子层)。

101.旋转涂布,光刻使pr图形化,使待电镀线路区域的种子层露出, 光刻后,通过电镀

技术形成cu线路层,然后湿法去除pr。

102.重新旋转涂布,通过光刻技术形成具有一定直径的圆形通孔,通 孔底部为cu线路层。

103.等离子清洗晶圆以去除通孔底部pr残留,然后电镀微凸点。本实 施例中电镀的微凸点可以是cu柱、cu/snag或者cuni/snag。

104.本实施例中,snag钎料中ag的含量约为1.8+0.5wt.%。电镀所形 成微凸点的高度误差小于1um。

105.湿法去除pr,并相继湿法刻蚀掉cu种子层和ti阻挡层后,即可 得到具有线路连接的微凸点。

106.本实施例中,当电镀的微凸点为cu柱时,那么还需要继续通过化 学镍金的方式在cu柱上再沉积ni-p/au层以形成cuni-p/au微凸点。 其中,ni-p层中р的含量约为9wt.%,表面au层的厚度约为0.03um。

107.综上,本发明将小芯片堆叠在一起或与存储裸片堆叠在一起,无 需构建复杂片上系统,将大型复杂系统芯片分解为较小的小芯片 chiplet,与单颗裸片相比具有更高的良率和更低的成本,解决了超大 规模集成电路芯片对连接各子系统之间的片上高速总线的数据传送带 宽需求与实际有线高速总线的数据传送带宽能力之间矛盾的问题。

108.本发明3dic集成将芯片在垂直方向借助tsv和凸点进行堆叠以形 成高度集成的系统可以充分发挥tsv最短线互连的特点,具有高性能、 宽带宽、低功耗、低信号延迟小尺寸等优势。

109.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管 参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员 应当理解:其依然可以对前述各实施例所记载的技术方案进行修改, 或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不 使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1