密集型封装的VCSEL阵列、包括VCSEL阵列的半导体器件及其制造方法与流程

密集型封装的vcsel阵列、包括vcsel阵列的半导体器件及其制造方法

技术领域

1.本发明涉及一种包括垂直腔表面发射激光器(vcsel)阵列的半导体器件。本发明进一步涉及一种制造这种包括vcsel阵列的半导体器件的对应方法。

背景技术:

2.垂直腔表面发射激光器或vcsel是一种半导体激光器二极管,其激光射束从顶表面垂直发射。由于由这些半导体光源提供的高效率、灵活封装选项、可靠性和各种其他优点,vcsel可以在各种应用中用作可见光照明器件和红外照明器件。示例性应用包括但不限于计算机鼠标、光纤通信、激光打印机和光学传感器。

3.在某些应用中,可能期望提供包括多个vcsel的vcsel阵列。对于大规模生产的传感器,期望提供可以以低成本制造的vcsel阵列。由于制造成本与芯片面积成比例,因此期望提供密集型封装的vcsel阵列。

4.us 2020/0144792 a1披露了一种小间距vcsel阵列。提供了具有小尺寸和小间距的垂直腔表面发射激光器(vcsel)和vcsel阵列。描述了用于减少由vcsel结构所消耗的面积的方法以使得可以获得更高密度的vcsel器件。如us 2020/0144792 a1中所描述的,所提出的vcsel阵列包括:多个vcsel元件,每个vcsel元件包括:氧化物孔;台面,该台面同心地环绕氧化物孔,该台面包括圆形台面部分和台面接片,台面接片从圆形台面部分向外延伸,其中欧姆金属被提供在台面接片上;以及氮化物通孔,其中氮化物通孔定位在台面接片上,其中相邻vcsel元件具有重叠的台面接片。

技术实现要素:

5.本发明的目的是提供一种进一步改进的vcsel阵列。特别地,提供适于以低成本、高良率地大规模生产的vcsel阵列将是有利的。期望提供可以以低成本、高良率地制造同时提供高器件可靠性的vcsel阵列。

6.根据本披露内容的第一方面,提出了一种包括垂直腔表面发射激光器vcsel阵列的半导体器件。该半导体器件包括:第一vcsel,该第一vcsel具有第一有源区域;第二vcsel,该第二vcsel具有第二有源区域;其中,该第一vcsel的第一有源区域和该第二vcsel的第二有源区域沿第一晶轴布置;以及阻挡结构,该阻挡结构布置在该第一vcsel与该第二vcsel之间,其中,该阻挡结构适于阻挡缺陷沿该第一晶轴在该第一vcsel与该第二vcsel之间传播。桥可以连接该第一vcsel和该第二vcsel。该阻挡结构可以特别适于阻挡缺陷沿第一晶轴在第一vcsel的有源区域与第二vcsel的有源区域之间的传播。

7.在本披露内容的另一方面中,提出了一种用于制造包括垂直腔表面发射激光器vcsel阵列的半导体器件的方法。该方法包括以下步骤:提供半导体裸片(die),该半导体裸片包括适于制造vcsel的垂直层堆叠体;确定该半导体裸片的在平行于该半导体裸片表面且垂直于该垂直层堆叠体的方向上的晶轴;将该半导体裸片加工成半导体器件,该半导体

器件包括:第一vcsel,该第一vcsel具有第一有源区域;第二vcsel,该第二vcsel具有第二有源区域;其中,该第一vcsel的第一有源区域和该第二vcsel的第二有源区域沿第一晶轴布置;以及阻挡结构,该阻挡结构布置在该第一vcsel与该第二vcsel之间,其中,该阻挡结构适于阻挡缺陷沿该第一晶轴在该第一vcsel(的有源区域)与该第二vcsel(的有源区域)之间传播。

8.在下文中描述本发明的优选实施例。应当理解,所要求保护的方法可以具有与所要求保护的半导体器件类似和/或相同的优选实施例、特别是如本文所披露的优选实施例。

9.本文提出的解决方案可以提供一种可能性,即提供进一步改进的vcsel阵列,该阵列可以以低成本、高良率地制造,同时提供高器件可靠性。

10.发明人认识到,在密集型封装的vcsel阵列中、特别是在具有20至30μm或更小的超低间距的密集型封装的vcsel阵列中,存在若干台面可能遭受出现缺陷的风险。作为一种特点,发明人认识到这样的缺陷可能会影响相邻vcsel。虽然在某些应用中可以容忍有限数量的单独vcsel的缺陷,但是由于不均匀的亮度图案,几个相邻vcsel的缺陷可能会被视为器件故障。

11.发明人认识到沿晶轴布置的相邻vcsel遭受多台面缺陷的概率高于未沿晶轴布置的相邻vcsel。因此,本发明基于提供想法、具体地提供布置在相邻的第一vcsel与第二vcsel之间的阻挡结构的想法,该阻挡结构适于阻挡缺陷沿第一晶轴在第一vcsel(的有源区域)与第二vcsel(的有源区域)之间传播。第一vcsel、阻挡结构和第二vcsel因此可以如此沿晶轴从前往后依次布置,使得阻挡结构保护第二vcsel免受源自第一vcsel的可能以较高概率沿晶轴传播的缺陷的影响。连接第一vcsel和第二vcsel的桥仍然可以沿着与沿晶轴的直线不重合的路径被提供。因此,只利用部分蚀刻区域和相邻vcsel之间的剩余桥,就可以实现具有小间距的非常密集的封装。

12.第一vcsel和第二vcsel通过桥(也称为脊或网)连接的特征意味着发射器周围的材料没有被完全去除,即,第一vcsel和第二vcsel不是作为独立台面提供的,因为这不允许实现密集型封装的阵列。例如,发射器周围的材料将不会被完全去除,可以仅蚀刻发射器周围的例如四个区域,并且一方面用于氧化,并鉴于这些区域有利地有目的性地关于晶轴对齐将其用作阻挡结构。因此,可以实现在制造中的有利的协同效果。第一vcsel和第二vcsel可以至少部分地共享共同的顶面接触部。第一vcsel和第二个vcsel是相邻vcsel;特别是最接近彼此的相邻vcsel,特别是在第一晶轴的方向上。如本文所使用的,vcsel的有源区域是指vcsel的适于在操作期间发射光的区域,通常是vcsel的中心部分。

13.发明人认识到,为了进一步缩小vcsel阵列的间距,一种显而易见的想法可以是将氧化沟槽放置在vcsel阵列的网格的行和列的角落上。由此可以提供甚至更加紧凑的设计。小芯片尺寸允许每个晶圆上有更多芯片,并且更小的芯片可以放置在更小的封装中,从而降低芯片和封装的总体成本。

14.然而,已经发现,利用如本文所描述的阻挡结构的具体布置来减少多台面缺陷的有利影响可以提高产品良率,其方式为,一些增加的芯片面积和因此更高的制造成本可以被更高的制造良率超额补偿。此外,可以减少在单独的vcsel发生故障的情况下依赖多个附加的备用vcsel来提供冗余。这进一步缩小了所需的器件面积,并可以进一步有助于降低功耗。

15.vcsel阵列可以是如下的阵列、特别是密集型封装的阵列,该阵列具有不超过30μm、特别是不超过20μm、特别是不超过17.5μm、特别是不超过15μm、特别是不超过10μm的间距。如本文所使用的,术语“间距”可以指相邻vcsel的(最短)中心间距离。所提出的解决方案因为在小的间距下是特别有利的,因为将台面完全分隔开和提供分离的电连接不再可行。此外,出现多台面缺陷的风险随着vcsel密度的增加而增加。

16.该阻挡结构在垂直于该第一晶轴的方向上的宽度(或长度)可以宽于第一有源区域和/或第二有源区域在垂直于该第一晶轴的方向上的宽度。例如,如果阻挡结构作为沿第一晶轴的相邻vcsel之间的沟槽提供,则该沟槽可以比有源区域的直径更宽。鉴于该取向,阻挡结构在垂直于第一晶轴的方向上的宽度可以指沟槽的长度。如本文所使用的,垂直于晶轴意味着垂直于晶轴但平行于半导体裸片的顶表面。第一有源区域、阻挡结构和第二有源区域可以相对于第一晶轴居中,使得比第一有源区域更宽的阻挡结构阻隔源自第一有源区域并沿第一晶轴传播的缺陷到达第二有源区域。

17.该阻挡结构在平行于该第一晶轴的方向上的宽度(或厚度)可以小于该vcsel间距的30%、特别是小于该vcsel间距的20%、特别是小于该vcsel间距的10%、特别是小于该vcsel间距的5%。另外或替代性地,阻挡结构在平行于第一晶轴的方向上的宽度可以小于10μm、特别是小于5μm、特别是小于3μm、特别是小于2μm。因此,即使是相当窄的沟槽或阻挡结构也可以有效地减少多台面缺陷。鉴于该取向,阻挡结构在平行于第一晶轴的方向上的宽度可以指沟槽的宽度。例如,沟槽或其他阻挡结构可以为3μm宽和10μm长。如本文所使用的,平行于晶轴是指平行于晶轴且平行于半导体裸片的顶表面。

18.如以上已经指出的,阻挡结构可以包括蚀刻区域或由蚀刻区域形成。特别地,阻挡结构可以包括用于氧化的沟槽、特别是用于氧化第一vcsel和/或第二vcsel的相应氧化物孔的沟槽或由这样的沟槽形成。该实施例的优点是协同效果,因为阻挡结构的形成和氧化物孔的形成可以同时进行。

19.应当理解,该蚀刻区域的深度可以超过该第一vcsel和/或该第二vcsel的有源层的深度。因此,可以大幅降低具有缺陷传播的风险。

20.该蚀刻区域可以与该第一vcsel和/或该第二vcsel的顶面接触部分隔开。特别地,阻挡结构可以包括部分蚀刻区域,该部分蚀刻区域可以与第一vcsel的有源区域周围的顶面接触部分隔开。该顶面接触部可以是p型接触部或n型接触部。

21.连接该第一vcsel和该第二vcsel的桥可以有利地围绕该阻挡结构的一侧弯曲。因此,桥优选地不在第一vcsel与第二vcsel之间建立与第一晶轴或可选地与任何晶轴重合的路径。在进一步的改进方案中,可以提供连接该第一vcsel和该第二vcsel的第二桥,该第二桥围绕该阻挡结构的不同于该第一侧的第二侧弯曲。该实施例的优点是需要去除的材料更少并且可以提供附加的结构支撑。

22.连接该第一vcsel和该第二vcsel的桥可选地可以是连接该第一vcsel、该第二vcsel和相邻的第三vcsel的桥。在进一步的改进方案中,该桥还可以连接相邻的第四vcsel。如本文所使用的,连接vcsel是指直接连接vcsel,即,不经由中间的另外的vcsel或其部分。

23.再次参考器件几何形状,第一vcsel与第二vcsel之间的距离可以小于第一有源区域和/或第二有源区域的直径。这进一步突出了提供密集型封装的阵列的方面,其中,阵列

的vcsel非常接近彼此。相邻vcsel之间的距离可以指布置在第一vcsel与第二vcsel之间的阻挡结构的宽度。

24.阵列的第一vcsel和第二vcsel可以具有共同的电的顶面接触部和/或共同的电的底面接触部。该顶面接触部可以是p型接触部。该底面接触部可以是n型接触部。或反之亦然。可选地,可以提供环绕第一vcsel的有源区域的第一顶面接触部分和环绕第二vcsel的有源区域的第二顶面接触部分。第一顶面接触部分和第二顶面接触部分可以经由围绕阻挡结构的第一侧的第一旁路接触部并经由围绕阻挡结构的第二侧的第二旁路接触部连接。如此可以提供相邻vcsel之间的不同电通路。这种旁路接触部可以指在两侧紧邻并绕过阻挡结构的电连接。

25.半导体器件的vcsel阵列当然可以提供超过两个vcsel。该半导体器件可以进一步包括具有第三有源区域的第三vcsel。可以提供连接第一vcsel和第三vcsel的第二桥。该第一vcsel的第一有源区域和该第三vcsel的第三有源区域可以沿第二晶轴布置。第二阻挡结构可以布置在第一vcsel与第三vcsel之间。该阻挡结构可以适于阻挡缺陷沿第二晶轴在第一vcsel(的有源区域)与第三vcsel(的有源区域)之间传播。这进一步减少了多台面缺陷。第一晶轴可以与第二晶轴相交成45

°

和135

°

之间、特别是60

°

和120

°

之间、特别是75

°

和105

°

之间、特别是85

°

和95

°

之间的角度。

26.该第一vcsel可以具有矩形的、特别是正方形的有源区域,并且其中,阻挡结构提供在该有源区域的每一侧。例如,可以在有源区域周围提供四个阻挡结构,在每侧各一个。这有效地保护vcsel免受外部缺陷的影响并同时保护了相邻的vcsel。

27.半导体器件可以包括在矩形网格上、特别是在正方形网格上以行和列布置的多个vcsel。在网格上的每对相邻vcsel之间提供单独的阻挡结构。每个阻挡结构可以适于阻挡缺陷在对应的一对相邻vcsel之间传播。网格的行可以与第一晶轴对齐。沿着行的阻挡结构可以适于阻挡缺陷在沿着相应行的相邻vcsel之间传播。网格的列可以与不同于第一晶轴的第二晶轴对齐。沿着列的阻挡结构可以适于阻挡缺陷在沿着相应列的相邻vcsel之间传播。

28.应当理解,在不脱离本发明的范围的情况下,上文提及的特征和下文将要解释的特征不仅可以以分别指出的组合来使用,还可以以其他组合或单独使用。

附图说明

29.本发明的这些和其他方面将从下文中描述的(多个)实施例中变得明显并参考下文中描述的(多个)实施例被阐明。在以下附图中:

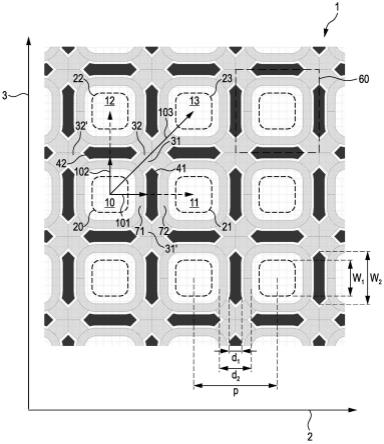

30.图1示出了根据本披露内容的一方面的包括垂直腔表面发射激光器vcsel阵列的半导体器件的实施例的示意图;

31.图2示出了根据本披露内容的一方面的示例性半导体器件的图像;

32.图3a至图3l展示了制造过程的不同加工步骤;

33.图4a至图4d示出了根据本披露内容的一方面的示例性半导体器件的测量结果;

34.图5示出了缺陷传播的示意图;

35.图6示出了根据本发明的一方面的方法的流程图。

具体实施方式

36.图1示出了包括垂直腔表面发射激光器(vcsel)阵列的半导体器件的实施例的示意图。该系统在其中整体用附图标记1表示。半导体器件的第一晶轴用附图标记2表示。可选的第二晶轴用附图标记3表示。在给定示例中,第一晶轴和第二晶轴可以相交成90

°

角。半导体器件1包括具有第一有源区域20的第一vcsel 10和具有第二有源区域21的第二vcsel 11。提供连接第一vcsel 10和第二vcsel 11的桥31、31’。该桥可以是半导体材料的未蚀刻部分。第一vcsel 10的第一有源区域20和第二vcsel 11的第二有源区域21沿第一晶轴2布置在彼此之后。在第一vcsel 10与第二vcsel 11之间、特别是在第一有源区域20与第二有源区域21之间布置有阻挡结构41,该阻挡结构在此呈沟槽形式。阻挡结构适于阻挡缺陷101沿第一晶轴2在第一vcsel 10与第二vcsel 11之间传播。这在图1中用箭头101示例性地展示,该箭头被作为阻挡结构41的沟槽阻挡。

37.半导体器件1可以可选地包括另外的vcsel,如图1中示例性地展示的。与上述类似地,可以提供具有第三有源区域22的第三vcsel 12。第二桥32、32’连接第一vcsel 10与第三vcsel 12。第一vcsel 10的第一有源区域20和第三vcsel 12的第三有源区域22沿第二晶轴2布置。第二阻挡结构42布置在第一vcsel 10与第三vcsel 12之间,其中,该阻挡结构适于阻挡缺陷102沿第二晶轴2在第一vcsel 10与第三vcsel 12之间传播。这在图1中用箭头102示例性地展示,该箭头被作为阻挡结构42的沟槽阻挡。应当注意,在第一vcsel 10与相对于第一vcsel 10对角布置的第四vcsel 13之间没有提供阻挡结构。然而,缺陷沿箭头103传播的概率是有限的,因此即使对于密集型封装的阵列也可以容忍该路径。此外,由于对角路径长度较长,因此源自第一vcsel 10的缺陷无法到达第二vcsel 20的概率较高。

38.换句话说,如果一个发射器中可能存在缺陷,则该缺陷在大多数情况下将沿着晶轴2、3之一传播。在此方向上布置的阻挡结构(在此作为蚀刻区域提供)将阻止缺陷传播。这将显著降低出现多台面故障的风险。因此,可以进一步提高器件可靠性以及制造良率。

39.有利地,半导体器件1可以包括若干单位单元60,这些单位单元可以灵活组合以提供具有期望的尺寸和形状的vcsel阵列。vcsel阵列的行数和/或列数可以根据需要灵活调整。

40.关于示例性几何尺寸,vcsel阵列可以是间距在8到30μm之间(例如,16μm)的密集型封装的阵列。具有宽度d1的窄沟槽可以作为阻挡结构提供。阻挡结构在平行于第一晶轴2的方向上的宽度d1可以小于vcsel间距p的30%、特别是小于vcsel间距的20%、特别是小于vcsel间距的10%、特别是小于vcsel间距的5%。在给定的示例中,沟槽可以约为3μm窄。另一方面,阻挡结构31在垂直于第一晶轴2的方向上的宽度w2优选地宽于第一有源区域20和/或第二有源区域21在垂直于第一晶轴2的方向上的宽度w1。因此,可以有效地防止源自两个有源区域之一的任何缺陷到达相应的另一个有源区域。例如,有源区域的宽度w1可以在3μm到20μm之间。阻挡结构的宽度w2通常可以至少约为10μm。然而,对于有源区域宽度超过10μm,阻挡结构的宽度可以相应增加。相邻vcsel的顶面接触部的内边缘之间的距离d2可以至少为5μm、特别是至少为8μm,使得具有足够的空间在其间形成阻挡结构。然而,作为上限,距离d2可以小于20μm、特别是小于15μm。这允许提供紧凑的阵列。在图1所示的示例中,第一vcsel 10与第二vcsel 11之间的中心间距离可以约为16μm。沿该短距离的缺陷传播被阻挡结构有效阻挡。在实施例中,阻挡结构可以布置在连接第一vcsl 10的中心和第二vcsel 11

的中心的线的中心处。在图1所示的示例中,第一vcsel 10与第四vcsel 13之间(即,沿对角线103)的中心间距离可以约为22.8μm。

41.如图1所示,连接第一vcsel 10和第二vcsel 11的桥31可以围绕阻挡结构41的上侧弯曲。因此,在绕过沿晶轴2的直接路径的同时建立了共同的电连接。可选地,连接第一vcsel 10和第二vcsel 11的第二桥31’可以围绕阻挡结构41的下侧弯曲。这些桥可以由多个相邻vcsel共享。如图1所示,连接第一vcsel 10和第二vcsel 11的桥31也可以连接到相邻的第三vcsel 12并且优选地还连接到相邻的第四vcsel 13。虽然示出了不同的附图标记31和32,但是这将被理解为在至少三个相邻vcsel之间共享的共同的桥结构。

42.图2示出了根据本披露内容的一方面的示例性半导体器件1的图像。在给定的示例中提供了12个vcsel,这些vcsel以如下方式提供:两行四个vcsel,然后是两行两个vcsel。第一vcsel 10和第二vcsel 11再次被阻挡结构31分隔开,该阻挡结构适于阻挡缺陷沿第一晶轴在第一vcsel 10与第二vcsel 12之间传播,该第一晶轴与第一vcsel 10和第二vcsel 11的有源区域的相应中心对齐。可以在顶表面上看到用于为vcsel提供第一电接触部的键合焊盘201。背面电极(未示出)可以用作第二电接触部。可选地,可以在表面上示出生产标记202。下文将参考图4进一步解释有关该器件的附加细节。

43.图3a至图3l展示了制造过程的不同加工步骤。未完成的半导体器件由附图标记1’表示。如图3a所展示的,在第一步骤中提供了半导体裸片300,该半导体裸片包括适于制造vcsel的垂直层堆叠体。半导体裸片被布置成使得在制造期间裸片的在平行于半导体裸片表面并且垂直于垂直层堆叠体的方向上的裸片晶轴2与相邻vcsel的有源区域对齐。图3b示出了利用如图3b’所示的掩模301’进行p接触部光刻301的步骤。图3c示出了p接触部302沉积的步骤。图3d示出了sinx沉积层303的步骤。图3e示出了利用如图3e’所示的掩模305进行光刻304以实现台面蚀刻的步骤。图3f示出了进行台面干法蚀刻以形成沟槽306的步骤,这些沟槽一方面可以用作氧化沟槽以便提供如图3g所示的氧化物孔306,但是也可以用作沿晶轴2方向的相邻vcsel的有源区域之间的阻挡结构。图3h示出了sinx沉积层308的步骤。图3i示出了通孔蚀刻光刻和晶种层309沉积的结果。图3j展示了用于实现镀金的光刻310。图3k展示了镀金311的步骤。图3l最终展示了在诸如晶种层去除、sinx中的沟道(street)蚀刻、弓形补偿层去除和晶圆打薄、背面n型接触部和弓形补偿金属沉积和退火等附加步骤之后的结果。背面接触部用附图标记322表示。图3l中的第一vcsel 11和第二vcsel 12现在被阻挡结构41分隔开。因此可以有效地防止图3l中的第一vcsel 11的有源区域21中的缺陷沿第一晶轴2的方向传播到相邻的第二vcsel。

44.再次参考图2并参考图4a至图4d,描述了示例性非限制性实施例。呈现了用于实现高光学输出功率的具有12个发射器的发射940nm的vcsel阵列。输出特性可以适于表现出光谱单模行为以及高斯形状的远场轮廓。密集型封装的发射器设计每mm2可以测量多达3850个发射器,并易于扩展以用于高功率应用。示例性垂直腔表面发射激光器(vcsel)的基本结构允许密集型封装的多发射器阵列以实现高的光学输出功率。如以上所指出的,可以提供氧化的940nm单模发射vcsel阵列,该阵列具有12个输出面和稳定的高斯远场射束轮廓以用于各种驱动条件和温度。在短脉冲条件下高达300mw(每个发射器》25mw)的峰值单模输出功率可以得到证实。有利地,出色的器件可靠性允许广泛的温度范围下的工业飞行时间(tof)应用。

45.在实施例中,可以提供基于gaas的外延层结构,该外延层结构包括gaasp有源区域以实现紫外940nm输出特性,以使用氧化物限制来保持光谱单模行为。芯片设计如图2所描绘的,其中12个发射窗口作为镀金的电的顶面接触部中的开口清晰可见,该顶面接触部包括图片中左下方的键合焊盘201,其示例性切割芯片尺寸为187

×

187μm。芯片背面可以经历晶圆打薄和镀金并用作电的底面接触部(参见图3l中的322)。

46.示例性vcsel阵列芯片的光-电流-电压(light

–

current

–

voltage,liv)测量在图4a中示出。可以看出,在高于30ma的电流下,尚未达到输出功率的热翻转(thermal roll-over)。50℃时的斜率效率为0.90w/a,其中阈值电流在3ma到6ma之间,取决于环境温度。与使用外延再生长的具有相似光学孔径的单模vcsel相比,氧化的12发射器vcsel阵列的光学输出功率甚至可以更高。如多结vcsel的高功率概念需要更高的正向电压,并且不提供单模发射。

47.如图4b所示,使用ns范围内的短脉冲条件,峰值输出功率可以增加到高于300mw(每个发射器》25mw),同时在室温下保持0.75w/a的斜率效率。通过按比例放大到具有相同发射器单位面积密度的更大芯片,甚至可以进一步增加输出功率。对于0.97mm2的芯片尺寸和2352个发射器,通过使用具有200μs脉冲宽度和10%占空比的脉冲操作可以达到大约1w/a的斜率效率。这可以在5a的电流下产生4w的输出功率。

48.如图4c所示,12发射器vcsel阵列的光谱测量可以在75℃温度下表现出单模行为,其中fwhm带宽为300ghz,峰值波长约为937nm。预计随着光谱分辨率的提高可以出现每个发射器的窄带宽光谱。如右侧的图4d的图片所表明的,所有发射器的干涉可以产生高斯形状的远场特性。在给定的示例中,50℃下的发散角约为17

°

,在25和105℃的范围内具有仅为-0.015

°

/℃的小的温度漂移。应当注意,即使是在ns范围内的短脉冲操作模式下,横向模式行为也可以恒定地保持高斯形状。

49.对实施所提出的解决方案的一组示例性器件的可靠性测量示出了卓越的结果。在连续波操作的测试时间达到3300小时后,在低于32.5ma电流和120℃的条件下没有出现故障。在如40ma、120℃和25ma、150℃的更极端条件下进行测试时,仅在600小时和1200小时后分别发生首次故障。对在如25ma和105℃的压力使用条件下出现1%故障的时间的计算提供了超过16000小时的器件寿命,从而为高功率单模器件创造了基准。特别地,多台面缺陷可以大幅减少。这在可以容忍单个vcsel故障的应用场景中特别有利。

50.因此,图2中展示并参考图4a至图4d的实验结果描述的示例性器件提供了单模vcsel阵列,该阵列具有12个顶面发射器,以在低正向电压下在30ma时实现高达25mw的高单模光学输出功率,而不会发生热翻转。通过利用短脉冲使器件实现每个发射器高达25mw或按比例放大密集型封装的发射器面积,可以进一步增加输出功率,从而可以实现瓦特范围内的功率值。即使在短脉冲条件下,该12发射器器件也以低发散角而不具有更高的横向模式令人信服。该器件极佳的可靠性特性符合长寿命工业应用的要求。

51.参考图5,阻挡结构的厚度可以可选地基于缺陷从第一vcsel 10传播到第二vcsel 11的有源区域的概率而变化。多组箭头501和502展示了一些潜在的传播路径。对于源自第一vcsel 10的上边缘的缺陷,阻挡结构41的顶端处的窄尖端可能就足够了,因为缺陷撞击阻挡结构的这部分的概率是有限的。然而,朝向阻挡结构41的中心部分可以实施更宽的阻挡区域,因为缺陷到达阻挡结构的这部分的概率更高。

52.图6示出了根据本发明的一方面的方法600的流程图。在第一步骤s601中,提供半导体裸片,该半导体裸片包括适于制造vcsel的垂直层堆叠体。在第二步骤s602中,确定半导体裸片的在平行于半导体裸片表面并且垂直于垂直层堆叠体的方向上的晶轴。在第三步骤s603中,诸如例如参考图3a至图3l所描述的那样将半导体裸片加工成半导体器件,该半导体器件包括:第一vcsel,该第一vcsel具有第一有源区域;第二vcsel,该第二vcsel具有第二有源区域;其中,该第一vcsel的第一有源区域和该第二vcsel的第二有源区域沿第一晶轴布置;以及阻挡结构,该阻挡结构布置在该第一vcsel与该第二vcsel之间,其中,该阻挡结构适于阻挡缺陷沿该第一晶轴在该第一vcsel与该第二vcsel之间传播。

53.虽然已经在附图和前述说明中详细展示和描述了本发明,但是这种展示和说明被认为是展示性的或示例性的而不是限制性的;本发明不限于所披露的实施例。从对附图、披露内容和所附权利要求的研究中,本领域技术人员在实施要求保护的发明时可以理解和实现对所披露的实施例的其他变化。

54.在权利要求中,词语“包括”不排除其他元件或步骤,并且不定冠词“一个”或“一种”并不排除多个。单个元件或其他单元可以实现权利要求中列举的几项的功能。在彼此不同的从属权利要求中列举某些措施的简单事实并不表明这些措施的组合不能被有利地使用。

55.计算机程序可以存储/分布在合适的非暂态介质(诸如与其他硬件一起提供或作为其他硬件的一部分提供的光学存储介质或固态介质)上,但是也可以以其他形式(诸如经由互联网或其他有线或无线电信系统)分布。

56.权利要求中的任何附图标记不应被解释为限制范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1