一种改善丘状凸起缺陷的工艺方法与流程

1.本发明涉及半导体技术领域,特别是涉及一种改善丘状凸起缺陷的工艺方法。

背景技术:

2.随着集成电路制造工艺的发展以及关键尺寸的缩小,很多新的方法被运用到器件制造工艺中,用以改善器件性能,氮化硅因其有着良好的刻蚀选择性、良好的铜粘附性以及良好的阻挡铜在界面间的扩散等性质而被广泛应用。

3.目前为止的报道中,研究者们认为只有增加氮化硅对铜表面的粘附性才能更好地压制铜在界面间的扩散,从而大都着眼于铜cmp之后增加预处理步骤用来去掉由于铜裸露造成的氧化铜层,从而减小界面间的接触电阻并且防止铜在界面间的扩散现象,现行的65/55/40/28/22nm等工艺节点中顶层铜cmp之后都会沉积氮化硅薄膜作为刻蚀阻挡层,而在氮化硅薄膜沉积之后不可避免的都会出现大量丘状(hillock)缺陷,本质上,hillock缺陷造成的机理是由于为了满足更低的介电层造成的容抗,而采用了包裹铜的低介电常数的介电层,而低介电常数的介电层往往都有较为疏松的特性,疏松的介电层带来的副作用便是在高温或者其他外部因素下难以压制铜线的溢出而造成了hillock缺陷,随着工艺节点逐渐向下,到40nm节点铜hillock缺陷越发严重达到250000颗以上,而铜hillock缺陷一直存在着角落区比较薄弱的铜渗透现象,而铜渗透现象在工艺节点逐渐向下时由于铜线与铜线的距离变得越来越短,从而所表现出的造成电流击穿的风险会越来越大。

技术实现要素:

4.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种改善丘状凸起缺陷的工艺方法,用于解决现有技术中铜cmp后形成的丘状缺陷导致电流击穿的风险增大的问题。

5.为实现上述目的及其他相关目的,本发明提供一种改善丘状凸起缺陷的工艺方法,至少包括:

6.步骤一、提供表面由铜和介电质结构组成的半导体器件平面;

7.步骤二、在所述半导体器件平面沉积厚度为50~200埃、350℃工艺的第一氮化硅层作为铜溢出阻挡层;

8.步骤三、对所述半导体器件平面进行退火预处理,增加所述铜溢出阻挡层与所述半导体器件平面中的铜表面的粘附性;

9.步骤四、在退火后的所述第一氮化硅层表面沉积第二氮化硅层,沉积工艺的温度为400℃。

10.优选地,步骤二中的所述沉积所述第一氮化硅层的方法为:在1-5torr的压力下,通入氮气流量为1000~10000sccm,通入硅烷流量100~1000sccm,通入氨气流量100~1000sccm,温度为350℃的环境下进行等离子体处理。

11.优选地,步骤二中所述等离子体处理的高频射频为100~1000瓦特。

12.优选地,步骤二中所述等离子体处理的持续时间为1~20秒。

13.优选地,步骤三中进行退火预处理的工艺为炉管工艺,退火温度为350℃。

14.优选地,步骤三中进行退火预处理的退火时间为30~60分钟。

15.优选地,步骤三的所述退火预处理的作用是防止步骤四中沉积所述第二氮化硅层后造成丘状凸起的缺陷。

16.优选地,该方法应用于65nm、55nm、40nm、28nm以及22nm技术节点的工艺方法中。

17.如上所述,本发明的改善丘状凸起缺陷的工艺方法,具有以下有益效果:本发明通过对铜cmp之后增加低温350℃工艺的氮化硅薄膜以及350℃低温炉管工艺的方式大大改善铜表面受400℃氮化硅工艺影响挤压造成的丘状凸起缺陷。

附图说明

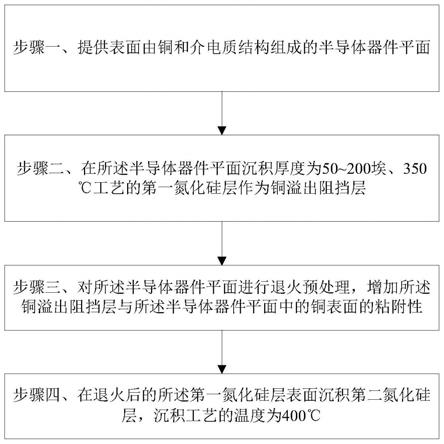

18.图1显示为本发明改善丘状凸起缺陷的工艺方法流程图。

具体实施方式

19.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

20.请参阅图1。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

21.本发明提供一种改善丘状凸起缺陷的工艺方法,至少包括:

22.步骤一、提供表面由铜和介电质结构组成的半导体器件平面;

23.步骤二、在所述半导体器件平面沉积厚度为50~200埃、350℃工艺的第一氮化硅层作为铜溢出阻挡层;

24.本发明进一步地,本实施例的步骤二中的所述沉积所述第一氮化硅层的方法为:在1-5torr的压力下,通入氮气流量为1000~10000sccm,通入硅烷流量100~1000sccm,通入氨气流量100~1000sccm,温度为350℃的环境下进行等离子体处理。

25.本发明进一步地,本实施例的步骤二中所述等离子体处理的高频射频为100~1000瓦特。

26.本发明进一步地,本实施例的步骤二中所述等离子体处理的持续时间为1~20秒。

27.步骤二中在此铜与介电质结构的平面沉积厚度为50~200埃的350摄氏度工艺的氮化硅作为铜溢出阻挡层,其制作工艺细节包含但不限定为:在1-5torr(托,真空压强单位)的压力下,通入氮气流量约为1000~10000sccm(standard cubic centimeter per minute,每分钟立方厘米),通入硅烷流量100~1000sccm,通入氨气流量100~1000sccm,温度约为350℃的环境下进行等离子体处理,其高频射频约为100~1000瓦特,持续时间约为1~20秒(以满足实际所需厚度设定时间)。

28.步骤三、对所述半导体器件平面进行退火预处理,增加所述铜溢出阻挡层与所述半导体器件平面中的铜表面的粘附性;在铜溢出阻挡层后做350摄氏度炉管工艺30~60分

钟用来使铜溢出阻挡层的氮化硅与铜表面具有更好地粘附性起到铜表面稳定作用。

29.本发明进一步地,本实施例的步骤三中进行退火预处理的工艺为炉管工艺,退火温度为350℃。

30.本发明进一步地,本实施例的步骤三中进行退火预处理的退火时间为30~60分钟。

31.本发明进一步地,本实施例的步骤三的所述退火预处理的作用是防止步骤四中沉积所述第二氮化硅层后造成丘状凸起的缺陷。

32.步骤四、在退火后的所述第一氮化硅层表面沉积第二氮化硅层,沉积工艺的温度为400℃。

33.本发明进一步地,本实施例的该方法应用于65nm、55nm、40nm、28nm以及22nm技术节点的工艺方法中。

34.本发明是在氮化硅沉积前增加了几种前处理步骤,经过预沉积350摄氏度工艺氮化硅薄膜后将铜hillock缺陷从基础水准250000颗以上降低到1001颗,再经过350摄氏度退火预处理后可将hillock defect降至0颗,效果明显。

35.综上所述,本发明通过对铜cmp之后增加低温350℃工艺的氮化硅薄膜以及350℃低温炉管工艺的方式大大改善铜表面受400℃氮化硅工艺影响挤压造成的丘状凸起缺陷。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

36.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1