一种驱动背板、显示面板及驱动背板的制造方法与流程

1.本发明涉及显示技术领域,尤其涉及一种驱动背板、显示面板及驱动背板的制造方法。

背景技术:

2.近年来,ar(augmented reality,增强现实)和vr(virtual reality)高ppi(每英寸像素数)产品在显示行业备受关注。但是,高ppi产品由于金属布线密度增加等原因,ar、vr产品的开口率和透过率相比常规产品,会大大降低。为了提高ar、vr产品的开口率和透过率,需要通过更加复杂的工艺制程来实现,比如说使用ltpo(low temperature polycrystalline oxide,低温多晶氧化物)技术。但是,ltpo技术由于整合了ltps(low temperature poly-silicon,低温多晶硅)和oxide(氧化物)两种tft(thin film transistor,薄膜场效应晶体管),制作过程工艺制程较多,进而导致生产成本增加。

3.因此,如何优化整合了ltps和oxide两种tft的显示面板的驱动基板的制造工艺成为了目前亟待解决的问题。

技术实现要素:

4.鉴于上述问题,本发明提出了一种驱动背板、显示面板及驱动背板的制造方法,可减少图形化掩膜的工艺步骤,实现了工艺优化,降低了工艺成本。

5.第一方面,本技术通过一实施例提供如下技术方案:

6.一种驱动背板,包括:

7.衬底基板;所述衬底基板包括第一区域和第二区域;低温多晶硅半导体层,设置在所述衬底基板的所述第一区域;氧化物半导体层,设置在所述衬底基板的所述第二区域;第一绝缘层,设置在所述低温多晶硅半导体层和所述氧化物半导体层远离所述衬底基板的一侧;穿透所述第一绝缘层的接触孔;所述接触孔包括:第一过孔和第二过孔,所述第一过孔延伸至所述低温多晶硅半导体层远离基板的一侧;所述第二过孔延伸至所述氧化物半导体层远离基板的一侧;所述氧化物半导体层对应于所述第二过孔的位置设置有连接孔;第一电极结构,设置在所述第一过孔中,并与所述低温多晶硅半导体层接触;以及第二电极结构,设置在所述第二过孔和所述连接孔中,并在所述连接孔中与所述氧化物半导体层形成侧面接触。

8.可选的,所述连接孔穿透所述氧化物半导体层。

9.可选的,还包括:

10.第一栅绝缘层,设置在所述低温多晶硅半导体层远离所述衬底基板的一侧;第一栅极、遮光结构,设置在所述第一栅绝缘层远离所述衬底基板的一侧;所述第一栅极位于所述第一区域,所述遮光结构位于所述第二区域;第二绝缘层,设置在所述第一栅极和遮光结构远离所述衬底基板的一侧;所述氧化物半导体层设置在所述第二绝缘层远离所述衬底基板的一侧;第二栅绝缘层,设置在所述氧化物半导体层远离所述衬底基板的一侧;以及第二

栅极,设置在所述第二栅绝缘层与所述第一绝缘层之间;其中,所述第一过孔还穿透所述第二绝缘层和所述第二栅绝缘层。

11.可选的,所述接触孔还包括:第三过孔,设置在所述遮光结构远离所述衬底基板一侧,所述第三过孔中设置有与所述遮光结构接触的第三电极结构;

12.所述驱动背板还包括:第三绝缘层,设置在所述第一电极结构、所述第二电极结构和所述第三电极结构远离所述衬底基板的一侧;所述第一绝缘层和所述第三绝缘层中设置有搭接过孔;在所述搭接过孔中设置有导电搭接结构,导电搭接结构分别与所述第三电极结构和所述第二栅极连接。

13.可选的,还包括:

14.缓冲层,设置在所述衬底基板和所述低温多晶硅半导体层之间;其中,所述低温多晶硅半导体层和所述氧化物半导体层设置在同一层。

15.第二方面,基于同一发明构思,本技术通过一实施例提供如下技术方案:

16.一种驱动背板的制造方法,包括:

17.在衬底基板第一区域形成低温多晶硅半导体层,以及第二区域形成氧化物半导体层;在所述低温多晶硅半导体层和所述氧化物半导体层远离所述衬底基板的一侧形成第一绝缘层;在所述第一绝缘层上覆盖图形化掩膜,并形成穿透所述第一绝缘层的接触孔;其中,所述接触孔包括:形成在所述低温多晶硅半导体层远离所述衬底基板一侧的第一过孔,以及形成在所述氧化物半导体层远离所述衬底基板一侧的第二过孔;在所述第一过孔中形成与所述低温多晶硅半导体层接触的第一电极结构,和在所述第二过孔中形成与所述氧化物半导体层接触的第二电极结构。

18.可选的,所述在所述第一过孔中形成与所述低温多晶硅半导体层接触的第一电极结构之前,还包括:

19.采用湿法刻蚀去除所述第一过孔底部的所述低温多晶硅半导体层表面的氧化层,并刻蚀所述第二过孔底部的氧化物半导体层形成连接孔;所述在所述第二过孔中形成与所述氧化物半导体层接触的第二电极结构,包括:在所述第二过孔和所述连接孔中形成第二电极结构,并使所述第二电极结构在所述连接孔中与所述氧化物半导体层形成侧面接触。

20.可选的,所述刻蚀所述第二过孔底部的氧化物半导体层形成连接孔,包括:

21.刻蚀并穿透所述第二过孔底部的氧化物半导体层,形成所述连接孔。

22.可选的,所述形成低温多晶硅半导体层之后,且形成氧化物半导体层之前,还包括:

23.在所述低温多晶硅半导体层远离所述衬底基板的一侧依次形成第一栅绝缘层、第一栅极、遮光结构和第二绝缘层;其中,所述第一栅极位于所述第一区域,所述遮光结构位于所述第二区域;所述形成氧化物半导体层包括:在所述第二绝缘层远离所述衬底基板一侧的第二区域形成所述氧化物半导体层;所述形成氧化物半导体层之后,且形成所述第一绝缘层之前,还包括:在所述氧化物半导体层上依次形成第二栅绝缘层和第二栅极。

24.可选的,所述接触孔还包括:形成在所述遮光结构远离所述衬底基板一侧的第三过孔;在形成所述第一电极结构和所述第二电极结构时,所述制造方法还包括:在所述第三过孔中形成与所述遮光结构接触的第三电极结构;在形成所述第一电极结构和所述第二电极结构之后,还包括:在所述第一电极结构、所述第二电极结构和所述第三电极结构上覆盖

第三绝缘层;刻蚀所述第三绝缘层和所述第一绝缘层,形成用于搭接所述第三电极结构和第二栅极的搭接过孔;在所述搭接过孔中形成搭接结构,以将所述第三电极结构和所述第二栅极电连接。

25.可选的,所述在衬底基板第一区域形成低温多晶硅半导体层,以及第二区域形成氧化物半导体层,包括:

26.在所述衬底基板的一侧形成缓冲层;在所述缓冲层远离所述衬底基板的一侧的所述第一区域形成低温多晶硅半导体层,以及所述第二区域形成氧化物半导体层;在形成所述低温多晶硅半导体层和所述氧化物半导体层之后,且形成所述第一绝缘层之前,还包括:在所述低温多晶硅半导体层和所述氧化物半导体层上依次形成第一栅绝缘层、第一栅极、第二栅极以及第二绝缘层;其中,所述第一栅极位于所述第一区域,所述第二栅极位于所述第二区域。

27.可选的,所述在所述第一绝缘层上形成接触孔,包括:

28.在含氧的气氛条件下干法刻蚀所述第一绝缘层,形成延伸至所述低温多晶硅半导体层的所述第一过孔,以及形成延伸至所述氧化物半导体层的所述第二过孔;在无氧的气氛条件下干法刻蚀掉所述第一过孔底部的所述低温多晶硅半导体层表面的氧化层。

29.第三方面,基于同一发明构思,本技术通过一实施例提供如下技术方案:

30.一种显示面板,其特征在于,包括前述第一方面中任一所述的驱动背板;或者包括由前述第二方面中任一所述的驱动背板的制造方法所制造的驱动背板。

31.在本发明实施例提供了一种驱动背板、显示面板及驱动背板的制造方法,其中,驱动背板及其制造方法,通过在衬底基板第一区域形成低温多晶硅半导体层,以及第二区域形成氧化物半导体层;在低温多晶硅半导体层和氧化物半导体层远离衬底基板的一侧形成第一绝缘层;在第一绝缘层上覆盖图形化掩膜,并在第一绝缘层上形成接触孔;其中,接触孔包括:形成在低温多晶硅半导体层远离衬底基板一侧的第一过孔,以及形成在氧化物半导体层远离衬底基板一侧的第二过孔;在第一过孔中形成与低温多晶硅半导体层接触的第一电极结构,和在第二过孔中形成与氧化物半导体层接触的第二电极结构。在本发明实施例的驱动背板制造时在形成第一过孔和第二过孔的工艺过程中,只需要使用一道图形化掩膜(mask),不需要第一过孔和第二过孔进行先后刻蚀,节省了工艺成本。

32.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

附图说明

33.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

34.图1~图6,和图10为本发明实施例中驱动背板的制造方法各步骤阶段对应的驱动背板结构示意图;

35.图7~图9为本发明实施例中驱动背板的层结构连接关系示意图;

36.图11~图18为本发明实施例中又一驱动背板的制造方法各步骤阶段对应的驱动背板结构示意图;

37.图19~图23为本发明实施例中又一驱动背板的制造方法各步骤阶段对应的驱动背板结构示意图;

38.图24~图26为本发明实施例中又一驱动背板的层结构连接关系示意图;

39.图27~图29为本发明实施例中又一驱动背板的制造方法各步骤阶段对应的驱动背板结构示意图;

40.图30为本发明实施例中一驱动背板的结构示意图;

41.图31为本发明实施例中又一驱动背板的结构示意图。

具体实施方式

42.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

43.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

44.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

45.请参阅图1,本发明中针对整合了ltps和oxide两种tft的显示面板的驱动背板,提供一种驱动背板的制造方法,在该制造方法中会在衬底基板11上依次形成缓冲层12、低温多晶硅半导体层121(p-si)、第一栅绝缘层13、第一栅极131、遮光结构132(light shielding,ls)、第一绝缘层14、氧化物半导体层141、第二栅绝缘层15、第二栅极151以及第二绝缘层16。其中,氧化物半导体层141在本实施实施例中可为铟镓锌氧化物(indium gallium zinc oxide,igzo),但不限于此。衬底基板11分为goa(gate driver on array,栅极行扫描驱动)区和pixel(像素)区,其中,低温多晶硅半导体层121和第一栅极131位于goa区,氧化物半导体层141、遮光结构132和第二栅极151位于pixel区。

46.接着,会在第二绝缘层16远离衬底基板11的一侧覆盖第一掩膜层(图中未示出),该第一掩膜层用于实现刻蚀形成低温多晶硅半导体层121对应的第一过孔1211,以及形成遮光结构132对应的第二过孔1321,如图2所示。进一步的,为了改善低温多晶硅半导体层121表面的接触电阻,同时避免boe etch(buffered oxide etch,缓冲氧化物刻蚀液)对损伤氧化物半导体层141;因此,在未开启氧化物半导体层141对应的过孔时,采用boe etch去除低温多晶硅半导体层121的过孔位置处的表面氧化物。此时,由于氧化物半导体层141对应的过孔未开启,从而可避免氧化物半导体层141产生损伤。

47.再接着,在第二绝缘层16远离衬底基板11的一侧覆盖第二掩膜层(图中未示出),

该第二掩膜层用于实现刻蚀形成氧化物半导体层141对应的第三过孔1411,以及形成第二栅极151对应的第四过孔1511,如图3所示。

48.再接着,在这些过孔中形成导电材料。在低温多晶硅半导体层121和氧化物半导体层141对应的过孔填充导电材料后形成对应的第一电极结构1212和第二电极结构1412;第一电极结构1212可作为低温多晶硅半导体层121的源/漏电极(sd),第二电极结构1412可作为氧化物半导体层141的源/漏电极。在第二栅极151和遮光结构132对应的过孔填充导电材料并形成搭接结构1322后,将第二栅极151和遮光结构132连接后作为氧化物半导体层141的双栅结构,如图4所示。

49.再接着,在第二绝缘层16远离衬底基板11的一侧覆盖第三绝缘层17,然后刻蚀第三绝缘层17和第二绝缘层16形成连接至氧化物半导体层141的第五过孔1413,如图5所示;在第五过孔1413中填充导电材料形成第三电极结构1414,第三电极结构1414从第五过孔1413中引出以连接像素结构的电极,如图6所示。

50.具体的,该驱动背板的部分结构关系可参见图7、8和9所示。其中,在图7中示出了goa区中的低温多晶硅半导体层121以及位于低温多晶硅半导体层121远离衬底基板11一侧的第一栅极131;低温多晶硅半导体层121的两端通过在第一过孔1211中设置的第一电极结构1212向远离衬底基板11的方向引出走线。在图8中,示出了pixel区中的氧化物半导体层141位于第二栅极151和遮光结构132之间;氧化物半导体层141的一端通过第三过孔1411中的第二电极向远离衬底基板11的方向引出,另一端通过第五过孔1413中的第三电极结构1414向远离衬底基板11的方向引出。在图9中,示出了pixel区中的遮光结构132和第二栅极151分别通过第二过孔1321中和第四过孔1511中的搭接结构1322向远离衬底基板11的方向引出并连接。

51.最后,在第二绝缘层16远离衬底基板11的一侧形成平坦层18和钝化层19;以便于后续继续制造对应的像素结构,例如,制造对应的像素电极181、公共电极191以及像素支撑192等,如图10所示。

52.在该种实现方式中,在形成低温多晶硅层和氧化物半导体层141各自对应的过孔时会使用到两道掩膜层,其中第一掩膜层用于形成低温多晶硅半导体层121对应的过孔,第二掩膜层用于形成氧化物半导体层141对应的过孔。因此整个工艺过程较为复杂,不利于制造成本的控制。

53.在本发明的又一实施例中还提供了另一种驱动背板的制造方法,可用于制造整合了ltps和oxide两种tft的显示面板的驱动背板;该驱动背板对应的像素区可以是单栅极结构,也可以是双栅极结构。在该制造方法中只用需要使用一道图形化掩膜工艺,即可刻蚀形成低温多晶硅半导体层和氧化物半导体层所对应的过孔,也即仅需要一道曝光工艺开启两类半导体结构对应的过孔,简化了制造工艺,可显著的降低制造成本。

54.进一步的,在制造过程中采用一道图形化掩膜工艺进行刻蚀虽然减少了工艺步骤,降低了生产成本。但是分析发现在过孔底部的氧化物半导体层存在一定的侵蚀损伤,该损伤会对造成一定接触不良,以及性能不稳定的缺陷。因此,在本技术中还需要解决如下技术问题:如何在采用一道图形化掩膜形成过孔的过程中避免对氧化物半导体层造成损伤。或者,在采用一道图形化掩膜形成过孔的过程中对氧化物半导体层造成损伤后,如何对造成损伤后的氧化物半导体层进行补救,以避免产生不稳定缺陷。

55.因此,在本发明后续实施例中还在一道图形化掩膜的情况下,采用了含氧气体刻蚀形成低温多晶硅半导体层和氧化物半导体层对应的过孔;接着,采用不含氧的气体刻蚀低温多晶硅半导体层表面的氧化层,以避免了氧化物半导体层的损伤。此外,本发明后续实施例中还针对仅使用一道图形化掩膜的情况下,对可能产生损伤的氧化物半导体层刻蚀至穿透;接着形成的电极以侧面接触的方式与氧化物半导体层连接,从而弥补氧化物半导体层损伤带来的接触不良等不稳定缺陷。下面通过具体示例进行进一步的说明。

56.1、针对单栅极结构的驱动背板而言:

57.首先,提供衬底基板21;该衬底基板21可以是玻璃基板;当然不限于此,也可以是其他常用的有机或无机衬底材料,例如柔性衬底基板21pi(polyimide,聚酰亚胺)。该衬底基板21可划分为第一区域bm和第二区域aa,如图11所示;可以理解的是,第一区域bm和第二区域aa中任一者为goa区,另一者为pixel区。在本实施例中以第一区域bm为goa区,第二区域aa为pixel区为例进行说明。

58.接着,在该衬底基板21上形成缓冲层22;再接着,在缓冲层22远离衬底基板21的一侧的第一区域bm形成低温多晶硅半导体层221,在缓冲层22远离衬底基板21的一侧的第二区域aa形成氧化物半导体层222,如图12所示。该低温多晶硅半导体层221和氧化物半导体层222可位于不同层,也可位于同一层;低温多晶硅半导体层221和氧化物半导体层222可制造在同一层,减少工艺步骤。可以理解的,低温多晶硅半导体层221和氧化物半导体层222均为图形化结构。

59.再接着,在低温多晶硅半导体层221和氧化物半导体层222远离衬底基板21的一侧依次形成第一栅绝缘层23,第一栅极231、第二栅极232和绝缘层,如图13所示。第一栅极231位于第一区域bm,用于作为低温多晶硅半导体层221的栅极,第二栅极232位于第二区域aa,用于作为氧化物半导体层222的栅极。第一栅绝缘层23可用于隔离第一栅极231与低温多晶硅半导体层221,以及用于隔离第二栅极232与氧化物半导体层222。进一步的,由于氧化物半导体层222对应的栅极为单栅极结构,本实施例中可将第一栅极231和第二栅极232可制造在同一层,减少工艺步骤。在一些实现方式中,绝缘层可包括第一绝缘层24和第二绝缘层25,第二绝缘层25形成在第一栅绝缘层23远离衬底基板21的一侧,并覆盖第一栅极231和第二栅极232,第一绝缘层24形成在第二绝缘层25远离衬底基板21的一侧。

60.再接着,由于需要在通过一道图形化掩膜形成低温多晶硅半导体层221和氧化物半导体层222对应的接触孔,可采用如下的工艺方法。

61.一种方式为保护氧化物半导体层222,避免工艺损坏氧化物半导体层222。方法如下:

62.首先,在第一绝缘层24上覆盖图形化掩膜(图中未示出),并在第一绝缘层24上形成接触孔;其中,接触孔包括:形成在低温多晶硅半导体层221远离衬底基板21一侧的第一过孔2211,以及形成在氧化物半导体层222远离衬底基板21一侧的第二过孔2221,如图14所示。可以理解的,第一过孔2211穿透第一绝缘层24和第二绝缘层25,其底部延伸至低温多晶硅半导体层221;同样的,第二过孔2221穿透第一绝缘层24和第二绝缘层25,其底部延伸至氧化物半导体层222。在一些可选的实现方式中,可在含氧的气氛条件下进行干法刻蚀第一绝缘层24,形成延伸至多晶硅半导体层的第一过孔2211,以及形成延伸至氧化物半导体层222的第二过孔2221。

63.其中,含氧的气氛条件可包括以下的任一种:

64.cf4和o2;sf6和o2;以及chf3和o2。

65.由于刻蚀接触孔的过程是在含氧的气氛条件下进行的,因此在低温多晶硅半导体层221上可能会形成氧化层。为了改善接触电阻,保证良好的电接触;接着,去除第一过孔2211底部的低温多晶硅半导体层221表面的氧化层。在一些可选的实现方式中,可在无氧的气氛条件下刻蚀掉第一过孔2211底部的低温多晶硅半导体层221表面的氧化层。

66.其中,无氧的气氛条件可包括以下的任一种:

67.cf4;sf6;chf3;cf4和ar;sf6和ar;chf3和ar。

68.通过上述干法刻蚀过程,通过含o2的气体在第一绝缘层24中刻蚀接触孔;接着,通过不含o2的气体去除低温多晶硅半导体层221表面的氧化层。可避免使用boe etch工艺,又能去掉低温多晶硅半导体层221表面的氧化层,从而也就避免了boe etch工艺过程对氧化物半导体层222的损伤。

69.再接着,在第一过孔2211中形成与低温多晶硅半导体层221接触的第一电极结构2212,和在第二过孔2221中形成与氧化物半导体层222接触的第二电极结构2222,如图15所示。由于,在前面的步骤中通过含氧和不含氧的两步干法刻蚀,清除了低温多晶硅半导体表面的氧化层,同时又避免了氧化物半导体层222的损伤;因此,第一电极结构2212可与低温多晶硅半导体层221在第一过孔2211的底部形成良好的电接触;第二电极结构2222也可与氧化物半导体层222在第二过孔2221的底部形成良好的电接触。

70.再接着,在第一绝缘层24远离衬底基板21的一侧覆盖第三绝缘层26,对第三绝缘层26进行刻蚀形成第三过孔2223;在第三过孔2223中形成第三电极结构2224以作为氧化物半导体层222的源/漏极引出,如图16所示。

71.另一种实现方式为不对氧化物半导体层222进行保护。方法如下:

72.首先,在第一绝缘层24上覆盖图形化掩膜,并在第一绝缘层24上形成接触孔;可采用现有的刻蚀工艺实现,不限制。接着,去除第一过孔2211底部的低温多晶硅半导体层221表面的氧化层,并刻蚀第二过孔2221底部的氧化物半导体层222形成连接孔2227。在一些实现方式中,可采用boe etch工艺去除氧化层,同时实现对氧化物半导体层222进行刻蚀,形成连接孔2227,如图17所示。最后,在第二过孔2221和连接孔2227中形成第二电极结构2222,并使第二电极结构2222在连接孔2227中与氧化物半导体层222形成侧面接触(side contact),如图18所示。通过将氧化物半导体层222刻蚀至穿透,由此,相对于第二过孔2221底部的面积,在连接孔2227中氧化物半导体层222具体更大面积的环形侧面,从而有效改善了第二电极结构2222与氧化物半导体层222之间的接触电阻,并避免了工艺过程中氧化物半导体层222损伤带来的不稳定缺陷。

73.进一步的,在一些实现方式中在刻蚀氧化物半导体层222时,可将该氧化物半导体层222刻蚀穿透,也即连接孔2227为贯穿氧化物半导体层222的连接孔2227;从而保证第二电极结构2222与氧化物半导体层222形成更加良好的侧面接触结构。

74.进一步的,在一些实现方式中将氧化物半导体层222刻蚀穿透后,应当避免再连接孔2227内出现氧化物半导体层222的侧面侵蚀;也就是说,连接孔2227底部的孔径应当小于等于第二过孔2221底部的孔径,从而保证在形成第二电极结构2222后,第二电极结构2222能够与氧化物半导体层222形成的侧面接触更加稳定可靠。

75.在一具体的实现方式中,将氧化物半导体层222上方形成的第二过孔2221的坡度角可控制在70

°

~80

°

,当氧化物半导体层222被boe etch刻穿后,可将氧化物半导体层222的坡度角控制在70

°

~90

°

;第二过孔2221和连接孔2227的大小可控制在2.0u~2.5u。该实现方式中,通过控制过孔的直径以及坡度,可保证在制造过程中各个膜层结构的稳定性,避免坍塌,提高工艺良率。

76.通过上述工艺方法,也可在仅使用一道图形化掩膜完成接触孔和电极结构的制造,简化了制造工艺,降低了生产成本。

77.2、针对双栅极结构的驱动背板而言:

78.请参阅图19,与前述的单栅极结构对应的工艺步骤相同的是,首先,提供衬底基板31;接着,在衬底基板31上形成缓冲层32;接着,在缓冲层32远离衬底基板31的一侧对应的第一区域bm形成低温多晶硅半导体层321,以及对应的第二区域aa形成氧化物半导体层351。具体来讲,与前述示例的单栅极结构的工艺步骤不同的是,由于在本示例中由于需要形成氧化物半导体层351对应的双栅极结构,因此,低温多晶硅半导体层321与氧化物半导体层351可位于不同层,如图19所示。

79.在一些实现方式中,在形成缓冲层32后,可在缓冲层32远离衬底基板31的表面形成低温多晶硅半导体层321。接着,在低温多晶硅半导体层321上覆盖第一栅绝缘层33;再接着,在第一栅绝缘层33上形成第一栅极331和遮光结构332,第一栅极331和遮光结构332可处于同一层。其中,第一栅极331位于第一区域bm,第一栅极331可作为低温多晶硅半导体层321的栅极;遮光结构332位于第二区域aa,可作为氧化物半导体层351的背栅结构。进一步的,在第一栅极331和遮光结构332上覆盖第二绝缘层35;再接着,在第二绝缘层35远离衬底基板31一侧的第二区域aa形成氧化物半导体层351,在氧化物半导体层351远离衬底基板31的一侧覆盖第二栅绝缘层36;再接着,在第二栅极361远离衬底基板31的一侧覆盖第一绝缘层34,如图19所示。接下来,对上述制造的膜层结构开启低温多晶硅半导体层321和氧化物半导体层351各自对应的接触孔。在下面提供两种形成接触孔的具体方式:

80.一些可选的实现方式中,在形成接触孔的过程中考虑对氧化物半导体层351进行保护,一些可选的实现方式中制造方法如下:

81.首先,在第一绝缘层34上覆盖图形化掩膜,并在第一绝缘层34上形成接触孔;其中,接触孔包括:形成在低温多晶硅半导体层321远离衬底基板31一侧的第一过孔3211,以及形成在氧化物半导体层351远离衬底基板31一侧的第二过孔3511。可以理解的,第一过孔3211穿透第一绝缘层34、第二栅绝缘层36和第二绝缘层35,其底部延伸至低温多晶硅半导体层321;第二过孔3511穿透第一绝缘层34,其底部延伸至氧化物半导体层351。进一步的,接触孔还可包括:形成在遮光结构332远离衬底基板31一侧的第三过孔3321;该第三过孔3321可用于连接氧化物半导体层351对应的背栅(遮光结构332),如图20所示。

82.进一步的,可在含氧的气氛条件下进行干法刻蚀第一绝缘层34,形成延伸至多晶硅半导体层的第一过孔3211,以及形成延伸至氧化物半导体层351的第二过孔3511。接着,去除第一过孔3211底部的低温多晶硅半导体层321表面的氧化层。可在无氧的气氛条件下刻蚀掉第一过孔3211底部的低温多晶硅半导体层321表面的氧化层。避免了使用boe etch工艺,从而在改善低温多晶硅半导体层321表面接触电阻的情况下,保护氧化物半导体层351不被损害。

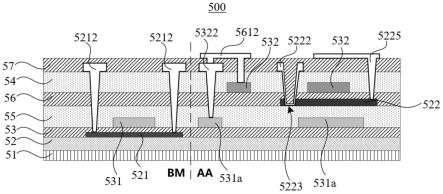

83.上述干法刻蚀工艺的两步工艺过程的具体实现可参考前述单栅结构的驱动背板示例中的阐述,本示例中不再赘述。

84.再接着,在第一过孔3211中形成与低温多晶硅半导体层321接触的第一电极结构3212,在第二过孔3511中形成与氧化物半导体层351接触的第二电极结构3512,以及在第三过孔3321中形成与遮光结构332接触的第三电极结构3322,如图21所示。由于,在前面的步骤中通过含氧和不含氧的两步干法刻蚀,清除了低温多晶硅半导体表面的氧化层,同时又避免了氧化物半导体层351的损伤;因此,第一电极结构3212可与低温多晶硅半导体层321在第一过孔3211的底部形成良好的电接触;第二电极结构3512也可与氧化物半导体层351在第二过孔3511的底部形成良好的电接触;第三电极结构3322也可与遮光结构332形成良好的电接触。

85.再接着,在第一电极结构3212、第二电极结构3512和第三电极结构3322上覆盖第三绝缘层37;可以理解的,第三绝缘层37覆盖在第一绝缘层34远离衬底基板31的一侧,并将第一电极结构3212、第二电极结构3512和第三电极结构3322远离衬底基板31的端部覆盖。进一步,再刻蚀第三绝缘层37和第一绝缘层34,形成用于搭接第三电极结构3322和第二栅极361的搭接过孔3611,如图22所示。然后,在搭接过孔3611中形成搭接结构3612,以将遮光结构332和第二栅极361电连接,如图23所示。

86.在上述的制造过程中,搭接过孔3611是在形成第三电极结构3322之后进行刻蚀的,因此,可准确控制刻蚀第三过孔3321的深度,不会对第二栅极361造成损伤;可保证在形成搭接结构3612之后具有良好的导电接触。而形成第一过孔3211和第二过孔3511时刻蚀形成第三过孔3321,由于低温多晶硅半导体层321和遮光结构332之间仅具有第一栅绝缘层33,低温多晶硅半导体层321和遮光结构332之间的厚度差较小,在形成第一过孔3211、第二过孔3511和第三过孔3321的过程中几乎不会损害遮光结构332。另外,由于遮光结构332和第二栅极361之间存在较大的厚度差(第二绝缘层35和第二栅绝缘层36),通过将第三过孔3321和搭接过孔3611分开形成,可避免为了将第一绝缘层34、第二栅绝缘层36和第二栅极361刻穿,而损坏或刻穿第二栅极361。

87.进一步的,在形成搭接过孔3611时,还可同时形成第四过孔3513,该第四过孔3513底部延伸至氧化物半导体层351,如图22所示;接着在形成搭接结构3612时,在第四过孔3513中形成第四电极结构3514,第四电极结构3514和氧化半导体层的表面导电接触,如图23所示,第四电极结构3514和第二电极结构3512可作为氧化物半导体层351的源/漏极。

88.为了使上述示例中的双栅结构的驱动背板的结构更易于理解,下面通过图24、25和26进行说明;

89.在图24中,示出了在第一区域bm内,低温氧化物半导体层351远离衬底基板31的一侧设置第一栅极331实现对沟道的控制;在低温氧化物半导体层351的两端通过第一过孔3211中的第一电极向远离衬底基板31的方向引出进行走线。

90.在图25中,示出了在第二区域aa内,氧化物半导体层351对应的双栅极结构位于其上下两侧,用于控制氧化物半导体层351的沟道;也即遮光结构332位于氧化物半导体层351靠近衬底基板31的一侧,第二栅极361位于氧化物半导体层351远离衬底基板31的一侧。在第二过孔3511中形成的第二电极结构3512向远离衬底基板31的方向引出,并连接对应的公共电极;在第四过孔3513中形成的第四电极结构3514向远离衬底基板31的方向引出,可用

于与像素结构的电极连接。

91.在图26中,示出了在第二区域aa内,遮光结构332通过搭接过孔3611中的第三电极结构3322向远离衬底基板31的方向引出,并通过搭接结构3612连接至第二栅极361。

92.一些可选的实现方式中,在形成接触孔的过程中不对氧化物半导体层351进行保护,制造方法如下:

93.与前一示例中对双栅极结构的氧化物半导体层351进行保护的制造方法所不同的是:在该种实现方法中首先在第一绝缘层34上覆盖图形化掩膜,并在第一绝缘层34上形成接触孔;可采用现有的刻蚀工艺实现,不限制。接着,去除第一过孔3211底部的低温多晶硅半导体层321表面的氧化层,并刻蚀第二过孔3511底部的氧化物半导体层351形成连接孔3518。在一些实现方式中,可采用boe etch工艺去除氧化层,同时实现对氧化物半导体层351进行刻蚀,形成连接孔3518,如图27所示。最后,在第二过孔3511和连接孔3518中形成第二电极结构3512,并使第二电极结构3512在连接孔3518中与氧化物半导体层351形成侧面接触,如图28所示,实现良好的电连接。

94.进一步的,在一些实现方式中在刻蚀氧化物半导体层351时,可将该氧化物半导体层351刻蚀穿透,也即连接孔3518为贯穿氧化物半导体层351的连接孔3518;从而保证第二电极结构3512与氧化物半导体层351形成更加良好的侧面接触结构。

95.进一步的,在一些实现方式中将氧化物半导体层351刻蚀穿透后,应当避免再连接孔3518内出现氧化物半导体层351的侧面侵蚀;也就是说,连接孔3518底部的孔径应当小于等于第二过孔3511底部的孔径,从而保证在形成第二电极结构3512后,第二电极结构3512能够与氧化物半导体层351形成的侧面接触更加稳定可靠。在一具体的实现方式中,将氧化物半导体层351上方形成的第二过孔3511的坡度角可控制在70

°

~80

°

,当氧化物半导体层351被boe etch刻穿后,可将氧化物半导体层351的坡度角控制在70

°

~90

°

;第二过孔3511和连接孔3518的总深度为:h=500nm(第一绝缘层34厚度)+150nm(第二栅绝缘层36厚度)+40nm(氧化物半导体层351厚度)=690nm,总深度约700nm;第二过孔3511和连接孔3518的大小可控制在2.0u~2.5u。该实现方式中,通过控制过孔的直径、深度以及坡度,可保证在制造过程中各个膜层结构的稳定性,避免坍塌,提高工艺良率。

96.因此,在该种实现方式中,也可在仅使用一道图形化掩膜完成接触孔和电极结构的制造,简化了制造工艺,降低了生产成本。

97.针对后续工艺中的电极结构、第三绝缘层37、搭接结构3612等的形成工艺以及对应的有益效果可参见前一示例中的双栅极结构的驱动背板的工艺过程,此处不再赘述;完成制造后驱动背板结构如图29所示。

98.请参阅图30,基于同一发明构思,在本发明的又一实施例中还提供了一种驱动背板500,该驱动背板500包括:衬底基板51、低温多晶硅半导体层521、氧化物半导体层522、第一绝缘层54、第一电极结构5212以及第二电极结构5222。

99.衬底基板51包括第一区域bm和第二区域aa;低温多晶硅半导体层521设置在衬底基板51的第一区域bm;氧化物半导体层522设置在衬底基板51的第二区域aa;第一绝缘层54设置在低温多晶硅半导体层521和氧化物半导体层522远离衬底基板51的一侧;在第一绝缘层54设置有接触孔;接触孔包括:第一过孔和第二过孔,第一过孔延伸至低温多晶硅半导体层521;第二过孔延伸至氧化物半导体层522;氧化物半导体层522对应于第二过孔底部的位

置设置有连接孔5223;第一电极结构5212,设置在第一过孔中,并与低温多晶硅半导体层521接触;以及第二电极结构5222,设置在第二过孔和连接孔5223中,并在连接孔5223中与所述氧化物半导体层522形成侧面接触。

100.在上述的驱动背板500结构中,由于在氧化物半导体层522设置有连接孔5223,因此,在制造的过程中可在一道图形化掩膜工艺中同时开启第一过孔和第二过孔,并在清洗低温多晶硅半导体层521表面的氧化层时对氧化物半导体层522进行刻蚀形成连接孔5223,并氧化物半导体层522在连接孔5223内与第二电极结构5222形成侧面接触,实现稳定的电连接。该结构可避免先后开启第一过孔和第二过孔,简化了制造工艺,降低成本。

101.进一步的,连接孔5223可穿透氧化物半导体层522,从而保证侧面接触的稳定性。

102.在一些可选的实现方式中氧化物半导体层522可对应设置位单栅极结构,实现方式如下:

103.请参阅图31,该驱动背板510还可包括:缓冲层52;该缓冲层52设置在衬底基板51和低温多晶硅半导体层521之间;低温多晶硅半导体层521和氧化物半导体层522设置在同一层。进一步的,在第一绝缘层54和半导体层(低温多晶硅半导体层521和氧化物半导体层522)之间还设置有第二绝缘层55。

104.在一些可选的实现方式中氧化物半导体层522可对应设置位双栅极结构,实现方式如下:

105.请参阅图30,该驱动背板500还可包括:第一栅绝缘层53、第一栅极531、遮光结构531a、第二绝缘层55、第二栅绝缘层56以及第二栅极532。

106.请继续参阅图30,第一栅绝缘层53设置在低温多晶硅半导体层521远离衬底基板51的一侧;第一栅极531、遮光结构531a,设置在第一栅绝缘层53远离衬底基板51的一侧;第一栅极531位于第一区域bm,遮光结构531a位于所述第二区域aa;第一栅极531和遮光结构531a可位于同一层,并且可通过同一道刻蚀工艺形成。第二绝缘层55设置在第一栅极531和遮光结构531a远离衬底基板51的一侧;氧化物半导体层522设置在第二绝缘层55远离衬底基板51的一侧;第二栅绝缘层56设置在氧化物半导体层522远离衬底基板51的一侧;第二栅极532设置在第二栅绝缘层56与第一绝缘层54之间。

107.在一些可选的实现方式中该驱动背板500的接触孔还可包括:第三过孔;该第三过孔设置在遮光结构531a远离衬底基板51一侧;第三过孔中设置有与遮光结构531a接触的第三电极结构5322;驱动背板500还可包括:第三绝缘层57,该第三绝缘层57设置在第一电极结构5212、第二电极结构5222和第三电极结构5322远离衬底基板51的一侧;第一绝缘层54和第三绝缘层57中设置有搭接过孔;在搭接过孔中设置有导电搭接结构5612,导电搭接结构5612分别与遮光结构531a和第二栅极532连接,如图30所示。该种结构可避免在制造过程种对第二栅极532造成损坏或刻蚀穿透。

108.需要说明的是,在本实施例中的驱动背板500可由前述方法实施例中的驱动背板500制造方法进行制造得到;因此,在本实施例中的驱动背板500未进一步说明的结构,例如氧化物半导体层522对应的另一第四电极结构5225(图31中未示出)等,可在参考前述的方法实施例中所述介绍的结构,此处不再赘述。

109.基于同一发明构思,在本发明的又一实施例中还提供了一种显示面板,包括前述实施例中任一所述的驱动背板。

110.需要说明的是,本实施例提供的一种显示面板,其中驱动背板的结构可参照前述实施例,所产生的有益效果已在前述关于基板封框结构的实施例中进行阐述,具体可参见前述关于基板封框结构的实施例,本实施例中不再赘述。显示面板中的像素发光结构、彩膜基板等未进行介绍的结构,可参见目前已有的现有技术,本实施例中不再赘述。

111.在以上的描述中,对于各层的构图、刻蚀等技术细节并没有做出详细的说明。但是本领域技术人员应当理解,可以通过各种技术手段,来形成所需形状的层、区域等。另外,为了形成同一结构,本领域技术人员还可以设计出与以上描述的方法并不完全相同的方法。另外,尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。

112.尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

113.显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1