扇出封装晶圆的对位方法及扇出封装晶圆与流程

1.本发明涉及芯片封装技术领域,特别涉及一种扇出封装晶圆的对位方法及扇出封装晶圆。

背景技术:

2.随着晶圆扇出封装的应用逐渐广泛,衍生出了不同类型的产品应用和封装要求,但封装过程中芯片间距也会有很多变化,例如:

3.1、芯片重布后间距变化多:重布后的芯片间距由不同的封装位置和尺寸决定;

4.2、扇出比(芯片面积/封装面积)的范围变化大:扇出比大意味着芯片间距增大;

5.3、相比较原来芯片间距为晶圆划片道尺寸,芯片重布后,芯片间距会显著放大。

6.同时在目前的先进封装工艺中,芯片重布后的晶圆扇出封装还需要通过重布线层进行优化布线,形成重布线层时需要利用光刻工艺形成金属导电层。

7.基于传统的晶圆级封装工艺进行重布线层的光刻工艺时,如图1所示,往往利用四个相邻芯片1之间的划片道3交叉点作为曝光对位点4,利用曝光设备的对位视窗2获取对应的曝光对位点4进行对位并进行曝光。

8.而基于晶圆扇出封装进行光刻工艺时曝光显影时,芯片重布后芯片间距会显著放大,但曝光设备的对位视场大小固定、搜寻对位标记范围固定,有可能出现如图2或图3所示的对位视窗图像。如图2所示,四个封装结构的四个芯片1分别位于所述对位视窗2的四个角落,四个芯片间隔的封装结构很宽,无法准确快速地确定贴片后的芯片分布,对扇出封装晶圆难以进行对位;更有甚者,如图3所示,四个封装结构的四个芯片1中的多个甚至四个全部位于所述对位视窗2的范围外,曝光设备的对位视窗看不到任何芯片,无法确定四个封装结构的封装划片道3的具体位置,即无法确定贴片后的芯片分布,对扇出封装晶圆难以进行对位。

技术实现要素:

9.本发明为了克服现有技术的不足,提供一种扇出封装晶圆的对位方法及扇出封装晶圆。

10.为了实现上述目的,本发明实施例还提供了一种扇出封装晶圆的对位方法,包括:

11.提供扇出封装晶圆基板,所述扇出封装晶圆基板具有若干个第一扇出封装区域和贴片于第一扇出封装区域内的第一芯片,在所述扇出封装晶圆基板内选择至少三个对位区域,所述对位区域至少包括2x2的四颗相邻第一芯片及每一颗第一芯片所对应的四个相邻的第一扇出封装区域;

12.每一个对位区域选取至少一颗第一芯片作为对位点芯片,对位点芯片对应的第一扇出封装区域作为对位扇出封装区域,在芯片贴片工艺中,将所述对位点芯片从对位扇出封装区域的预定贴片位置按照预定移动规则向四颗相邻第一芯片的中间位置移动并贴片,使得所述对位点芯片的实际贴片位置位于后续工艺对应的曝光设备对位视窗内;

13.根据对位点芯片在曝光设备对位视窗的位置和预定移动规则确定整个扇出封装晶圆基板的芯片贴片位置。

14.可选的,每一个对位区域选取两颗斜对角的第一芯片作为对位点芯片,两颗所述对位点芯片从对应的对位扇出封装区域的预定贴片位置按照预定移动规则移动到实际贴片位置并贴片。

15.可选的,每一个对位区域选取一颗第一芯片作为对位点芯片,所述对位点芯片从对应的对位扇出封装区域的预定贴片位置按照预定移动规则移动到实际贴片位置并贴片。

16.可选的,当所述对位点芯片对应的预定贴片位置本身全部或部分位于后续光刻工艺对应的曝光设备对位视窗内,在贴片时,所述对位点芯片向中间位置移动后,对位点芯片的实际贴片位置仍位于对位点芯片对应的对位扇出封装区域内。

17.可选的,当对位点芯片对应的预定贴片位置全部位于后续光刻工艺对应的曝光设备对位视窗外,在贴片时,所述对位点芯片向中间位置移动后,对位点芯片对应的最大移动位置不超过四个相邻第一扇出封装区域之间的封装划片道要求的最小宽度区域。

18.可选的,所述第一扇出封装区域除了具有第一芯片,还具有若干其他芯片,所述其他芯片贴片于其他芯片对应的预定贴片位置。

19.本发明实施例提供了一种扇出封装晶圆,包括:

20.扇出封装晶圆基板,所述扇出封装晶圆基板具有若干个第一扇出封装区域和贴片于第一扇出封装区域内的第一芯片;

21.所述扇出封装晶圆基板内至少具有三个对位区域,所述对位区域至少包括2x2的四颗相邻第一芯片及每一颗第一芯片所对应的四个相邻的第一扇出封装区域;

22.每一个对位区域的至少一颗第一芯片作为对位点芯片,对位点芯片对应的第一扇出封装区域作为对位扇出封装区域,在芯片贴片工艺中,将所述对位点芯片从对位扇出封装区域的预定贴片位置按照预定移动规则向四颗相邻第一芯片的中间位置移动并贴片,使得所述对位点芯片的实际贴片位置位于后续工艺对应的曝光设备对位视窗内,其余第一芯片贴片于对应第一扇出封装区域的预定贴片位置。

23.可选的,每一个对位区域选取两颗斜对角的第一芯片作为对位点芯片,两颗所述对位点芯片从对应的对位扇出封装区域的预定贴片位置按照预定移动规则分别向四颗相邻第一芯片的中间位置移动并贴片。

24.可选的,每一个对位区域选取一颗第一芯片作为对位点芯片,所述对位点芯片从对应的对位扇出封装区域的预定贴片位置按照预定移动规则向四颗相邻第一芯片的中间位置移动并贴片。

25.可选的,当所述对位点芯片对应的预定贴片位置本身全部或部分位于后续光刻工艺对应的曝光设备对位视窗内,对位点芯片的实际贴片位置位于对位点芯片对应的对位扇出封装区域内。

26.可选的,当对位点芯片对应第一扇出封装区域的预定贴片位置全部位于后续光刻工艺对应的曝光设备对位视窗外,对位点芯片对应的实际贴片位置不超过四个相邻第一扇出封装区域之间的封装划片道要求的最小宽度区域。

27.可选的,所述第一扇出封装区域除了具有第一芯片,还具有若干其他芯片,所述其他芯片贴片于其他芯片对应的预定贴片位置。

28.综上所述,本发明的有益效果在于:

29.本发明在扇出封装晶圆基板选择至少三个对位区域,所述对位区域至少包括2x2的四颗相邻第一芯片,每一个对位区域选取至少一颗第一芯片作为对位点芯片,在芯片贴片工艺中,将所述对位点芯片从预定贴片位置按照预定移动规则向四颗相邻第一芯片的中间位置移动,使得所述对位点芯片的实际贴片位置位于后续工艺对应的曝光设备对位视窗内,根据对位点芯片在曝光设备对位视窗的位置和预定移动规则整个扇出封装晶圆基板的芯片贴片位置。本发明通过牺牲几颗对位区域的对位点芯片,利用对位点芯片按预定移动规则向四颗相邻第一芯片的中间位置移动,确定对位点位置,从而能确定整个扇出封装晶圆基板的芯片贴片位置,曝光设备进行粗对位的时候不会找错芯片的行列,且适用于现有的光刻机台进行光刻,不需要额外的对位点图案制作,成本较低。

30.为让本发明的上述和其它目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合附图,作详细说明如下。

附图说明

31.图1为现有技术的基于传统的晶圆级封装工艺进行光刻工艺时的光刻对位结构示意图;

32.图2和图3为现有技术的基于晶圆扇出封装进行光刻工艺时的光刻对位结构示意图;

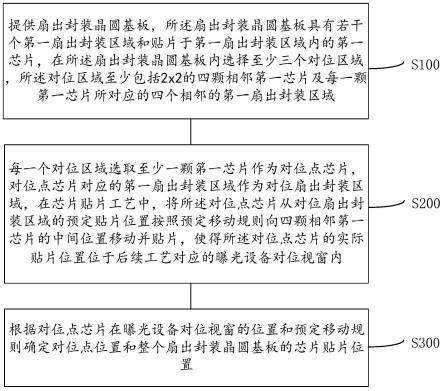

33.图4为本发明实施例的一种扇出封装晶圆的光刻对位方法的流程示意图;

34.图5~图10为本发明实施例的扇出封装晶圆的结构示意图。

具体实施方式

35.为了便于本领域技术人员的理解,下面将结合具体实施例对本发明作进一步详细描述。

36.本发明实施例首先提供了一种扇出封装晶圆的光刻对位方法,请参考图4,为所述光刻对位方法的流程示意图,包括:

37.步骤s100,提供扇出封装晶圆基板,所述扇出封装晶圆基板具有若干个第一扇出封装区域和贴片于第一扇出封装区域内的第一芯片,在所述扇出封装晶圆基板内选择至少三个对位区域,所述对位区域至少包括2x2的四颗相邻第一芯片及每一颗第一芯片所对应的四个相邻的第一扇出封装区域;

38.步骤s200,每一个对位区域选取至少一颗第一芯片作为对位点芯片,对位点芯片对应的第一扇出封装区域作为对位扇出封装区域,在芯片贴片工艺中,将所述对位点芯片从对位扇出封装区域的预定贴片位置按照预定移动规则向四颗相邻第一芯片的中间位置移动并贴片,使得所述对位点芯片的实际贴片位置位于后续工艺对应的曝光设备对位视窗内;

39.步骤s300,根据对位点芯片在曝光设备对位视窗的位置和预定移动规则确定对位点位置和整个扇出封装晶圆基板的芯片贴片位置。

40.具体的,执行步骤s100,请参考图5和图8,图5为所述扇出封装晶圆的整体结构示意图,图8为一个对位区域内的四颗相邻第一芯片及所对应的四个相邻的第一扇出封装区

域的结构示意图。

41.在本实施例中,所述扇出封装晶圆基板为用于后续芯片扇出封装的基板,所述扇出封装晶圆基板可以为封装载板、玻璃载板、空白半导体晶圆片等其中的一种。

42.在晶圆扇出封装工艺中,在所述扇出封装晶圆基板表面预定的位置进行芯片贴片,并在所述扇出封装晶圆基板表面和芯片表面进行芯片塑封封装,形成芯片封装结构;然后将所述扇出封装晶圆基板与芯片封装结构进行剥离,在所述芯片封装结构对应的剥离表面形成重布线层,其中,形成重布线层时需要利用光刻工艺形成金属图案。

43.光刻工艺需要先利用对位点进行粗对位,如果不采用晶圆扇出封装形成进行光刻工艺形成重布线层,如图1所示,往往利用四个相邻芯片之间的划片道交叉点作为粗对位的对位点。但随着扇出封装晶圆的布局多样化,芯片位于封装结构的位置各不相同且不同的扇出比,导致芯片重布后间距变化多且间距变大,甚至大于光刻工艺对应的曝光设备对位视窗的尺寸(如图3所示),即在现有的曝光设备对位视窗找不到任何一颗芯片,没办法据此进行对位,且利用上述方法容易导致对位的行列错误,导致对位失败。

44.为此,在本实施例中,所述扇出封装晶圆基板10分为若干个第一扇出封装区域20,一个所述第一扇出封装区域20用于形成一个扇出封装结构,且所述第一扇出封装区域20的尺寸大于预贴片的第一芯片的尺寸。

45.在进行粗对位时,扇出封装晶圆至少需要三个对位点进行对位,以确定贴片后芯片分布。因此在所述扇出封装晶圆基板内选择至少三个对位区域15,每一个对位区域15对应一个对位点。

46.如图5和图6所示,虚线框示出了一个对位区域15,对位区域15内包括六个相邻的第一扇出封装区域20和六颗相邻第一芯片的预定贴片位置31。

47.在其他实施例中,每一个对位区域至少包括2x2的四个相邻的第一扇出封装区域20和2x2的四颗相邻第一芯片。

48.在后续的说明中,以四颗相邻第一芯片30分别为b、c、d、e,一颗第一芯片30对应一个第一扇出封装区域20为例进行说明。四颗第一芯片30在对应的第一扇出封装区域20内具有对应的预定贴片位置31。

49.在本实施例中,如图6~图10所示,一个第一扇出封装区域20仅用于封装一颗第一芯片30。

50.在其他实施例中,一个第一扇出封装区域除了封装有一颗第一芯片,还同时封装有其它芯片。所述第一芯片和其它芯片的芯片类型、尺寸可以相同,也可以不同。所述第一芯片与其它芯片的区别仅仅在于:在扇出封装晶圆基板的对位区域,至少有一颗第一芯片作为对位点芯片向四颗相邻第一芯片的中间位置移动,使得所述对位点芯片的实际贴片位置位于后续光刻工艺对应的曝光设备对位视窗内。

51.执行步骤s200,如图6~图8所示,每一个对位区域至少具有四颗相邻第一芯片,选取至少一颗第一芯片作为对位点芯片30’,对位点芯片30’对应的第一扇出封装区域作为对位扇出封装区域20’,在芯片贴片工艺中,将所述对位点芯片30’从对位扇出封装区域20’的预定贴片位置31按照预定移动规则向四颗相邻第一芯片的中间位置移动并贴片,使得所述对位点芯片的实际贴片位置32’位于后续工艺对应的曝光设备对位视窗内,其余第一芯片30仍贴片于对应第一扇出封装区域20的预定贴片位置31。

52.其中图6为对位区域中包括对位点芯片b、e的第一芯片的预定贴片位置的结构示意图,图7为对位区域中包括对位点芯片b、e的第一芯片的实际贴片位置的结构示意图,图8为第一芯片贴片过程中移动位置的结构示意图。

53.其中,对位点芯片对应第一扇出封装区域的预定贴片位置可以位于后续光刻工艺对应的曝光设备对位视窗视野内,也可以位于后续光刻工艺对应的曝光设备对位视窗视野外。

54.在本实施例中,如图8所示,对位点芯片为两个第一芯片,对位点芯片b和e斜对角设置。当所述对位点芯片b和e对应第一扇出封装区域的预定贴片位置31本身全部或部分位于后续光刻工艺对应的曝光设备对位视窗40内,按照预定移动规则向中间位置移动后,对位点芯片b和e的实际贴片位置32仍位于对位点芯片对应的对位扇出封装区域20’内。

55.其中,所述预定移动规则可以为一确定的定值,也可以为根据第一芯片在第一扇出封装区域20的位置和尺寸确定移动规则。

56.在如图9所示的实施例中,由于对位点芯片的预定贴片位置31和实际贴片位置32全部都位于曝光设备对位视窗40内,因此只需要移动特定的位置即可以利用对位点芯片b和e确定对位点。如表1所示,为四个相邻的第一扇出封装区域和四颗相邻第一芯片的尺寸含义。

57.[0058][0059]

表1

[0060]

其中对位点芯片b在x轴方向的最大移动距离为(l-x)/2-(o

’‑

o),最小移动距离为2um,对位点芯片b在y轴方向的最大移动距离为(w-y)/2+(p

’‑

p),最小移动距离为2um。

[0061]

其中对位点芯片e在x轴方向的最大移动距离为(l-x)/2+(o

’‑

o),最小移动距离为2um,对位点芯片b在y轴方向的最大移动距离为(w-y)/2-(p

’‑

p),最小移动距离为2um。

[0062]

上述的最小移动距离可以根据不同的工艺进行调整。

[0063]

在其他实施例中,如图10所示,当对位点芯片30’对应的预定贴片位置31全部位于后续光刻工艺对应的曝光设备对位视窗40外,对位点芯片30’向中间位置移动后,对位点芯片30’对应的预定贴片位置的最大移动位置不超过四个相邻第一扇出封装区域之间的封装划片道要求的最小宽度区域,对位点芯片30’对应的实际贴片位置不超过四个相邻第一扇

出封装区域之间的封装划片道要求的最小宽度区域。

[0064]

其中对位点芯片b在x轴方向的最大移动距离为(l-x+k-k’)/2-(o

’‑

o),最小移动距离为(l-x+k-m)/2-(o

’‑

o),对位点芯片b在y轴方向的最大移动距离为(w-y+k-k’)/2+(p

’‑

p),最小移动距离为(w-y+k-n)/2+(p

’‑

p)。

[0065]

其中对位点芯片e在x轴方向的最大移动距离为(l-x+k-k’)/2+(o

’‑

o),最小移动距离为(l-x+k-m)/2+(o

’‑

o),对位点芯片b在y轴方向的最大移动距离为(w-y+k-k’)/2-(p

’‑

p),最小移动距离为(w-y+k-n)/2-(p

’‑

p)。

[0066]

由于对位点芯片对应的预定贴片位置全部位于后续光刻工艺对应的曝光设备对位视窗40外,因此需要提高对位点芯片的预定移动距离,即使对位点芯片的实际贴片位置位于预设的划片道区域(即宽度为k的区域),但只要不覆盖封装成品划片道要求的最小宽度区域(即宽度为k’的区域),不影响后续的划片切割。

[0067]

在本实施例中,在芯片贴片工艺中,将所述对位点芯片按照预定移动规则向四颗相邻第一芯片的中间位置移动,使得所述对位点芯片的实际贴片位置位于后续光刻工艺对应的曝光设备对位视窗内,但不作为对位点芯片的其他第一芯片仍正常贴片在预定贴片位置,对应第一芯片的扇出封装结构仍可以正常工作。

[0068]

本发明通过牺牲几个对位点芯片对应的几个扇出封装结构,为整个扇出封装晶圆进行对位,也不需要额外进行对位点制作,且适用于现有的光刻机台进行光刻,成本较低。

[0069]

在其他实施例中,当所述第一扇出封装区域内同时贴片有第一芯片和其他芯片,对位扇出封装区域也同时贴片对位点芯片和其他芯片,且仅仅对位点芯片进行移动,调整贴片位置,而位于对位扇出封装区域的其他芯片不移动,仍贴片于对应的预定贴片位置。

[0070]

在其他实施例中,当所述第一扇出封装区域内同时贴片有第一芯片和其他芯片,对位扇出封装区域只贴片对位点芯片,不贴片其他芯片,避免移动后的对位点芯片和其他芯片位置重叠。

[0071]

在本实施例中,对位扇出封装区域的对位点芯片30’采用正常的第一芯片进行贴片,在其他实施例中,对位扇出封装区域的对位点芯片也可以选择废芯片或空白芯片进行贴片。

[0072]

执行步骤s300,根据对位点芯片在曝光设备对位视窗的位置和预定移动规则确定对位点位置和整个扇出封装晶圆基板的芯片贴片位置。

[0073]

在本实施例中,两颗所述对位点芯片30’分别向四颗相邻第一芯片的中间位置移动的距离不同,按照上述预定移动规则进行移动,两颗所述对位点芯片b、e中间的位置即为对位点的中心位置,利用所述对位点位置确定整个扇出封装晶圆基板的芯片贴片位置。

[0074]

在其他实施例中,也可以将两颗所述对位点芯片的其中一个角作为对位点。

[0075]

由于本实施例利用对位点芯片确定对位点,利用对位点对扇出封装晶圆的芯片布局位置进行粗定位,因此对位点的实际位置可以根据需要在曝光设备对位视窗的范围内进行设定,不做特别限定。

[0076]

在其他实施例中,两颗所述对位点芯片分别向四颗相邻第一芯片的中间位置移动的距离也可以相同,通过获取对位点芯片的尺寸、第一扇出封装区域的尺寸、划片道的尺寸和对位点芯片预定贴片位置在第一扇出封装区域中的位置、对位点芯片向中间位置移动的距离,也可以确定对位点的位置。

[0077]

在其他实施例中,一个对位区域对应的对位点芯片还可以只有一个,四颗第一芯片中只有一颗对位点芯片向四颗相邻第一芯片的中间位置移动,当通过获取对位点芯片的尺寸、第一扇出封装区域的尺寸、划片道的尺寸和对位点芯片预定贴片位置在第一扇出封装区域中的位置、对位点芯片向中间位置移动的距离和对位点芯片位于曝光设备对位视窗的准确位置,也可以确定对位点的位置。

[0078]

在其他实施例中,一个对位区域对应的对位点芯片还可以超过2颗,通过对多个对位点芯片的位置调整进行定位。

[0079]

本发明实施例还提供了一种扇出封装晶圆,如图5~图8所示,包括:

[0080]

扇出封装晶圆基板10,所述扇出封装晶圆基板10具有若干个第一扇出封装区域20和贴片于第一扇出封装区域内的第一芯片30;

[0081]

所述扇出封装晶圆基板10内至少具有三个对位区域15,所述对位区域15至少包括2x2的四颗相邻第一芯片30及每一颗第一芯片所对应的四个相邻的第一扇出封装区域20;

[0082]

每一个对位区域的至少一颗第一芯片作为对位点芯片30’,对位点芯片对应的第一扇出封装区域作为对位扇出封装区域20’,在芯片贴片工艺中,将所述对位点芯片30’从对位扇出封装区域的预定贴片位置31’按照预定移动规则向四颗相邻第一芯片的中间位置移动并贴片,使得所述对位点芯片30’的实际贴片位置位于后续工艺对应的曝光设备对位视窗40内,其余第一芯片30贴片于对应第一扇出封装区域的预定贴片位置31。

[0083]

在本实施例中,如图8和图9所示,对位点芯片30’为两个第一芯片,对位点芯片b和e斜对角设置。当所述对位点芯片b和e对应的对位扇出封装区域20’的预定贴片位置31本身全部或部分位于后续光刻工艺对应的曝光设备对位视窗40内,按照预定移动规则向中间位置移动后,对位点芯片b和e的实际贴片位置仍位于对位点芯片30’对应的对位扇出封装区域20’内。

[0084]

在其中一个实施例中,所述预定移动规则具体为:

[0085]

其中对位点芯片b在x轴方向的最大移动距离为(l-x)/2-(o

’‑

o),最小移动距离为2um,对位点芯片b在y轴方向的最大移动距离为(w-y)/2+(p

’‑

p),最小移动距离为2um。

[0086]

其中对位点芯片e在x轴方向的最大移动距离为(l-x)/2+(o

’‑

o),最小移动距离为2um,对位点芯片b在y轴方向的最大移动距离为(w-y)/2-(p

’‑

p),最小移动距离为2um。

[0087]

在其他实施例中,如图10所示,当对位点芯片30’对应第一扇出封装区域的预定贴片位置31’全部位于后续光刻工艺对应的曝光设备对位视窗40外,对位点芯片30’向中间位置移动后,对位点芯片对应的预定贴片位置的最大移动位置不超过四个相邻第一扇出封装区域之间的封装划片道要求的最小宽度区域(即宽度为k’的区域)。

[0088]

其中对位点芯片b在x轴方向的最大移动距离为(l-x+k-k’)/2-(o

’‑

o),最小移动距离为(l-x+k-m)/2-(o

’‑

o),对位点芯片b在y轴方向的最大移动距离为(w-y+k-k’)/2+(p

’‑

p),最小移动距离为(w-y+k-n)/2+(p

’‑

p)。

[0089]

其中对位点芯片e在x轴方向的最大移动距离为(l-x+k-k’)/2+(o

’‑

o),最小移动距离为(l-x+k-m)/2+(o

’‑

o),对位点芯片b在y轴方向的最大移动距离为(w-y+k-k’)/2-(p

’‑

p),最小移动距离为(w-y+k-n)/2-(p

’‑

p)。

[0090]

在其他实施例中,所述第一扇出封装区域除了具有第一芯片,还具有若干其他芯片,所述第一芯片和其它芯片的芯片类型、尺寸可以相同,也可以不同。所述第一芯片与其

它芯片的区别仅仅在于:在扇出封装晶圆基板的对位区域,至少有一颗第一芯片作为对位点芯片向四颗相邻第一芯片的中间位置移动,使得所述对位点芯片的实际贴片位置位于后续光刻工艺对应的曝光设备对位视窗内。

[0091]

在其他实施例中,当所述第一扇出封装区域内同时贴片有第一芯片和其他芯片,对位扇出封装区域只贴片对位点芯片,不贴片其他芯片,避免移动后的对位点芯片和其他芯片位置重叠。

[0092]

在本实施例中,对位点芯片采用正常的第一芯片进行贴片,在其他实施例中,也可以选择废芯片或空白芯片进行贴片。

[0093]

以上所述仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1