一种提高桥式整流器功率的半导体封装结构的制作方法

1.本发明涉及一种改善桥式整流器半导体封装结构内部热平衡,提高桥式整流器功率,降低制造成本的半导体封装结构。

背景技术:

2.桥式整流器的主要功能是链接电网与电器,将交流电转换成直流电供电器产品使用,其内部晶片在工作过程中产生一定的热量,因晶片载体结构的不同,将直接影响桥式整流器元件及导热散热性能。传统的桥式整流器外形结构是电由环氧树脂封包,外形尺寸大,如附图6图7所示,原产品的引线框架设计结构,四颗芯片的承载面积与其他非芯片的承载面积差异较大,导致器件内部的四个芯片在工作过程产生的热量传输和散出不平衡。因原产品内部芯片的所承载面积小,导致承载的芯片尺寸小,产品功率较低,塑封体体积大,导致物料用量大,制造成本高。

技术实现要素:

3.本发明针对以上现有产品存在的问题,提供一种提高桥式整流器功率的半导体封装结构,包括芯片载体1,芯片载体2,芯片载体3,置于芯片载体上的芯片,铜连接线,单体引脚以及塑封体;其特征在于,塑封体内半导体元器件的尺寸大小、形状及其位置,根据芯片发出的热源大小,确定芯片载体面积大小、形状及其布设的位置,以改善芯片均衡散热和减小封装结构的体积。

4.所述芯片载体1载有二粒芯片,芯片载体1在半导体封装结构中布设为最大载体面积。

5.所述芯片载体2载有一粒芯片,芯片载体2在半导体封装结构中设置为芯片载体1的二分之一面积。

6.所述芯片载体2延伸与芯片载体1的连接部设计为窄长的水平段,以减小芯片载体2非承载芯片部分占有面积。

7.所述芯片载体3载有一粒芯片,芯片载体3在半导体封装结构中设置为芯片载体1的五分之二面积。

8.所述芯片载体3移至半导体封装结构中的右侧,芯片载体3延伸与芯片载体1的连接部设计为窄长的水平段,端部呈t形,以减小芯片载体3非承载芯片部分占有面积。

9.所述单体引脚设置为竖向窄长的的上段宽、下段窄的单体引脚,以减小其占有面积。

10.所述铜连接线为拱形状。

11.所述芯片载体1能够承载二粒芯片分别为3.048mm的需求,芯片载体2,芯片载体3分别能够承载芯片为3.048mm的需求。

12.四粒芯片分别与铜连接线焊接,芯片载体和单体引脚分别与产品引脚焊接后,用塑封体封装,形成产品本体长24~25.3mm,宽10.3~10.5mm,厚3.2-4.5mm。

13.本发明的优点是,由于增大了芯片载体的面积,从而增加了芯片的尺寸,提高了芯片电流容量,使芯片产生的热源能均衡地传输散出,使功率提升了50%。同时由于减小了载体连接部的占有面积,从而也减少了塑封体的用料(节约塑封料约30%),进步优化了树脂(黑胶)的使用量,节约铜材27%,降低了产品成本26%,缩小了产品尺寸。

附图说明

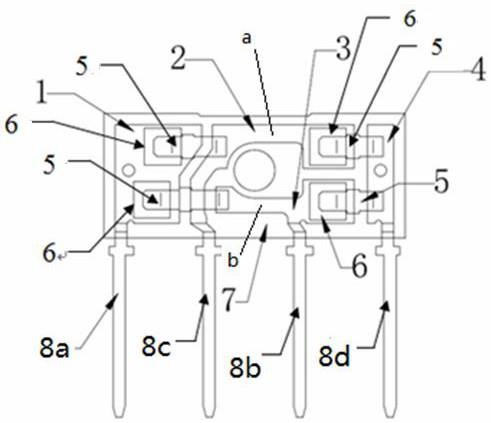

14.图1是本发明的封装结构内部元器件布置的平面图;图2是图1的侧视图;图3是图1内部局部元件布置放大平面图;图4是图3的侧视图;图5是本发明封装后产品外形平面图;图6是传统桥式整流器半导体封装结构内部元器件布置平面图;图7是图6的侧视图;图8是传统桥式整流器半导体封装后产品外形平面图;图9为现有成品(kbj)外形示意图;图10为本发明产品(kbjl)外形示意图;图中标号说明:1-芯片载体1;2-芯片载体2;3.-芯片载体3;4-单体引脚;5-铜连接线 ;6-芯片;7-塑封体;8(8a,8b,8c,8d)-产品引脚。

具体实施方式

15.请参兑阅附图所示,本发明包括芯片载体1,芯片载体2,芯片载体3,置于芯片载体上的芯片6,铜连接线5,单体引脚4以及塑封体7;塑封体内半导体元器件的尺寸大小、形状及其位置,根据芯片发6出的热源大小,确定芯片载体1、载体2、载体3面积大小、形状及其布设的位置,以改善芯片6均衡散热和减小封装结构的体积。

16.所述芯片载体1载有二粒芯片6,芯片载体1在半导体封装结构中布设为最大载体面积。

17.所述芯片载体2载有一粒芯片6,芯片载体2在半导体封装结构中设置为芯片载体1的二分之一面积。

18.所述芯片载体2延伸与芯片载体1的连接部设计为窄长的水平段a,以减小芯片载体2非承载芯片6部分的占有面积。

19.所述芯片载体3载有一粒芯片6,芯片载体3在半导体封装结构中设置为芯片载体1的五分之二面积。

20.所述芯片载体3移至半导体封装结构中的右侧,芯片载体3延伸与芯片载体1的连接部设计为窄长的水平段b,端部呈t形,以减小芯片载体3非承载芯片6部分的占有面积。

21.所述单体引脚4设置为竖向窄长的上段宽、下段窄的单体引脚,以减小其占有面积。

22.所述铜连接线5为拱形状。

23.所述芯片载体1能够承载二粒芯片分别为3.048mm的需求,芯片载体2,芯片载体3

分别能够承载芯片为3.048mm的需求。

24.四粒芯片6分别与铜连接线5焊接,芯片载体1、芯片载体2、芯片载体3和单体引脚4分别与产品引脚8(8a,8b,8c,8d)焊接后,用塑封体封装,形成产品本体长24~25.3mm,宽10.3~10.5mm,厚3.2-4.5mm。

25.其中,本发明的产品引脚交流电极8b、8c与传统产品对调换(因芯片载体3的位置改变)。

26.本发明进行了温升仿真试验,对比现有传统产品,封装体内四颗芯片之间的最大工作温差为7.6℃,低于于市场现有产品的温差12.8℃,改善率最大下降约41%。功率提升了50%,制造成本降低26%。

27.本发明主要是改进原桥式整流器封装体内芯片载体1、载体2、载体3在封装体内的位置、承载芯片的体积,达到改善四颗芯片在封装体内的热平衡性,提高产品功率,並缩小产品体积降低原材料使用量及制造成本。

28.原产品与本发明产品对应的芯片承载面积比较(单位:平方毫米):原产品与本发明产品芯片热模拟比较(单位:℃):。

技术特征:

1.一种提高桥式整流器功率的半导体封装结构,包括芯片载体1,芯片载体2,芯片载体3,置于芯片载体上的芯片,铜连接线,单体引脚以及塑封体,其特征在于,塑封体内半导体元器件的尺寸大小、形状及其位置,根据芯片发出的热源大小,确定芯片载体面积大小、形状及其布设的位置,以改善芯片均衡散热和减小封装结构的体积。2.按权利要求1所述提高桥式整流器功率的半导体封装结构,其特征在于,所述芯片载体1载有二粒芯片,芯片载体1在半导体封装结构中布设为最大载体面积。3.按权利要求1所述提高桥式整流器功率的半导体封装结构,其特征在于,所述芯片载体2载有一粒芯片,芯片载体2在半导体封装结构中设置为芯片载体1的二分之一面积。4.按权利要求3所述提高桥式整流器功率的半导体封装结构,其特征在于,所述芯片载体2延伸与芯片载体1的连接部设计为窄长的水平段,以减小芯片载体2非承载芯片部分的占有面积。5.按权利要求1所述提高桥式整流器功率的半导体封装结构,其特征在于,所述芯片载体3载有一粒芯片,芯片载体3在半导体封装结构中设置为芯片载体1的五分之二面积。6.按权利要求5所述提高桥式整流器功率的半导体封装结构,其特征在于,所述芯片载体3移至半导体封装结构中的右侧,芯片载体3延伸与芯片载体1的连接部设计为窄长的水平段,端部呈t形,以减小芯片载体3非承载芯片部分的占有面积。7.按权利要求1所述提高桥式整流器功率的半导体封装结构,其特征在于,所述单体引脚设置为竖向窄长的上段宽、下段窄的单体引脚。8.按权利要求1所述提高桥式整流器功率的半导体封装结构,其特征在于,所述铜连接线为拱形状。9.按权利要求1所述提高桥式整流器功率的半导体封装结构,其特征在于,所述芯片载体1能够承载二粒芯片分别为3.048mm的需求,芯片载体2,芯片载体3分别能够承载芯片3.048mm的需求。10.按权利要求1所述提高桥式整流器功率的半导体封装结构,其特征在于,四粒芯片分别与铜连接线焊接,芯片载体和单体引脚分别与产品引脚焊接后,用塑封体封装,形成产品本体长24~25.3mm,宽10.3~10.5mm,厚3.2-4.5mm。

技术总结

本发明提供一种提高桥式整流器功率的半导体封装结构,包括芯片载体1,芯片载体2,芯片载体3,置于芯片载体上的芯片,铜连接线,单体引脚以及塑封体;塑封体内半导体元器件的尺寸大小、形状及其位置,根据芯片发出的热源大小,确定芯片载体面积大小、形状及其布设的位置,以改善芯片均衡散热和减小封装结构的体积。优点是,由于增大了芯片载体的面积,从而增加了芯片的尺寸,提高了芯片电流容量,使芯片产生的热源能均衡地传输散出,使功率提升了50%。同时由于减小了载体连接部的占有面积,从而也减少了塑封体的用料约30%,节约铜材27%,降低了产品成本26%,缩小了产品尺寸。缩小了产品尺寸。缩小了产品尺寸。

技术研发人员:夏镇宇 程根保 徐爱萍

受保护的技术使用者:敦南微电子(无锡)有限公司

技术研发日:2022.07.01

技术公布日:2022/10/11

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1