一种基于翘曲度及应力改善后的IPD滤波器制造方法与流程

一种基于翘曲度及应力改善后的ipd滤波器制造方法

技术领域

1.本发明涉及半导体器件的加工制造技术领域,尤其涉及一种基于翘曲度及应力改善后的ipd滤波器制造方法。

背景技术:

2.随着科技时代的进步,现如今5g时代已经来临,为了使手机和汽车信息传输等领域飞速发展适应5g新时代,就需要大功率的5g信号滤波器来做信号过滤,随即saw、baw、ipd滤波器相继被设计出来。其相应的有信号接收端、信号发射端,简称为rx、tx。

3.ipd滤波器(integrated product development filter)集成无源滤波器,它相比saw、baw可以容纳更大的带宽,也就是信号接收的范围更大,这是它最大的优势。目前为止,硅基的ipd滤波器基本趋于成熟,玻璃基ipd滤波器还在开发阶段,其优势相比硅基成本低,但玻璃基相比硅基较脆,其成分是二氧化硅。所以产品在制作的过程当中,会出现因产品结构间的相互应力导致玻璃基翘曲,甚至等到切割晶圆时发生碎片的缺陷。

技术实现要素:

4.基于此,有必要针对上述技术问题,提供一种基于翘曲度及应力改善后的ipd滤波器制造方法。

5.一种基于翘曲度及应力改善后的ipd滤波器制造方法,包括以下步骤:

6.s1、制备衬底,并对其表面进行清洗;

7.s2、在所述衬底上制备应力改善缓冲层;

8.s3、在所述应力改善缓冲层上制备电容,所述电容包括至下而上依次分布的下电极、介质层和上电极;

9.s4、在所述应力改善缓冲层上制备螺旋电感;

10.s5、制备第一pi层、第一金属走线和第二pi层,所述第一pi层覆盖在所述电容、螺旋电感和所述衬底上,所述第二pi层设置在所述第一pi层的上方,所述第一金属走线位于所述第一pi层和第二pi层之间;

11.s6、在所述第二pi层上制备连接凸点和第二金属走线,通过第一金属走线和第二金属走线使所述电容、螺旋电感与所述连接凸点相导通,形成ipd滤波器本体;

12.s7、对所述ipd滤波器本体进行减薄和切割后进行封装。

13.在其中一个实施例中,所述步骤s1包括:

14.s11、制备二氧化硅玻璃衬底;

15.s12、用等离子体清洗所述衬底的表面。

16.在其中一个实施例中,所述步骤s2包括:

17.s21、通过采用teos源pecvd生长sio2膜层的工艺,在所述衬底的上表面覆盖一层2000a以上的sio2膜层;

18.s22、通过化学抛光研磨工艺,对sio2膜层进行抛光,使其表面平坦化。

19.在其中一个实施例中,所述步骤s3中,所述下电极的制备过程如下:

20.s311、在所述sio2膜层的上表面通过pvd工艺做第一金属种籽层;

21.s312、通过带胶电镀工艺做5~10um的铜制管脚;

22.s313、去胶并通过刻蚀工艺去除多余的第一金属种籽层,获取下电极金属膜层;

23.s314、对所述下电极金属膜层进行cmp工艺处理;

24.s315、使用金属热退火工艺进行热退火。

25.在其中一个实施例中,所述步骤s3中,所述介质层的制备过程如下:

26.s321、在所述下电极的上表面通过pecvd工艺做sin膜层;

27.s322、通过光刻刻蚀工艺对sin膜层进行图形化,去除位于所述下电极上方以外的多余sin膜层;

28.s323、通过光刻涂胶技术对sin膜层的表面做精度修整;

29.s324、去除多余的胶残留。

30.在其中一个实施例中,所述步骤s3中,所述上电极的制备过程如下:

31.s331、在所述介质层的上表面通过pvd工艺做第二金属种籽层;

32.s332、通过带胶电镀工艺制备导电铜层,获取上电极金属膜层;

33.s333、对所述上电极金属膜层进行cmp工艺处理;

34.s334、去除多余胶,使用金属热退火工艺进行热退火。

35.在其中一个实施例中,所述步骤s5中,所述第一pi层的制备过程包括:

36.s511、通过涂胶工艺,在所述衬底上旋涂一层聚酰亚胺材料,并使聚酰亚胺材料覆盖在所述电容和螺旋电感上;

37.s512、通过曝光显影的方式形成第一pi层的第一金属化孔;

38.s513、使用烘箱高温烘烤并固化第一pi层。

39.在其中一个实施例中,所述步骤s5中,所述第一金属走线的制备过程包括:

40.s521、在所述第一金属化孔中,通过pvd工艺做第三金属种籽层;

41.s522、通过电镀工艺做第一金属走线厚铜,使第一金属走线厚铜的上部能够伸入到第二pi层内;

42.s523、对第一金属走线厚铜进行cmp工艺处理;

43.s524、使用金属热退火工艺进行热退火。

44.在其中一个实施例中,所述步骤s5中,所述第二pi层的制备过程包括:

45.s531、通过涂胶工艺,在所述第一pi层上旋涂一层聚酰亚胺材料;

46.s532、通过曝光显影的方式形成第二pi层的第二金属化孔;

47.s533、使用烘箱高温烘烤并固化第二pi层。

48.在其中一个实施例中,所述步骤s6中,所述连接凸点的制备过程包括:

49.s61、通过pvd工艺做第四金属种籽层;

50.s62、在所述第二金属化孔内,通过pvd工艺和电镀工艺做第二金属走线9;

51.s63、去胶、刻蚀多余的第四金属种籽层;

52.s64、通过pvd工艺做第五金属种籽层;

53.s65、通过带胶电镀工艺,形成连接凸点;

54.s66、去胶、刻蚀多余的第五金属种籽层。

55.上述基于翘曲度及应力改善后的ipd滤波器制造方法,能够减小产品结构间的相互应力,改善ipd滤波器的翘曲度,避免切割晶圆时发生碎片等缺陷,其具有成本低,产品应力小,产品产能高等优点。

附图说明

56.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

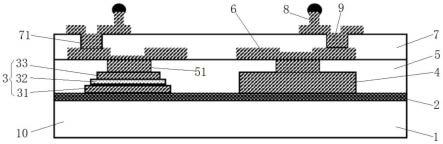

57.图1是本发明的ipd滤波器的结构示意图;

58.图2是本发明的螺旋电感的截面示意图。

具体实施方式

59.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的较佳的实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。

60.需要说明的是,当元件被称为“固定于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件。当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。

61.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。

62.参阅图1-2所示,本发明一实施例提供一种基于翘曲度及应力改善后的ipd滤波器制造方法,包括以下步骤:

63.s1、制备衬底1,并对其表面进行清洗;

64.s2、在所述衬底1上制备应力改善缓冲层2;

65.s3、在所述应力改善缓冲层2上制备电容3,所述电容3包括至下而上依次分布的下电极31、介质层32和上电极33;

66.s4、在所述应力改善缓冲层2上制备螺旋电感4;

67.s5、制备第一pi层5、第一金属走线6和第二pi层7,所述第一pi层5覆盖在所述电容3、螺旋电感4和所述衬底1上,所述第二pi层7设置在所述第一pi层5的上方,所述第一金属走线6位于所述第一pi层5和第二pi层7之间;

68.s6、在所述第二pi层7上制备连接凸点8和第二金属走线9,通过第一金属走线6和第二金属走线9使所述电容3、螺旋电感4与所述连接凸点8相导通,形成ipd滤波器本体10;本实施例中,连接凸点8可以作为倒装芯片封装的金属引线。

69.s7、对所述ipd滤波器本体10进行减薄和切割后进行封装。

70.具体地,在本发明一实施例中,所述步骤s1包括:

71.s11、制备二氧化硅玻璃衬底1;s12、用等离子体清洗所述衬底1的表面。如此,不仅

使二氧化硅玻璃衬底1的表面更加干净清洁,便于在其表面制备应力改善缓冲层2,而且,采用等离子体清洗方式具有无污染、无废水、环保、安全、可大大提高材料在后续表层加工中的粘接强度等优点。在一些实施例中,衬底1还可以为氮化镓、碳化硅等。

72.在本发明一实施例中,所述步骤s2包括:

73.s21、通过采用teos源pecvd生长sio2膜层的工艺,在所述衬底1的上表面覆盖一层2000a以上的sio2膜层;如此,通过设置的sio2膜层可以提供一定的缓冲作用,并可以改善衬底1的应力;

74.s22、通过化学抛光研磨工艺,对sio2膜层进行抛光,使其表面平坦化。如此,可以减少制备电容3和螺旋电感4时的应力。

75.在本发明一实施例中,所述步骤s3中,所述下电极31的制备过程如下:

76.s311、在所述sio2膜层的上表面通过pvd工艺做第一金属种籽层;其中,第一金属种籽层可以为ti/cu的种籽层(0.1um ti、0.3~0.5um cu);

77.s312、通过带胶电镀工艺做5~10um的铜制管脚;

78.s313、去胶并通过刻蚀工艺去除多余的第一金属种籽层,获取下电极金属膜层;

79.s314、对所述下电极金属膜层进行cmp工艺处理;如此,可以使下电极金属膜层保持较好的均匀性,也可以改变下电极金属膜层的金属表面粗糙度;

80.s315、使用金属热退火工艺进行热退火,以提高金属的平坦化,并且可以释放下电极金属膜层的应力,从而使下电极金属膜层和应力改善缓冲层2能够有效地结合,降低整体翘曲度。

81.在本发明一实施例中,所述步骤s3中,所述介质层32的制备过程如下:

82.s321、在所述下电极31的上表面通过pecvd工艺做sin膜层;

83.s322、通过光刻刻蚀工艺对sin膜层进行图形化,去除位于所述下电极31上方以外的多余sin膜层;

84.s323、通过光刻涂胶技术对sin膜层的表面做精度修整;使其保持一致性(误差

±

1nm);

85.s324、去除多余的胶残留。

86.在本发明一实施例中,所述步骤s3中,所述上电极33的制备过程如下:

87.s331、在所述介质层32的上表面通过pvd工艺做第二金属种籽层;第二金属种籽层可以为ti/cu的种籽层;

88.s332、通过带胶电镀工艺制备导电铜层,获取上电极金属膜层;其中,导电铜层的厚度可以为5-10um;

89.s333、对所述上电极金属膜层进行cmp工艺处理;如此,可以提高上电极33的均匀性和粗糙度;

90.s334、去除多余胶,使用金属热退火工艺进行热退火,提高金属层平坦化,并且可以释放上电极金属膜层的应力,从而使上电极金属膜层和介质层32能够有效地结合,降低整体翘曲度。

91.需要说明的是,本发明的步骤s4中,在所述应力改善缓冲层2上制备螺旋电感4后,可以对螺旋电感4进行cmp工艺处理,以提高螺旋电感的均匀性。

92.在本发明一实施例中,所述步骤s5中,所述第一pi层5的制备过程包括:

93.s511、通过涂胶工艺,在所述衬底1上旋涂一层10um厚度的聚酰亚胺材料(高耐温材料),并使聚酰亚胺材料覆盖在所述电容3和螺旋电感4上,其作用是:作为铜走线与工作区的分层,避免互相干扰,其次,用高耐温材料是可以更加有效地抵抗大功率器件工作导致的高温环境,避免pi层的热膨胀导致pi层发生翘曲,从而影响芯片本身的性能(第一pi层5和第二pi层7的作用相同);

94.s512、通过曝光显影的方式形成第一pi层5的第一金属化孔51;第一金属化孔51用于实现第一金属走线6的导通;

95.s513、使用烘箱高温烘烤并固化第一pi层5。

96.在本发明一实施例中,所述步骤s5中,所述第一金属走线6的制备过程包括:

97.s521、在所述第一金属化孔51中,通过pvd工艺做第三金属种籽层;其中,所述第三金属种籽层可以为tan/cu的种籽层;

98.s522、通过电镀工艺做第一金属走线厚铜,使第一金属走线厚铜的上部能够伸入到第二pi层7内;

99.s523、对第一金属走线厚铜进行cmp工艺处理,以提高第一金属走线厚铜的一致性;

100.s524、使用金属热退火工艺进行热退火,以提高第一金属走线厚铜的平坦化。

101.在本发明一实施例中,所述步骤s5中,所述第二pi层7的制备过程包括:

102.s531、通过涂胶工艺,在所述第一pi层5上旋涂一层聚酰亚胺材料(高耐温材料);

103.s532、通过曝光显影的方式形成第二pi层7的第二金属化孔71;第二金属化孔71用于实现第二金属走线9的导通;

104.s533、使用烘箱高温烘烤并固化第二pi层7。

105.在本发明一实施例中,所述步骤s6中,所述连接凸点8的制备过程包括:

106.s61、通过pvd工艺做第四金属种籽层;其中,第四金属种籽层可以为tan/cu的种籽层;

107.s62、在所述第二金属化孔71内,通过pvd工艺和电镀工艺做第二金属走线9;本实施例中,第二金属走线9的制备方法与第一金属走线6的制备方法基本相同。

108.s63、去胶、刻蚀多余的第四金属种籽层;

109.s64、通过pvd工艺做第五金属种籽层;其中,第五金属种籽层可以为ti/cu的种籽层;

110.s65、通过带胶电镀工艺,形成连接凸点8;

111.s66、去胶、刻蚀多余的第五金属种籽层。

112.在本发明一实施例中,为了便于连接,还可以在所述连接凸点8的顶部设置锡球。

113.综上所述,本发明的基于翘曲度及应力改善后的ipd滤波器制造方法,能够减小产品结构间的相互应力,改善ipd滤波器的翘曲度,避免切割晶圆时发生碎片等缺陷,其具有成本低,产品应力小,产品产能高等优点。

114.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

115.以上所述实施例仅表达了本发明的几种实施方式,但并不能因此而理解为对本发

明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1