半导体装置的制造方法和半导体装置与流程

1.本发明涉及半导体装置的制造方法以及半导体装置。

背景技术:

2.在具有多个半导体元件的半导体装置中,为了使元件间不发生电干扰而设置元件分离结构。作为设置该元件分离结构的方法,例如可举出通过在元件分离区域(有时也称为“场”)选择性形成厚的硅氧化膜(有时也称为“场氧化膜”),从而将形成于有源区域的多个元件分离的locos(local oxidation of silicon:硅的局部氧化)法。

3.作为该locos法的一例,首先,在硅半导体基板上形成氧化种难以通过且与硅相比难以充分热氧化的硅氮化膜。另外,在形成硅氮化膜之前,在硅半导体基板与硅氮化膜之间形成基底氧化膜作为应力缓冲膜。接着,通过蚀刻处理选择性去除硅氮化膜而形成掩模图案后,进行场氧化处理。由此,通过使未被硅氮化膜覆盖的硅半导体基板的表面氧化而变厚的场氧化膜来设置元件分离结构,将多个元件电分离。

4.然而,在场氧化处理时,氧化种从掩模图案的开口部通过基底氧化膜扩散到硅氮化膜之下,因此成为场氧化膜的周缘进入硅氮化膜的下方那样的结构。场氧化膜的周缘的截面形状为鸟喙那样的形状,因此有时称为“鸟嘴”。该鸟嘴有时会进入有源区域,因此使有源区域的有效面积变窄,进而对电特性造成不良影响。

5.因此,为了使氧化种不扩散到硅氮化膜之下的硅半导体基板,通过使基底氧化膜尽可能地薄,能够减小鸟嘴而确保有源区域的有效面积较大,能够配置更多的半导体元件。

6.然而,若使基底氧化膜变薄,则容易因基底氧化膜与硅氮化膜之间产生的剪切应力而在硅半导体基板产生位错。该位错的产生会导致热载流子所致的特性的劣化,有时耐久年数(器件寿命)大幅降低。

7.因此,为了缓和该剪切应力,例如提出了如下方法:将基底氧化膜的膜厚设为10nm~100nm,将对基底氧化膜进行的热处理的加热温度设为1,050℃以上,形成400nm以上的膜厚的场氧化膜(参照专利文献1)。

8.现有技术文献

9.专利文献

10.专利文献1:日本特开平5-21424号公报

技术实现要素:

11.发明所要解决的课题

12.在使基底氧化膜变薄的情况下,在专利文献1所记载的半导体装置的制造方法中,解决了因应力而产生位错从而导致耐久性降低这一点,但除此之外,在通过干式蚀刻处理来选择性去除硅氮化膜时,有时会形成称为微沟槽的微小的孔。

13.具体而言,在该干式蚀刻处理中,若对sf6等蚀刻气体施加高频电力而生成离子、自由基来选择性去除硅氮化膜,则在蚀刻面的周缘附近,尤其反应性高的自由基容易积存。

于是,有时会在周围的硅中形成伴有缺陷的微沟槽,或者即使不至于形成微沟槽,也会由于其蚀刻损伤而在硅中产生缺陷。若在这样的状态下对硅半导体基板进行场氧化,则随着场氧化膜、其鸟嘴的变形而残留硅的缺陷,由于经由该缺陷的漏电流的产生等,有时在形成于有源区域的半导体元件中无法得到所期望的电特性。

14.因此,本发明的一个方面的目的在于,提供一种半导体装置的制造方法,即使为了减小鸟嘴而使基底氧化膜变薄,也能够抑制场氧化膜及其鸟嘴的大幅变形、缺陷的产生,能够形成容易得到期望的电特性的半导体元件。

15.用于解决课题的方法

16.本发明的一个实施方式中的半导体装置的制造方法是设置有形成半导体元件的有源区域和将上述半导体元件电分离的元件分离区域的半导体装置的制造方法,其包括:

17.在硅半导体基板的表面形成基底氧化膜,

18.对于上述基底氧化膜形成厚膜部和薄膜部,上述厚膜部沿着上述有源区域与上述元件分离区域的边界设置,并且至少从上述边界向上述元件分离区域侧具有规定的宽度,上述薄膜部在上述厚膜部以外的上述有源区域以及上述元件分离区域中比上述厚膜部的膜厚薄,

19.在上述厚膜部和上述薄膜部的表面形成硅氮化膜,

20.通过过蚀刻处理选择性去除上述元件分离区域的上述硅氮化膜,

21.通过以上述有源区域的上述硅氮化膜为掩模的场氧化处理,从而在上述元件分离区域的上述硅半导体基板的表面选择性形成场氧化膜。

22.发明效果

23.根据本发明的一个方面,能够提供一种半导体装置的制造方法,即使为了减小鸟嘴而使基底氧化膜变薄,也能够抑制场氧化膜及其鸟嘴的大幅变形、缺陷的产生,能够形成容易得到期望的电特性的半导体元件。

附图说明

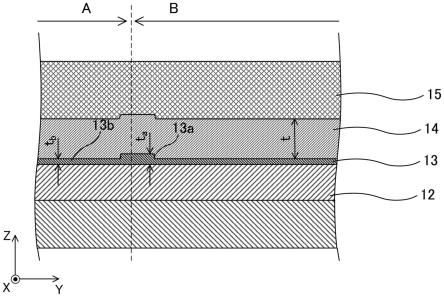

24.[图1]图1是示出第一实施方式中的半导体装置的制造方法的概略截面图。

[0025]

[图2]图2是示出第一实施方式中的半导体装置的制造方法的概略截面图。

[0026]

[图3]图3是示出第一实施方式中的半导体装置的制造方法的概略截面图。

[0027]

[图4]图4是示出第一实施方式中的半导体装置的制造方法的概略截面图。

[0028]

[图5]图5是示出第一实施方式中的半导体装置的制造方法的概略截面图。

[0029]

[图6]图6是示出第二实施方式中的半导体装置的制造方法的概略截面图。

[0030]

[图7]图7是示出第三实施方式中的半导体装置的制造方法的概略截面图。

[0031]

[图8]图8是示出以往的半导体装置的制造方法的概略截面图。

[0032]

[图9]图9是示出以往的半导体装置的制造方法的概略截面图。

[0033]

[图10]图10是示出以往的半导体装置的制造方法的概略截面图。

[0034]

[图11]图11是示出以往的半导体装置的制造方法的概略截面图。

[0035]

[图12]图12是示出以往的另一半导体装置的制造方法的概略截面图。

[0036]

[图13]图13是示出以往的另一半导体器件的示意性截面图。

[0037]

符号说明

[0038]

11:硅半导体基板,12:p型阱区域,13:基底氧化膜,13a:厚膜部,13b:薄膜部,14:硅氮化膜,15:光致抗蚀剂膜,16:场氧化膜,100:半导体装置,a:有源区域,b:元件分离区域,c:边界,t:硅氮化膜的膜厚,ta:厚膜部的膜厚,tb:薄膜部的膜厚,w:(厚膜部中的)规定的宽度,wb:(鸟嘴的)形成区域。

具体实施方式

[0039]

本发明的一个实施方式中的半导体装置的制造方法是设置有形成半导体元件的有源区域和将半导体元件电分离的元件分离区域的半导体装置的制造方法。在该半导体装置的制造方法中,首先,在硅半导体基板的表面形成基底氧化膜。接着,对于基底氧化膜,形成沿着有源区域与元件分离区域的边界设置且至少从边界向元件分离区域侧具有规定的宽度的厚膜部以及在厚膜部以外的有源区域和元件分离区域比厚膜部的膜厚薄的薄膜部。接着,在厚膜部及薄膜部的表面形成硅氮化膜,通过过蚀刻处理选择性去除元件分离区域的硅氮化膜。而且,包括通过以有源区域的硅氮化膜为掩膜的场氧化处理,从而在元件分离区域的硅半导体基板的表面上选择性形成场氧化膜的步骤。

[0040]

在该半导体装置的制造方法中,在通过使用干蚀刻的过蚀刻处理来对元件分离区域的硅氮化膜进行选择性去除时,在蚀刻容易变深的蚀刻面的周缘,即从有源区域与元件分离区域的边界向元件分离区域侧形成基底氧化膜的厚膜部。由此,即使为了减小硅半导体基板鸟嘴而减薄基底氧化膜的薄膜部,厚膜部也防止蚀刻到达硅半导体基板。因此,能够抑制场氧化膜及其鸟嘴的大幅变形、缺陷的产生,能够得到可形成容易得到所希望的电特性的半导体元件的半导体装置。

[0041]

需要说明的是,直接确定这样的鸟嘴附近的局部的硅内的缺陷的减少几乎不实际。

[0042]

在此,“过蚀刻”是指即使进行适当蚀刻也能够充分去除因“面内偏差”而残留的硅氮化膜的蚀刻。上述的“适当蚀刻”是指,去除硅氮化膜的大部分,直到等离子体内的蚀刻生成物变化而等离子体发光的光谱大幅变化为止进行的蚀刻。

[0043]

另外,“基底氧化膜”是指在硅半导体基板(或者,例如,如以下的实施方式那样形成于硅半导体基板的p型阱层)的表面形成的硅氧化膜,是指在场氧化时成为用作掩模的硅氮化膜的基底的氧化膜。该基底氧化膜一般通过热氧化法形成,但也可以是通过cvd堆积的氧化膜。进而,该基底氧化膜只要是作为硅氮化膜的基底而形成在硅半导体基板上的基底氧化膜,则可以是任意形状。

[0044]

以下,参照附图对以往的实施方式以及本发明的实施方式进行详细说明。

[0045]

需要说明的是,在附图中,对相同的构成部分标注相同的附图标记,有时省略重复的说明。另外,在附图中,x方向、y方向以及z方向相互垂直。将包含x方向和该x方向的相反方向(-x方向)的方向称为“x轴方向”,将包含y方向和该y方向的相反方向(-y方向)的方向称为“y轴方向”,将包含z方向和该z方向的相反方向(-z方向)的方向称为“z轴方向”(高度方向、厚度方向)。关于这一点,在以下的各实施方式中,有时将各膜的z方向侧的面称为“表面”。

[0046]

附图是示意性的,宽度、长度以及进深的比率等并不如附图所示。

[0047]

首先,在说明本发明的实施方式之前,进行以往的实施方式的说明。

[0048]

需要说明的是,这些实施方式都是设置有形成半导体元件的有源区域和将半导体元件电分离的元件分离区域的半导体装置的制造方法。

[0049]

图8至图10是示出以往的半导体装置的制造方法的概略截面图。在图8至图10所示的以往的制造方法中,通过使基底氧化膜尽量薄,从而在场氧化中使氧化种难以通过而不使鸟嘴变大。

[0050]

作为以往的半导体装置的制造方法,首先,如图8所示,在p型的硅半导体基板11的表面,通过杂质的注入以及热扩散而形成p型阱区域12之后,对p型阱区域12通过热氧化处理而形成膜厚t1的基底氧化膜13。

[0051]

接着,如图9所示,在基底氧化膜13的表面整个区域形成成为场氧化时的掩模的硅氮化膜14之后,在该硅氮化膜14的表面整个区域形成成为硅氮化膜蚀刻时的掩模的光致抗蚀剂膜15。

[0052]

然后,如图10所示,在元件分离区域b中,在通过曝光处理选择性去除光致抗蚀剂膜15之后,通过蚀刻处理选择性去除硅氮化膜14。

[0053]

在硅氮化膜14的蚀刻处理中,当使用干式蚀刻时,通常硅氮化膜14相对于基底氧化膜13的选择比比较小,为2~3左右。另外,考虑到硅氮化膜14的膜厚偏差以及蚀刻中的面内偏差,通过过蚀刻处理来选择性去除硅氮化膜14。此时,蚀刻面由于过蚀刻处理而到达基底氧化膜13,基底氧化膜13的膜厚成为比t1薄的t2。进而,在从该蚀刻面的周缘(即,有源区域a与元件分离区域b的边界c)起的元件分离区域b侧,自由基容易积存,蚀刻速度容易局部地变快,因此蚀刻到达p型阱区域12,形成微沟槽mt。

[0054]

具体而言,在硅氮化膜14的过蚀刻处理中,存在蚀刻面的周缘附近的蚀刻速度与蚀刻面的周缘附近以外的蚀刻速度相比成为约1.2倍的情况。

[0055]

实际上,将过蚀刻处理的条件设为一定的膜厚的基底氧化膜13的过蚀刻量为10nm,通过干蚀刻选择性去除膜厚为150nm的硅氮化膜14。于是,在蚀刻面的周缘附近22nm左右,在蚀刻面的周缘附近以外10nm左右,基底氧化膜13被过蚀刻。根据该结果,当将硅氮化膜14相对于基底氧化膜13的选择比设为2而换算成硅氮化膜14时,认为在蚀刻面的周缘附近被蚀刻了194nm~216nm左右,在周缘附近以外被蚀刻了170nm~180nm左右。因此,根据这些值可知,蚀刻面的周缘附近的蚀刻速度与蚀刻面的周缘附近以外的蚀刻速度相比约为1.2倍。

[0056]

另外,在该过蚀刻处理的条件下,从蚀刻面的周缘向元件分离区域b侧被较深地蚀刻的区域的宽度为约0.3μm。

[0057]

进而,若如图10所示在p型阱区域12中形成有微沟槽mt的状态下进行场氧化,则氧化种进行反应的面变大,因此鸟嘴16a的形成区域w

b1

变宽,并且场氧化膜16、其鸟嘴16a会变形。因此,有时在形成于有源区域a的半导体元件中无法获得所期望的电特性。

[0058]

因此,考虑通过使基底氧化膜13的膜厚足够厚,从而不在p型阱区12形成微沟槽mt。

[0059]

具体而言,如图12所示,通过将基底氧化膜13的膜厚设为比t1充分厚的t3,从而能够不在p型阱区12形成微沟槽mt。

[0060]

若在该状态下进行场氧化,则如图13所示,场氧化膜16及其鸟嘴16a就不会变形,但基底氧化膜13的膜厚t3比图10所示的基底氧化膜13的膜厚t1厚,因此氧化种容易通过基

底氧化膜13。于是,氧化种容易向硅氮化膜14之下的p型阱区域12扩散,鸟嘴16a的形成区域w

b2

变宽。

[0061]

这样,在以往的半导体装置的制造方法中,需要调整基底氧化膜13的膜厚,使得鸟嘴16a的形成区域不会变得过宽,并且场氧化膜16、其鸟嘴16a不会变形,该调整非常困难。

[0062]

因此,在本发明的实施方式中,能够提供一种半导体装置,即使为了减小鸟嘴16a而使基底氧化膜13变薄,场氧化膜16、其鸟嘴16a也不会大幅变形,能够形成容易得到期望的电特性的半导体元件100。

[0063]

(第一实施方式)

[0064]

图1至图5是示出第一实施方式的半导体装置的制造方法的概略截面图。

[0065]

第一实施方式的半导体装置100通过第一实施方式的半导体装置的制造方法来制造。在第一实施方式的半导体装置的制造方法中,设置形成半导体元件的有源区域a和将半导体元件电分离的元件分离区域b。

[0066]

以下,对该半导体装置的制造方法进行详细说明。

[0067]

在本实施方式的半导体装置的制造方法中,首先,如图1所示,在p型的硅半导体基板11的表面,通过杂质的注入以及热扩散而形成p型阱区域12之后,对p型阱区域12通过热氧化处理而形成膜厚ta的基底氧化膜13。

[0068]

接着,如图2所示,对基底氧化膜13形成厚膜部13a和薄膜部13b。

[0069]

具体而言,厚膜部13a和薄膜部13b通过如下方式形成:在形成厚膜部13a的范围内以维持膜厚为ta的状态的方式用光致抗蚀剂膜覆盖,在形成薄膜部13b的范围内以膜厚成为比ta薄的tb的方式对基底氧化膜13进行半蚀刻处理。

[0070]

厚膜部13a沿着有源区域a与元件分离区域b的边界c设置,且至少从该边界c向元件分离区域b侧具有规定的宽度w。在通过干式蚀刻来选择性去除元件分离区域b中的硅氮化膜14时,该厚膜部13a作为阻挡部发挥功能,以使得不会过度蚀刻至p型阱区域12。这是因为,在自由基容易积存的蚀刻面的周缘附近,蚀刻速度局部地变快,因此厚膜部13a以包含蚀刻面的周缘附近的方式沿着有源区域a与元件分离区域b的边界c设置。

[0071]

作为厚膜部13a的膜厚ta,只要是在选择性去除硅氮化膜14时蚀刻不会到达p型阱区域12的膜厚,就没有特别限制,可以根据目的适当选择。关于该膜厚ta,从过厚时鸟嘴的形成区域容易扩展的观点出发,优选减薄至蚀刻不到达p型阱区域12的程度。

[0072]

作为厚膜部13a的规定的宽度w,只要是在选择性去除硅氮化膜14时在蚀刻面的周缘附近被较深地蚀刻的宽度以上,就没有特别限制,可以根据目的适当选择,但优选在蚀刻面的周缘附近被较深地蚀刻的宽度。

[0073]

在本实施方式中,从能够沿着有源区域a与元件分离区域b的边界c稳定地形成厚膜部13a的观点出发,将厚膜部13a的规定的宽度w设为1μm。

[0074]

作为厚膜部13a的位置,只要能够以包含蚀刻面的周缘附近的被较深地蚀刻的区域的方式沿着有源区域a与元件分离区域b的边界c设置,就没有特别限制,能够根据目的适当选择,但优选在元件分离区域b中包含被较深地蚀刻的宽度的位置。另外,从减小鸟嘴的观点出发,优选在有源区域a中不包含厚膜部13a。

[0075]

在本实施方式中,厚膜部13a的位置设为厚膜部13a的规定的宽度w的1μm中的0.3μm包含于有源区域a中、0.7μm包含于元件分离区域b中的位置。

[0076]

薄膜部13b在厚膜部13a以外的有源区域a和元件分离区域b中具有比厚膜部13a的膜厚ta薄的膜厚tb。

[0077]

作为薄膜部13b的膜厚tb,只要是在选择性去除硅氮化膜14时蚀刻不会到达p型阱区域12的膜厚,就没有特别限制,可以根据目的适当选择,但从薄的一方在场氧化时氧化种难以通过、能够不扩散到硅氮化膜14之下的方面考虑,优选为35nm以下。另外,薄膜部13b的膜厚tb从过薄时也容易因应力而在硅半导体基板11产生位错、耐久年数降低的方面考虑,优选为20nm以上。

[0078]

若根据硅氮化膜14的膜厚来对厚膜部13a及薄膜部13b的膜厚进行研究,则考虑为了完全选择性去除硅氮化膜14而通过蚀刻比硅氮化膜14的膜厚t深1.2倍来去除的情况。在该情况下,若将硅氮化膜14相对于基底氧化膜13的选择比估计得较少而设为2,则基底氧化膜13的薄膜部13b会被蚀刻0.1t的厚度。因此,作为薄膜部13b的膜厚tb,需要设为0.1t以上。另外,由于在蚀刻面的周缘附近被较深地蚀刻为薄膜部13b的1.2倍左右,因此基底氧化膜13的厚膜部13a会被蚀刻0.22t的厚度。因此,作为厚膜部13a的膜厚ta,需要设为0.22t以上。

[0079]

具体而言,若将硅氮化膜14相对于基底氧化膜13的选择比设为2,则优选满足下式:(t+2ta)/(t+2tb)≥1.2。

[0080]

例如,若硅氮化膜14的膜厚t为150nm,则将薄膜部13b的膜厚tb设为0.1t以上,将厚膜部13a的膜厚ta设为0.22t以上,若考虑薄膜部13b的膜厚tb的优选范围为20nm≤tb≤35nm,则将厚膜部13a的膜厚ta设为39nm以上,将薄膜部13b的膜厚tb设为20nm以上。

[0081]

接下来,如图3所示,在包含厚膜部13a以及薄膜部13b的基底氧化膜13的表面整个区域通过cvd法形成硅氮化膜14之后,在硅氮化膜14的表面整个区域形成光致抗蚀剂膜15。

[0082]

硅氮化膜14的膜厚只要是成为场氧化时的掩模的膜厚即可,没有特别限制,可以根据目的适当选择,但优选选择性去除变得容易的膜厚。

[0083]

在本实施方式中,将硅氮化膜14的膜厚t设为150nm。

[0084]

接着,如图4所示,在通过曝光处理选择性去除元件分离区域b的光致抗蚀剂膜15之后,通过使用干蚀刻的过蚀刻处理,选择性去除元件分离区域b的硅氮化膜14。此时,蚀刻面的基底氧化膜13的膜厚tc比厚膜部13a的膜厚ta以及薄膜部13b的膜厚tb薄。

[0085]

接着,通过以图4所示的有源区域a的硅氮化膜14为掩模的场氧化处理,如图5所示,在元件分离区域b的p型阱区域12的表面选择性形成场氧化膜16。

[0086]

而且,在形成了场氧化膜16之后,去除有源区域a的硅氮化膜14、基底氧化膜13,在有源区域a形成mosfet等半导体元件。

[0087]

这样,在第一实施方式的半导体装置的制造方法中,蚀刻未到达p型阱区域12,不会产生微沟槽mt。因此,在该半导体装置的制造方法中,即使为了减小鸟嘴16a而使基底氧化膜13变薄,也能够抑制场氧化膜16及其鸟嘴16a的大幅变形、缺陷的产生,能够形成容易得到所希望的电特性的半导体元件。

[0088]

(第二实施方式)

[0089]

图6是示出第二实施方式中的半导体装置的制造方法的概略截面图。另外,图6示出与在第一实施方式中形成了图3所示的光致抗蚀剂膜15的状态同样的状态。

[0090]

如图6所示,第二实施方式除了第一实施方式中的厚膜部13a未延伸至有源区域a

而形成以外,与第一实施方式相同。

[0091]

由此,在第二实施方式中,由于厚膜部13a未延伸至有源区域a而形成,因此在场氧化时氧化种难以通过有源区域a的硅氮化膜14的下方,因此能够进一步减小鸟嘴。

[0092]

(第三实施方式)

[0093]

图7是示出第三实施方式中的半导体装置的制造方法的概略截面图。另外,图7示出与在第一实施方式中形成了图3所示的光致抗蚀剂膜15的状态同样的状态。

[0094]

如图7所示,第三实施方式除了第一实施方式中的厚膜部13a在元件分离区域b的整个区域延伸而形成以外,与第一实施方式相同。

[0095]

由此,在第三实施方式中,由于厚膜部13a在元件分离区域b的整个区域延伸而形成,因此能够容易地进行光致抗蚀剂膜15的曝光处理以及对硅氮化膜14进行过蚀刻处理时的对位。

[0096]

如以上说明的那样,本发明的一个实施方式中的半导体装置的制造方法是设置有形成半导体元件的有源区域和将半导体元件电分离的元件分离区域的半导体装置的制造方法。在该半导体装置的制造方法中,首先,在硅半导体基板的表面形成基底氧化膜。接着,对于基底氧化膜,形成沿着有源区域与元件分离区域的边界设置且至少从边界向元件分离区域侧具有规定的宽度的厚膜部和在厚膜部以外的有源区域及元件分离区域比厚膜部的膜厚薄的薄膜部。接着,在厚膜部及薄膜部的表面形成硅氮化膜,通过过蚀刻处理选择性去除元件分离区域的硅氮化膜。而且,包括通过以有源区域的硅氮化膜为掩膜的场氧化处理,从而在元件分离区域的硅半导体基板的表面上选择性形成场氧化膜的步骤。

[0097]

由此,能够提供一种半导体装置,即使为了减小鸟嘴而使基底氧化膜变薄,也能够抑制场氧化膜及其鸟嘴的大幅变形、缺陷的产生,能够形成容易得到所希望的电特性的半导体元件。

[0098]

以上,基于本发明的各实施方式具体地进行了说明,但本发明并不限定于此前记载的实施方式,在不脱离其主旨的范围内能够进行各种变更。

[0099]

例如,在上述的各实施方式中,在p型的硅半导体基板之上形成了p型阱区域,但不限于此,也可以都设为n型,也可以将任意一个设为n型。

[0100]

另外,在上述的各实施方式中,形成了p型阱区,但不限于此,也可以不形成p型阱区。

[0101]

进一步,在上述的各实施方式中,通过半蚀刻处理形成厚膜部以及薄膜部,但不限于此,也可以通过场氧化处理形成厚膜部。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1