主动元件基板及其制造方法与流程

1.本发明涉及一种主动元件基板及其制造方法。

背景技术:

2.由于包含金属氧化物半导体的薄膜晶体管易受到环境中的氧气、氢气和水的影响,使其在长时间使用之后,容易出现性能衰退,影响薄膜晶体管的电性。举例来说,在包含薄膜晶体管阵列的显示装置中,若部分的薄膜晶体管的金属氧化物半导体出现性能衰退,容易使显示装置所显示的画面产生不均匀(mura)的问题。一般来说,为了减少这种不均匀的问题,会将像素电路连接至外部芯片,并通过外部补偿存储器存储大量的电流信息。前述电流信息经演算法演算以得到补偿电流或电压,再将补偿电流或电压回馈至像素电路中。然而,外部芯片的电路设计复杂,且成本高。

技术实现要素:

3.本发明提供一种主动(有源)元件基板,能节省外部存储器的生产成本。

4.本发明提供一种主动元件基板制造方法,能节省外部存储器的生产成本。

5.本发明的至少一实施例提供一种主动元件基板。主动元件基板包括基板、第一半导体元件以及第二半导体元件。第一半导体元件以及第二半导体元件设置于基板之上。第一半导体元件包括第一栅极、第一半导体层、第一源极以及第一漏极。第一栅极与第一半导体层之间夹有栅介电结构。栅介电结构包括栅介电层的一部分与铁电材料层的一部分的堆叠。第一源极以及第一漏极电连接至第一半导体层。第二半导体元件电连接至第一半导体元件,且包括第二栅极、第二半导体层、第二源极以及第二漏极。第二栅极与第二半导体层之间夹有铁电材料层的另一部分。第二源极以及第二漏极电连接至第二半导体层。

6.本发明的至少一实施例提供一种主动元件基板的制造方法,包括:形成第一半导体层以及第二半导体层于基板之上;形成栅介电层于第一半导体层上;形成铁电材料层于栅介电层以及第二半导体层上;形成第一栅极以及第二栅极于铁电材料层上,其中栅介电层位于第一栅极与第一半导体层之间,且铁电材料层位于第一栅极与第一半导体层之间以及第二栅极与第二半导体层之间;形成电连接至第一半导体层的第一源极以及第一漏极;形成电连接至第二半导体层第二源极以及第二漏极。

附图说明

7.图1是本发明的一实施例的一种主动元件基板的剖面示意图;

8.图2a至图2f是图1的主动元件基板的制造方法的剖面示意图;

9.图3是本发明的一实施例的一种主动元件基板的剖面示意图;

10.图4a至图4d是图3的主动元件基板的制造方法的剖面示意图;

11.图5是本发明的一实施例的一种像素电路的等效电路示意图;

12.图6是本发明的一实施例的一种显示装置在图5的像素电路设置下的像素补偿操

作流程图。

13.符号说明

14.10,20:主动(有源)元件基板

15.100:基板

16.102:缓冲层

17.112,112’:第一半导体层

18.112a:第一源极区

19.112b:第一沟道区

20.112c:第一漏极区

21.114,114’:第二半导体层

22.114a:第二源极区

23.114b:第二沟道区

24.114c:第二漏极区

25.116,116’:第三半导体层

26.116a:第三源极区

27.116b:第三沟道区

28.116c:第三漏极区

29.120:栅介电层

30.122:第一栅介电图案

31.124:第二栅介电图案

32.140:铁电材料层

33.142:第一铁电材料图案

34.144:第二铁电材料图案

35.150:层间介电层

36.a:第一节点

37.b:第二节点

38.c:第三节点

39.cst:存储电容

40.d1:第一漏极

41.d2:第二漏极

42.d3:第三漏极

43.el:发光元件

44.g1:第一栅极

45.g2:第二栅极

46.g3:第三栅极

47.gi:栅介电结构

48.nd:法线方向

49.o1,o2,o3,o4,o5,o6,op:开口

50.px:像素电路

51.s1:第一源极

52.s2:第二源极

53.s3:第三源极

54.t1:第一半导体元件

55.t2:第二半导体元件

56.t3:第三半导体元件

[0057]vs1

,v

data

,v

dd

,v

s2

,v

sus

,v

ss

:电压

具体实施方式

[0058]

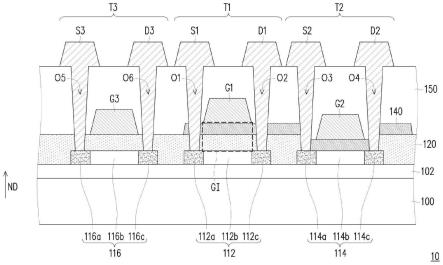

图1是依照本发明的一实施例的一种主动元件基板的剖面示意图。

[0059]

请参考图1,主动元件基板10包括基板100、第一半导体元件t1以及第二半导体元件t2。在本实施例中,主动元件基板10还包括第三半导体元件t3以及缓冲层102。在一些实施例中,第二半导体元件t2通过附图中未绘示的导电构件而电连接至第一半导体元件t1。在一些实施例中,第二半导体元件t2通过附图中未绘示的导电构件而电连接至第三半导体元件t3。在一些实施例中,第三半导体元件t3通过附图中未绘示的导电构件而电连接至第一半导体元件t1。

[0060]

基板100的材质可为玻璃、石英、有机聚合物或是不透光/反射材料(例如:导电材料、金属、晶片、陶瓷或其他可适用的材料)或是其他可适用的材料。若使用导电材料或金属时,则在第一基板100上覆盖一层绝缘层(未绘示),以避免短路问题。在一些实施例中,基板100为软性基板,且基板100的材料例如为聚乙烯对苯二甲酸酯(polyethylene terephthalate,pet)、聚二甲酸乙二醇酯(polyethylene naphthalate,pen)、聚酯(polyester,pes)、聚甲基丙烯酸甲酯(polymethylmethacrylate,pmma)、聚碳酸酯(polycarbonate,pc)、聚酰亚胺(polyimide,pi)或金属软板(metal foil)或其他可挠性材质。缓冲层102位于基板100上,缓冲层102的材质可以包括氮化硅、氧化硅、氮氧化硅或其他合适的材料或上述材料的堆叠层,但本发明不以此为限。

[0061]

第一半导体元件t1、第二半导体元件t2以及第三半导体元件t3设置于基板100以及缓冲层102之上。第一半导体元件t1包括第一栅极g1、第一半导体层112、第一源极s1以及第一漏极d1。第二半导体元件t2包括第二栅极g2、第二半导体层114、第二源极s2以及第二漏极d2。第三半导体元件t3包括第三栅极g3、第三半导体层116、第三源极s3以及第三漏极d3。

[0062]

第一半导体层112、第二半导体层114以及第三半导体层116设置于基板100与缓冲层102上。第一半导体层112包括第一源极区112a、第一漏极区112c及位于第一源极区112a与第一漏极区112c之间的第一沟道区112b。第二半导体层114包括第二源极区114a、第二漏极区114c及位于第二源极区114a与第二漏极区114c之间的第二沟道区114b。第三半导体层116包括第三源极区116a、第三漏极区116c及位于第三源极区116a与第三漏极区116c之间的第三沟道区116b。

[0063]

第一栅极g1在基板100的顶面的法线方向nd上重叠于第一半导体层112的第一沟道区112b,且第一栅极g1与第一半导体层112之间夹有栅介电结构gi。栅介电结构包括栅介电层120的一部分与铁电材料层140的一部分的堆叠。栅介电层120覆盖第一半导体层112的

上表面与侧壁,且铁电材料层140位于栅介电层120的上表面。

[0064]

第二栅极g2在基板100的顶面的法线方向nd上重叠于第二半导体层114的第二沟道区114b,且第二栅极g2与第二半导体层114之间夹有铁电材料层140的另一部分。栅介电层120覆盖第二半导体层116的侧壁,且铁电材料层140接触第二半导体层114的上表面。在一些实施例中,铁电材料层140自第一栅极g1与栅介电层120之间连续地延伸至第二栅极g2以及第二半导体层114之间。

[0065]

第三栅极g3在基板100的顶面的法线方向nd上重叠于第三半导体层116的第三沟道区116b,且第三栅极g3与第三半导体层116之间夹有栅介电层120的另一部分。栅介电层120覆盖第三半导体层116的上表面与侧壁。

[0066]

在一些实施例中,第一栅极g1与第一半导体层112之间的距离大于第二栅极g2与第二半导体层114之间的距离以及第三栅极g3与第三半导体层116之间的距离。

[0067]

在一实施例中,第一半导体层112、第二半导体层114以及第三半导体层116的材料包括单晶硅、多晶硅、微晶硅、有机半导体材料、金属氧化物半导体材料(例如:氧化铟镓锌(igzo)、氧化铟锡锌(itzo)、氧化铝锌锡(azto)、氧化铟钨锌(iwzo)等四元金属化合物或包含镓(ga)、锌(zn)、铟(in)、锡(sn)、铝(al)、钨(w)中的任三者的三元金属构成的氧化物)或其他合适的材料。在一些实施例中,第一半导体层112、第二半导体层114以及第三半导体层116包括成分相同或不同的材料。在一些实施例中,第一半导体层112、第二半导体层114以及第三半导体层116包括相同或不同的厚度。

[0068]

在一实施例中,第一栅极g1、第二栅极g2以及第三栅极g3的材料可包括金属,例如铬(cr)、金(au)、银(ag)、铜(cu)、锡(sn)、铅(pb)、铪(hf)、钨(w)、钼(mo)、钕(nd)、钛(ti)、钽(ta)、铝(al)、锌(zn)或上述金属的任意组合的合金或上述金属及/或合金的叠层,但本发明不以此为限。第一栅极g1、第二栅极g2以及第三栅极g3也可以使用其他导电材料,例如:金属的氮化物、金属的氧化物、金属的氮氧化物、金属与其它导电材料的堆叠层或是其他具有导电性质的材料。在一些实施例中,第一栅极g1、第二栅极g2以及第三栅极g3包括成分相同或不同的材料。在一些实施例中,第一栅极g1、第二栅极g2以及第三栅极g3包括相同或不同的厚度。

[0069]

在一些实施例中,栅介电层120的材料例如为氧化硅、氮化硅、氮氧化硅或其他合适的材料。在一些实施例中,栅介电层120的厚度为50纳米至100纳米。

[0070]

在一些实施例中,铁电材料层140的材料包括ni

x

mgyzn

0.98-y

o或hfzzr

1-z

o2,其中x为0.01至0.05,y为0.05至0.15,z为0.4至0.6。在一些实施例中,铁电材料层140的厚度为5纳米至50纳米。

[0071]

层间介电层150设置于第一栅极g1、第二栅极g2、第三栅极g3、铁电材料层140以及栅介电层120之上,且覆盖第一栅极g1、第二栅极g2、第三栅极g3、铁电材料层140以及栅介电层120。层间介电层150的材料例如为氧化硅、氮化硅、氮氧化硅或其他合适的材料。

[0072]

层间介电层150、铁电材料层140以及栅介电层120中的开口o1、o2分别重叠于第一源极区112a及第一漏极区112c。第一源极s1与第一漏极d1位于层间介电层150上,且分别填入开口o1、o2以电连接至第一半导体层112的第一源极区112a及第一漏极区112c。

[0073]

层间介电层150、铁电材料层140以及栅介电层120中的开口o3、o4分别重叠于第二源极区114a及第二漏极区114c。第二源极s2与第二漏极d2位于层间介电层150上,且分别填

入开口o3、o4以电连接至第二半导体层114的第二源极区114a及第二漏极区114c。

[0074]

需注意的是,虽然在图1中,铁电材料层140被第一源极s1、第一漏极d1、第二源极s2以及第二漏极d2分隔成多个区块,但铁电材料层140实际上为连续的结构。换句话说,铁电材料层140环绕第一源极s1、第一漏极d1、第二源极s2以及第二漏极d2,且第一源极s1、第一漏极d1、第二源极s2以及第二漏极d2穿过铁电材料层140。

[0075]

层间介电层150以及栅介电层120中的开口o5、o6分别重叠于第三源极区116a及第三漏极区116c。第三源极s3与第三漏极d3位于层间介电层150上,且分别填入开口o5、o6以电连接至第三半导体层116的第三源极区116a及第三漏极区116c。

[0076]

在一实施例中,第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3与第三漏极d3的材料可包括金属,例如铬、金、银、铜、锡、铅、铪、钨、钼、钕、钛、钽、铝、锌或上述金属的任意组合的合金或上述金属及/或合金的叠层,但本发明不以此为限。第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3与第三漏极d3也可以使用其他导电材料,例如:金属的氮化物、金属的氧化物、金属的氮氧化物、金属与其它导电材料的堆叠层或是其他具有导电性质的材料。在一些实施例中,第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3与第三漏极d3包括成分相同或不同的材料。在一些实施例中,第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3与第三漏极d3包括相同或不同的厚度。

[0077]

基于上述,第一半导体元件t1的第一栅极g1与第一半导体层112之间的栅介电结构gi包括栅介电层120与铁电材料层140,因此,可以通过负电容效应(negative capacitor effect)让第一半导体元件t1的次临界摆幅(sub-threshold swing)小于60mv/dec,且使得第一栅极g1与第一半导体层112之间的铁电材料层140的迟滞效应减小。此外,由于第二半导体元件t2的第二栅极g2与第二半导体层116之间夹有铁电材料层140,因此,第二半导体元件t2除了可以作为驱动元件以外,还具有存储电流信息或电压信息的功能。最后,第三半导体元件t3的第一栅极g1与第一半导体层112之间夹有栅介电层120,可以提供稳定的正向或反向电流。

[0078]

图2a至图2f是图1的主动元件基板10的制造方法的剖面示意图。

[0079]

请参考图2a,形成第一半导体层112’、第二半导体层114’以及第三半导体层116’于基板100之上。在本实施例中,第一半导体层112’、第二半导体层114’以及第三半导体层116’形成于缓冲层102上。在一些实施例中,形成第一半导体层112’、第二半导体层114’以及第三半导体层116’的方法包括以下步骤:首先,在基板110及缓冲层102上形成毯覆的半导体材料层(未绘示);接着,利用光刻制作工艺,在半导体材料层上形成图案化光致抗蚀剂(未绘示);继之,利用图案化光致抗蚀剂作为掩模,来对半导体材料层进行湿式或干式蚀刻制作工艺,以形成第一半导体层112’、第二半导体层114’以及第三半导体层116’;之后,移除图案化光致抗蚀剂。换句话说,第一半导体层112’、第二半导体层114’以及第三半导体层116’例如为同时形成。

[0080]

请参考图2b,形成栅介电层120于第一半导体层112’以及第三半导体层116’上。在一些实施例中,形成栅介电层120的方法包括以下步骤:首先,在第一半导体层112’、第二半导体层114’、第三半导体层116’以及缓冲层102上形成毯覆的介电材料层(未绘示);接着,利用光刻制作工艺,在介电材料层上形成图案化光致抗蚀剂(未绘示);继之,利用图案化光

致抗蚀剂作为掩模,来对介电材料层进行湿式或干式蚀刻制作工艺,以形成包括开口op的栅介电层120,其中开口op暴露出第二半导体层114’;之后,移除图案化光致抗蚀剂。在一些实施例中,开口op的长度小于第二半导体层114’的长度,且栅介电层120覆盖第二半导体层114’的侧壁以及部分表面。在一些实施例中,开口op的长度大于第二半导体层114’的长度,且栅介电层120不接触第二半导体层114’。在一些实施例中,栅介电层120的材料可为不含氢的氧化物,由此避免栅介电层120中的氢原子在制作工艺中扩散至第一半导体层112’、第二半导体层114’以及第三半导体层116’中。

[0081]

请参考图2c,形成铁电材料层140于栅介电层120以及第二半导体层114’上。铁电材料层140填入栅介电层120的开口op中以接触第二半导体层114’。在一些实施例中,形成铁电材料层140的方法包括以下步骤:首先,在栅介电层120以及第二半导体层114’上形成毯覆的铁电材料层(未绘示);接着,利用光刻制作工艺,在铁电材料层上形成图案化光致抗蚀剂(未绘示);继之,利用图案化光致抗蚀剂作为掩模,来对铁电材料层进行湿式或干式蚀刻制作工艺,以形成不重叠于第三半导体层116’的铁电材料层140;之后,移除图案化光致抗蚀剂。

[0082]

请参考图2d,形成第一栅极g1以及第二栅极g2于铁电材料层140上,且形成第三栅极g3于栅介电层120上。栅介电层120位于第一栅极g1与第一半导体层112之间以及第三栅极g3与第三半导体层116之间,铁电材料层140位于第一栅极g1与第一半导体层112之间以及第二栅极g2与第二半导体层114之间。在一些实施例中,形成第一栅极g1、第二栅极g2以及第三栅极g3的方法包括以下步骤:首先,在栅介电层120以及铁电材料层140上形成毯覆的导电材料层(未绘示);接着,利用光刻制作工艺,在导电材料层上形成图案化光致抗蚀剂(未绘示);继之,利用图案化光致抗蚀剂作为掩模,来对导电材料层进行湿式或干式蚀刻制作工艺,以形成第一栅极g1、第二栅极g2以及第三栅极g3;之后,移除图案化光致抗蚀剂。换句话说,第一栅极g1、第二栅极g2以及第三栅极g3例如为同时形成。

[0083]

接着,以第一栅极g1、第二栅极g2以及第三栅极g3为掩模,对第一半导体层112’、第二半导体层114’以及第三半导体层116’进行掺杂制作工艺p,以形成包括第一源极区112a、第一沟道区112b与第一漏极区112c的第一半导体层112、包括第二源极区114a、第二沟道区114b与第二漏极区114c的第二半导体层114’以及包括第三源极区116a、第三沟道区116b与第三漏极区116c的第三半导体层116。在一些实施例中,掺杂制作工艺p包括氢等离子体制作工艺或离子注入制作工艺。

[0084]

请参考图2e,形成层间介电层150于栅介电层120以及铁电材料层140之上。在一些实施例中,层间介电层150为不含氢的绝缘层,由此避免层间介电层150中的氢原子扩散至第一半导体层112、第二半导体层114以及第三半导体层116,但本发明不以此为限。在一些实施例中,层间介电层150中含有氢原子,因此,可以通过热处理使氢原子扩散至第一半导体层112、第二半导体层114以及第三半导体层116中,以调整第一半导体层112、第二半导体层114以及第三半导体层116的电阻率。在一些实施例中,当使用层间介电层150中的氢原子进行第一半导体层112、第二半导体层114以及第三半导体层116的掺杂时,可以省略图2d的掺杂制作工艺p。

[0085]

请参考图2f,形成开口o1、o2、o3、o4、o5、o6,方法包括以下步骤:首先,利用光刻制作工艺,在层间介电层150上形成图案化光致抗蚀剂(未绘示);继之,利用图案化光致抗蚀

剂作为掩模,来进行湿式或干式蚀刻制作工艺,以于层间介电层150、铁电材料层140以及栅介电层120中形成开口o1、o2、o3、o4、o5、o6;之后,移除图案化光致抗蚀剂。

[0086]

开口o1、o2贯穿层间介电层150、铁电材料层140以及栅介电层120,以分别暴露出第一半导体层112的第一源极区112a与第一漏极区112c。开口o3、o4贯穿层间介电层150、铁电材料层140以及栅介电层120,以分别暴露出第二半导体层114的第二源极区114a与第二漏极区114c。开口o5、o6贯穿层间介电层150以及栅介电层120,以分别暴露出第三半导体层116的第三源极区116a与第三漏极区116c。

[0087]

最后请回到图1,形成第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3以及第三漏极d3于层间介电层150上。第一源极s1以及第一漏极d1分别填入开口o1、o2。第二源极s2以及第二漏极d2分别填入开口o3、o4。第三源极s3以及第三漏极d3分别填入开口o5、o6。在一些实施例中,形成第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3以及第三漏极d3的方法包括以下步骤:首先,在层间介电层150上形成毯覆的导电材料层(未绘示);接着,利用光刻制作工艺,在导电材料层上形成图案化光致抗蚀剂(未绘示);继之,利用图案化光致抗蚀剂作为掩模,来对导电材料层进行湿式或干式蚀刻制作工艺,以形成第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3以及第三漏极d3;之后,移除图案化光致抗蚀剂。换句话说,第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3以及第三漏极d3例如为同时形成。

[0088]

经过上述制作工艺后可大致上完成主动元件基板10的制作。

[0089]

图3是依照本发明的一实施例的一种主动元件基板20的剖面示意图。在此必须说明的是,图3的实施例沿用图1的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0090]

图3的主动元件基板20与图1的主动元件基板10的主要差异在于:主动元件基板20的栅介电层120对齐第一沟道区112b以及第三沟道区116b,且铁电材料层140对齐第一沟道区112b以及第二沟道区114b。

[0091]

请参考图3,栅介电层120包括第一栅介电图案122以及第二栅介电图案124,其中第一栅介电图案122以及第二栅介电图案124彼此分离。铁电材料层140包括第一铁电材料图案142以及第二铁电材料图案144,其中第一铁电材料图案142以及第二铁电材料图案144彼此分离。

[0092]

第一栅介电图案122以及第一铁电材料图案142在基板100的顶面的法线方向nd上重叠于第一栅极g1以及第一沟道区112b,且第一栅介电图案122以及第一铁电材料图案142位于第一栅极g1以及第一沟道区112b之间,并构成栅介电结构gi。第一栅介电图案122的侧壁以及第一铁电材料图案142的侧壁对齐于第一栅极g1的侧壁。

[0093]

第二铁电材料图案144在基板100的顶面的法线方向nd上重叠于第二栅极g2以及第二沟道区114b,且第二铁电材料图案144位于第二栅极g2以及第二沟道区114b之间。第二铁电材料图案144的侧壁对齐于第二栅极g2的侧壁。

[0094]

第二栅介电图案124在基板100的顶面的法线方向nd上重叠于第三栅极g3以及第三沟道区116b,且第二栅介电图案124位于第三栅极g3以及第三沟道区116b之间。第二栅介电图案124的侧壁对齐于第三栅极g3的侧壁。

[0095]

在本实施例中,栅介电层120以及铁电材料层140不重叠于第一源极区112a、第一漏极区112c、第二源极区114a、第二漏极区114c、第三源极区116a以及第三漏极区116c,因此,可以避免栅介电层120以及铁电材料层140影响第一源极区112a、第一漏极区112c、第二源极区114a、第二漏极区114c、第三源极区116a以及第三漏极区116c的掺杂浓度,也可以避免掺杂制作工艺对栅介电层120以及铁电材料层140造成的负面影响。

[0096]

图4a至图4d是图3的主动元件基板的制造方法的剖面示意图。

[0097]

请参考图4a,接续图2c的步骤,形成第一栅极g1以及第二栅极g2于铁电材料层140上,且形成第三栅极g3于栅介电层120上。接着以第一栅极g1、第二栅极g2以及第三栅极g3为掩模,图案化栅介电层120以及铁电材料层140,以形成第一栅介电图案122、第二栅介电图案124、第一铁电材料图案142以及第二铁电材料图案144。

[0098]

接着请参考图4b,以第一栅极g1、第二栅极g2以及第三栅极g3为掩模,对第一半导体层112’、第二半导体层114’以及第三半导体层116’进行掺杂制作工艺p,以形成包括第一源极区112a、第一沟道区112b与第一漏极区112c的第一半导体层112、包括第二源极区114a、第二沟道区114b与第二漏极区114c的第二半导体层114’以及包括第三源极区116a、第三沟道区116b与第三漏极区116c的第三半导体层116。在一些实施例中,掺杂制作工艺p包括氢等离子体制作工艺或离子注入制作工艺。

[0099]

请参考图4c,形成层间介电层150于栅介电层120以及铁电材料层140之上。层间介电层150接触第一源极区112a、第一漏极区112c、第二源极区114a、第二漏极区114c、第三源极区116a以及第三漏极区116c。在一些实施例中,层间介电层150中含有氢原子,因此,可以通过热处理使氢原子扩散至第一半导体层112、第二半导体层114以及第三半导体层116中,以调整第一半导体层112、第二半导体层114以及第三半导体层116的电阻率。在一些实施例中,通过层间介电层150中的氢原子进行掺杂制作工艺,因此可以省略图4b的掺杂制作工艺p。

[0100]

请参考图4d,形成开口o1、o2、o3、o4、o5、o6于层间介电层150中。

[0101]

最后请回到图3,形成第一源极s1、第一漏极d1、第二源极s2、第二漏极d2、第三源极s3以及第三漏极d3于层间介电层150上。第一源极s1以及第一漏极d1分别填入开口o1、o2,以电连接至第一半导体层112的第一源极区112a与第一漏极区112c。第二源极s2以及第二漏极d2分别填入开口o3、o4,以电连接至第二半导体层114的第二源极区114a与第二漏极区114c。第三源极s3以及第三漏极d3分别填入开口o5、o6,以电连接至第三半导体层116的第三源极区116a与第三漏极区116c。

[0102]

经过上述制作工艺后可大致上完成主动元件基板20的制作。

[0103]

图5是依照本发明的一实施例的一种像素电路px的等效电路示意图。图5的像素电路px例如是前述任一实施例中的主动元件基板上的像素电路px。

[0104]

请参考图5,像素电路px包括第一半导体元件t1、第二半导体元件t2、第三半导体元件t3、存储电容cst及发光元件el。

[0105]

第一半导体元件t1可作为开关晶体管使用。第一半导体元件t1的第一栅极电连接于电压v

s1

(例如为扫描线电压),第一半导体元件t1的第一漏极(或第一源极)电连接于电压v

data

(例如为数据线电压),第一半导体元件t1的第一源极(或第一漏极)电连接于第一节点a。

[0106]

第二半导体元件t2具有驱动晶体管以及存储器的功能。第二半导体元件t2的第二栅极电连接于第一节点a。第二半导体元件t2的第二漏极电连接于电压v

dd

,第二半导体元件t2的第二源极电连接于第二节点b。

[0107]

第三半导体元件t3例如可作为感测晶体管使用。第三半导体元件t3的第三栅极电连接于电压v

s2

,第三半导体元件t3的第三漏极电连接于第三节点c,第三半导体元件t3的第三源极电连接于电压v

sus

。电压v

s2

用于控制第三半导体元件t3的开关,以通过第三半导体元件t3将驱动电流的信息传送给外部芯片。

[0108]

存储电容cst的一端电连接于第一节点a,存储电容cst的另一端电连接于第三节点c。第二节点b与第三节点c电性相连。由于第二半导体元件t2的第二栅极电连接至存储电容cst,即使关闭第一半导体元件t1,第二半导体元件t2仍可持续导通一小段时间。

[0109]

发光元件el的一端电连接于第二节点b,发光元件el的另一端电连接于电压v

ss

。发光元件el的亮度会因为通过第二半导体元件t2的驱动电流的大小不同而改变。发光元件el例如是微型发光二极管、有机发光二极管或其他发光元件。

[0110]

在本实施例中,在第一节点a处,第一半导体元件t1的第一源极(或第一漏极)、第二半导体元件t2的第二栅极以及存储电容cst的一端彼此电连接。在第二节点b处,第二半导体元件t2的第二源极以及发光元件el的一端彼此电连接。在第三节点c处,第三半导体元件t3的第三漏极以及存储电容cst的另一端彼此电连接。第三半导体元件t3的第三漏极通过第三节点c以及第二节点b而电连接至第二半导体元件t2的第二源极。

[0111]

图6是依照本发明的一实施例的一种显示装置在图5的像素电路设置下的像素补偿操作流程图。

[0112]

以下简述显示装置在像素电路px的设置下,像素补偿的操作方式,请同时参考图5及图6。首先,显示装置为关闭状态,使像素电路px在背景执行灰阶(grey level)感测。灰阶感测的方式例如是将第一半导体元件t1、第二半导体元件t2及第三半导体元件t3开启,以使通过第一半导体元件t1的驱动电压和第二半导体元件t2的驱动电流可以通过第三半导体元件t3传送给外部芯片。

[0113]

接着,外部芯片通过信号处理及演算,建立出对应模型,进而计算出对应的补偿信息。之后,再将补偿信息写入像素电路px中。举例来说,开启第一半导体元件t1以及第二半导体元件t2以及第三半导体元件t3,以将外部芯片计算出的补偿信息写入第二半导体元件t2中的铁电材料层。具体地说,通过极化第二半导体元件t2中的铁电材料层,使信息记载于第二半导体元件t2中。在一些实施例中,打开第三半导体元件t3以减少第二半导体元件t2的源极与漏极之间的电压差,或进一步使第二半导体元件t2的源极与漏极之间不具电压差。

[0114]

接着,开启显示装置。由于补偿信息已经写入第二半导体元件t2,通过第二半导体元件t2的驱动电流的大小可以被调整,进而达成像素补偿的功能。在一些实施例中,在开启显示装置时,第三半导体元件t3为关断状态。

[0115]

综上所述,本发明的第二半导体元件t2具有存储器的功能,因而不需要在外部芯片中设置补偿存储器,使整体系统简化、成本降低。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1