半导体结构的形成方法、半导体结构及存储器与流程

1.本发明涉及半导体存储器技术领域,特别涉及一种半导体结构的形成方法、半导体结构及存储器。

背景技术:

2.在行业内,经常采用钝化膜来保护底层,以避免底层受水分和移动离子的侵害。

3.但是,在制备钝化膜过程中,由于制备工艺限制,钝化膜中会含有硅氢键。在使用过程中,由于含有硅氢键的钝化膜长时间暴露在空气中,会导致水汽易于附着在钝化膜表面;之后,水汽可能通过缝隙进入到内存组件的互连层内。此时,钝化膜丧失对互连层的保护效果,这会影响内存组件的可靠性。

技术实现要素:

4.本发明公开了一种半导体结构的形成方法、半导体结构及存储器,该半导体结构的形成方法可以提升结构本身的防水隔离效果,以提升半导体结构的可靠性。

5.为达到上述目的,本发明提供以下技术方案:

6.根据本公开的第一个方面,提供了一种半导体结构的形成方法,包括:

7.提供一衬底;

8.在所述衬底上形成互连层;

9.在所述互连层上形成第一钝化层,所述第一钝化层具有氢键;

10.至少对所述第一钝化层的表面进行钝化处理,去除至少部分所述氢键,形成第二钝化层。

11.在本公开的一个实施例中,所述形成第二钝化层的方法包括:

12.去除所述第一钝化层的表面的至少部分所述氢键,在所述第一钝化层剩余未钝化处理部分上形成第二钝化层。

13.在本公开的一个实施例中,在所述第一钝化层上形成第二钝化层之后,所述方法还包括:

14.循环执行n次如下步骤,n为大于等于1的整数:

15.在所述第二钝化层上形成当前的第一钝化层;

16.对当前的所述第一钝化层的表面进行钝化处理,去除当前的所述第一钝化层表面的至少部分所述氢键,形成对应的第二钝化层。

17.在本公开的一个实施例中,所述形成第二钝化层的方法包括:

18.去除所述第一钝化层表面以及内部的至少部分氢键,将所述第一钝化层转化成所述第二钝化层。

19.在本公开的一个实施例中,在所述第一钝化层上形成第二钝化层之后,所述方法还包括:

20.循环执行n次如下步骤,n为大于等于1的整数:

21.在所述第二钝化层上形成当前的第一钝化层;

22.对当前的所述第一钝化层进行钝化处理,去除当前的所述第一钝化层表面以及内部的至少部分氢键,转化成对应的第二钝化层。

23.在本公开的一个实施例中,所述第一钝化层的厚度范围为20nm~100nm。

24.在本公开的一个实施例中,至少对所述第一钝化层的表面进行钝化处理的方法包括:

25.通过反应物与所述第一钝化层中的至少部分氢键反应、形成水;

26.去除所述水,形成所述第二钝化层。

27.在本公开的一个实施例中,至少对所述第一钝化层的表面进行钝化处理的方法包括:

28.采用形成所述第一钝化层的相同工艺,至少对所述第一钝化层的表面进行钝化处理。

29.在本公开的一个实施例中,在所述互连层上形成第一钝化层的方法包括:

30.采用等离子体增强化学的气相沉积工艺,在所述互连层上形成第一钝化层。

31.在本公开的一个实施例中,所述第一钝化层的材料包括含有氢键的氮化物或氧化物。

32.在本公开的一个实施例中,所述第一钝化层的材料为含有氢键的氮化硅,所述第二钝化层的材料为氮氧化硅。

33.在本公开的一个实施例中,至少对所述第一钝化层的表面进行钝化处理的方法包括:

34.采用等离子体增强化学的气相沉积工艺,至少对所述第一钝化层的表面进行钝化处理,其中,等离子体处理的功率范围为500w~1000w。

35.在本公开的一个实施例中,所述反应物为一氧化二氮,且所述反应物的气体流量范围为100sccm~500sccm。

36.在本公开的一个实施例中,采用等离子体增强化学的气相沉积工艺,至少对所述第一钝化层的表面进行钝化处理的方法还包括:

37.施加载气,加快所述反应物与所述第一钝化层的解离速度。

38.在本公开的一个实施例中,所述载气为氮气,所述载气的气体流量范围为5000sccm~15000sccm。

39.根据本公开的第二个方面,提供了一种半导体结构,包括:

40.衬底;

41.互连层,形成于所述衬底一侧;

42.第一钝化层,形成于所述互连层背离所述衬底一侧,且所述第一钝化层具有氢键;

43.第二钝化层,形成于所述第一钝化层背离所述互连层一侧,所述第二钝化层部分由所述第一钝化层转化形成,且所述第二钝化层内的氢键数目小于所述第一钝化层内的氢键数目。

44.根据本公开的第三个方面,提供了一种存储器,包括上述任意技术方案提供的半导体结构。

45.本公开提供的半导体结构的形成方法通过对制备形成的第一钝化层进行钝化处

理,可以至少去除第一钝化层表面的部分氢键,形成第二钝化层。需要说明的是,该第二钝化层内含有较少的氢键,可以有效防止水汽进入,从而可以对互连层形成有效保护,增强器件的可靠性。

附图说明

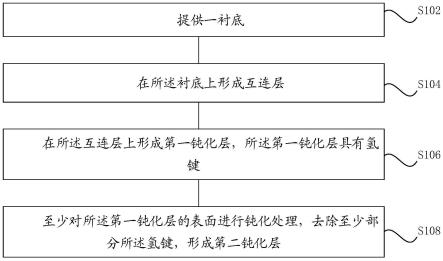

46.图1为本公开实施例提供的半导体结构的形成方法的流程图;

47.图2为对应图1中流程的膜层制备示意图;

48.图3为对应图1中流程的又一膜层制备示意图;

49.图4为本公开实施例提供的半导体结构的形成方法的工艺步骤图;

50.图5为本公开实施例提供的半导体结构的形成方法的又一工艺步骤图;

51.图6a至图6c为本公开实施例提供的半导体结构中互连层的膜层制备示意图;

52.图7为本公开实施例提供的半导体结构的膜层示意图。

53.图标:100、互连层;101、第一介质层;102、第一金属层;103、第一绝缘层;104、第二介质层;105、第二金属层;106、第二绝缘层;107、第三介质层;108、第一保护层;109、第三金属层;110、第二保护层;111、光刻胶;112、第四介质层;200、第一钝化层;201、硅氮键;202、硅氢键;203、氮氢键;300、第二钝化层;301、硅氧键;a、空气间隙。

具体实施方式

54.体现本公开特征与优点的典型实施例将在以下的说明中详细叙述。应理解的是本公开能够在不同的实施例上具有各种的变化,其皆不脱离本公开的范围,且其中的说明及附图在本质上是作说明之用,而非用以限制本公开。

55.在对本公开的不同示例性实施方式的下面描述中,参照附图进行,附图形成本公开的一部分,并且其中以示例方式显示了可实现本公开的多个方面的不同示例性结构、系统和步骤。应理解的是,可以使用部件、结构、示例性装置、系统和步骤的其他特定方案,并且可在不偏离本公开范围的情况下进行结构和功能性修改。而且,虽然本说明书中可使用术语“之上”、“之间”、“之内”等来描述本公开的不同示例性特征和元件,但是这些术语用于本文中仅出于方便,例如根据附图中的示例的方向。本说明书中的任何内容都不应理解为需要结构的特定三维方向才落入本公开的范围内。

56.第一方面,本公开实施例提供一种半导体结构的形成方法。图1为本公开实施例提供的半导体结构的形成方法的流程图;图2为对应图1中流程的膜层制备示意图;图3为对应图1中流程的又一膜层制备示意图。请结合图2和图3参考图1所示出的内容,本公开实施例提供的半导体结构的形成方法包括:

57.步骤s102:提供一衬底;

58.步骤s104:在衬底上形成互连层100;

59.步骤s106:在互连层100上形成第一钝化层200,第一钝化层200具有氢键;

60.步骤s108:至少对第一钝化层200的表面进行钝化处理,去除至少部分氢键,形成第二钝化层300。

61.具体的,本公开实施例提供的半导体结构的形成方法通过对制备形成的第一钝化层200进行钝化处理,可以至少去除第一钝化层200表面的部分氢键,形成第二钝化层300。

62.需要说明的是,采用本公开实施例提供的形成方法制备的半导体结构中,第二钝化层300内含有较少的氢键,可以有效防止水汽进入,从而可以对互连层100形成有效保护,增强器件的可靠性。

63.值得注意的是,本公开实施例提供的半导体结构的形成方法中,可以仅对第一钝化层200的表面进行钝化处理,还可以对第一钝化层200整体进行钝化处理。

64.在一个实施例中,本公开实施例提供的半导体结构的形成方法中,步骤s108中,形成第二钝化层300的方法包括:

65.去除第一钝化层200的表面的至少部分氢键,在第一钝化层200剩余未钝化处理部分上形成第二钝化层300。

66.需要说明的是,第一钝化层200的表层部分经钝化处理,在钝化处理过程中至少部分氢键被去除,可以减少外部环境中水汽进入互连层100的可能性,以提升对互连层100的防护效果。

67.而且,在该方法中仅沉积、制备一次第一钝化层200和第二钝化层300,可以简化制备工艺、提升制备效率。

68.在一种具体的实施方式中,在对第一钝化层200进行钝化处理过程中,形成的第二钝化层300的厚度大于第一钝化层200中被处理的表层厚度。当然,也可能形成的第二钝化层300的厚度等于第一钝化层200中被处理的表层厚度,具体可以根据需求进行设置,在此不再赘述。

69.在一个实施例中,步骤s108中,在第一钝化层200上形成第二钝化层300之后,本公开实施例提供的半导体结构的形成方法还包括:

70.循环执行n次如下步骤,n为大于等于1的整数:

71.在第二钝化层300上形成当前的第一钝化层200;

72.对当前的第一钝化层200的表面进行钝化处理,去除当前的第一钝化层200表面的至少部分氢键,形成对应的第二钝化层300。

73.示例性的,以n为1为例,在完成步骤s108、制备形成首个第二钝化层300后,还可以在首个第二钝化层300上再次制备形成第一钝化层200,以及,对该第一钝化层200进行钝化处理,以形成新的第二钝化层300。

74.应理解,倘若以一个第一钝化层200和由其制备形成的第二钝化层300为一个钝化层组,互连层100上可以堆叠有多个钝化层组,且该钝化层组的数目为n+1。

75.需要说明的是,本实施例中,多个第一钝化层200和多个第二钝化层300堆叠设置,且每个第一钝化层200均经过钝化处理,该形成方式可以改善互连层100表面钝化结构(若干第一钝化层200和第二钝化层300形成)的整体状态,使得钝化结构内部含有较少的氢键,从而可以更好地防止水汽进入到半导体结构内部,从而提升器件的可靠性。

76.当然,本公开实施例提供的半导体结构的形成方法中,还可以制备多层第一钝化层200,仅某些层的第一钝化层200进行钝化处理,形成相应的第二钝化层300,具体可以根据需求进行设置,在此不再赘述。应理解,“多层”指至少两层。

77.在另一个实施例中,步骤s108中,形成第二钝化层300的方法包括:

78.去除第一钝化层200表面以及内部的至少部分氢键,将第一钝化层200转化成第二钝化层300。

79.需要说明的是,第一钝化层200整体经钝化处理,在钝化处理过程中至少部分氢键被去除,可以减少外部环境中水汽进入互连层100的可能性,提升对互连层100的防护效果。

80.而且,在该方法中仅沉积、制备一次第一钝化层200和第二钝化层300,可以简化制备工艺、提升制备效率。

81.在一种具体的实施方式中,在对第一钝化层200进行钝化处理过程中,形成的第二钝化层300的厚度小于第一钝化层200的厚度。当然,也可能形成的第二钝化层300的厚度等于第一钝化层200中被处理的表层厚度,具体可以根据需求进行设置,在此不再赘述。

82.在一个实施例中,步骤s108中,在第一钝化层200上形成第二钝化层300之后,本公开实施例提供的半导体结构的形成方法还包括:

83.循环执行n次如下步骤,n为大于等于1的整数:

84.在第二钝化层300上形成当前的第一钝化层200;

85.对当前的第一钝化层200进行钝化处理,去除当前的第一钝化层22表面以及内部的至少部分氢键,转化成对应的第二钝化层300。

86.示例性的,以n为1为例,在完成步骤s108、在制备形成首个第二钝化层300后,还可以在首个第二钝化层300上再次制备形成放置第一钝化层200,以及,对该第一钝化层200进行钝化处理,以形成新的第二钝化层300。

87.应理解,该实施例中每个第一钝化层200转化为第二钝化层300,互连层100上可以堆叠有多个第二钝化层300,第二钝化层300的数目为n+1。

88.需要说明的是,本实施例中,多个第二钝化层300堆叠设置,具体的,每个第一钝化层200均经过钝化处理转化为第二钝化层300,该形成方式可以改善互连层100表面钝化结构(多个第二钝化层300形成)的整体状态,使得钝化结构内部含有较少的氢键,从而可以更好地防止水汽进入到半导体结构内部,从而提升器件的可靠性。

89.当然,本公开实施例提供的半导体结构的形成方法中,还可以制备多层第一钝化层200,仅对某层第一钝化层200进行钝化处理,形成相应的第二钝化层300,具体可以根据需求进行设置,在此不再赘述。应理解,“多层”指至少两层。

90.在一个实施例中,第一钝化层200的厚度范围为20nm~100nm。

91.需要说明的是,倘若第一钝化层200的厚度过大会导致最后形成的钝化结构的整体厚度过大,影响半导体结构的整体尺寸;倘若第一钝化层200的厚度过小,会导致最后形成的钝化结构的整体厚度过小,无法对互连层100形成有效保护。

92.因而,当设置第一钝化层200的厚度在上述范围内时,可以较好的平衡半导体结构整体尺寸以及对互连层100的防护效果两点。示例性的,第一钝化层200的厚度可以设置为以下任意数值中的一个:

93.20nm、25nm、30nm、25nm、40nm、45nm、50nm、55nm、60nm、65nm、70nm、75nm、80nm、85nm、90nm、95nm、100nm。

94.此外,值得注意的是,当钝化结构仅由一层第二钝化层300形成时,第一钝化层200的厚度范围可以大一些,以保障钝化结构的防护效果。

95.在一个实施例中,步骤s108中,至少对第一钝化层200的表面进行钝化处理的方法包括:

96.通过反应物与第一钝化层200中的至少部分氢键反应、形成水;

97.去除水,形成第二钝化层300。

98.需要说明的是,该方法可以将第一钝化层200中的氢键打破,以形成水。值得注意的是,在钝化处理过程中,由于处理温度等因素影响,可以将水直接去除,该形成方式使得钝化处理之后的第二钝化层300中仅含有少量氢键,可以避免钝化处理之后形成的产物受环境因素等影响无法有效隔绝水,从而可以提升钝化结构对互连层100的防护效果,以及提升器件的可靠性。

99.具体的,在至少对第一钝化层200的表面进行钝化处理时,可以采用多种工艺实现。示例性的,可以采用沉积工艺,具体的,主要有气相沉积法(chemical vapor deposition,cvd)或者原子层沉积(atomic layer deposition,ald)等沉积工艺。

100.应理解,气相沉积法主要是利用含有薄膜元素的一种或几种气相化合物或单质、在衬底表面上进行化学反应生成薄膜的方法;原子层沉积可以理解为一种变相的cvd工艺,通过将气相前驱体脉冲交替地通入反应器并在沉积基体上化学吸附并反应形成沉积膜的一种方法。

101.在一个实施例中,步骤s108中,至少对第一钝化层200的表面进行钝化处理的方法包括:

102.采用形成第一钝化层200的相同工艺,至少对第一钝化层200的表面进行钝化处理。

103.需要说明的是,当采用制备第一钝化层200的同一工艺进行钝化处理时,第一钝化层200的制备以及钝化处理过程可以在同一设备中进行,可以降低制备难度,加快本公开实施例提供的半导体结构的制备进程。

104.值得注意的是,制备形成第一钝化层200的方式也存在多种,示例性的,可以采用沉积工艺,具体的,主要有pvd、cvd或者ald等气相沉积工艺。

105.在一个实施例中,在互连层100上形成第一钝化层200的方法包括:

106.采用等离子体增强化学的气相沉积工艺,在互连层100上形成第一钝化层200。

107.应理解,等离子体增强化学的气相沉积法(plasma enhanced chemical vapor deposition,pecvd)是借助微波或射频等使含有薄膜成分原子的气体电离,在局部形成等离子体,而等离子体化学活性很强,很容易发生反应,在基片上沉积出所期望的薄膜。为了使化学反应能在较低的温度下进行,利用了等离子体的活性来促进反应。

108.实验机理:是借助微波或射频等使含有薄膜组成原子的气体,在局部形成等离子体,而等离子体化学活性很强,很容易发生反应,在基片上沉积出所期望的薄膜。

109.需要说明的是,pecvd工艺在制备过程中基本温度低,可以降低对温度的需求,降低制备难度,且沉积速率快,可以加快第一钝化层200的制备速率,提升制备效率。

110.此外,采用pecvd制备的第一钝化层200,膜层质量好,针孔较少,不易龟裂。

111.值得注意的是,第一钝化层200的材料存在多种可能,在一个实施例中,第一钝化层200的材料为含有氢键的氮化物、含有氢键的氧化物或含有氢键的氮碳化物中的一种。

112.需要说明的是,含有氢键的氮化物、含有氢键的氧化物或含有氢键的氮碳化物在钝化处理后形成的第二钝化层300可以对互连层100形成较好的防护效果。

113.示例性的,该第一钝化层200可以为氧化硅、氮化硅、氮氧化硅等。

114.在一个具体的实施例中,可以选取设定的第二钝化层300为含氧氢键的氮化硅,第

二钝化层300的材料为氮氧化硅。

115.需要说明的是,氮化硅薄膜具有良好的防水及防移动离子迁移的能力,可以提升对互连层100的防护效果。

116.示例性的,在采用pecvd制备氮化硅过程中,可以使用硅烷(sih4)与氨气(nh3)或氮气(n2)在氩气等离子体状态下反应,反应式如下:

117.3sih4+4

→

sin4+12h2;

118.由于pecvd制作的氮化硅往往是非化学配比的,含有相当数量的氢原子(10%~30%)。因此,有时氮化硅的化学表示式写为si

xnyhz

。

119.在一个实施例中,步骤s108中,至少对第一钝化层200的表面进行钝化处理的方法包括:

120.采用等离子体增强化学的气相沉积工艺,至少对第一钝化层200的表面进行钝化处理,其中,等离子体处理的功率范围为500w~1000w。

121.值得注意的是,在采用pecvd制备第一钝化层200后,可以在该同一设备中进行钝化处理过程,以降低制备难度,加快本公开实施例提供的半导体结构的制备进程。

122.需要说明的是,控制等离子体处理的功率范围为500w~1000w,可以提升钝化处理之后、所得的钝化层300的膜层品质,从而可以提升制备所得的第二钝化层300的防护效果,以保证半导体结构的可靠性。

123.当然,第一钝化层200的制备与钝化处理过程可以采用不同工艺,在不同设备中进行,具体可以根据需求进行设置,在此不再赘述。

124.在一个实施例中,反应物为一氧化二氮(n2o),且反应物的气体流量范围为100sccm~500sccm。

125.需要说明的是,n2o气体可以与第一钝化层200内的氢键反应、形成水蒸气,且该制备形成的水蒸气可以在制备过程中挥发,并不会影响互连层100。同时,制备所得的第二钝化层300内含有较少的氢键,可以有效防止水汽进入,从而可以对互连层100形成有效保护,增强器件的可靠性。

126.示例性的,形成于互连层100表面的第一钝化层200如图2所示,具体的,第一钝化层200内具有较多的硅氮键201,且具有一些硅氢键202(si-h)和氮氢键203(n-h);在对第一钝化层200进行钝化处理后形成的钝化层300如图3所示出,具体的,相比图2中所示出的第一钝化层200,第二钝化层300整体厚度增加,同时,第二钝化层300内增加了硅氧键301(si-o)。应理解,如图2中硅氢键202(si-h)和氮氢键203(n-h)内均含有氢键。

127.值得注意的是,如图4所示出的第二钝化层300中,第二钝化层300内部的氢键减少,可以有效防止水汽进入,从而可以对互连层100形成有效保护,增强器件的可靠性。

128.当然,本公开实施例提供的半导体结构的形成方法中,第一钝化层200内的硅氮键201、硅氢键202和氮氢键203数目并不限于图2所示出的数目,图2中仅为示意性说明。同样的,制备所得的第二钝化层300结构并不限于图3所示出的结构,图3中仅为示例性说明。

129.在一个实施例中,采用等离子体增强化学的气相沉积工艺,至少对第一钝化层200的表面进行钝化处理的方法还包括:

130.施加载气,加快反应物与第一钝化层200的解离速度。

131.需要说明的是,n2气体可以加快解离速度,以提升对第一钝化层200的钝化处理效

率,从而加快本公开实施例提供的半导体结构的制备过程。

132.在一个具体的实施例中,载气为氮气,载气的气体流量范围为5000sccm~15000sccm。

133.示例性的,在采用n2o或n2气体钝化处理第一钝化层200时,具体反应过程如下:

134.si

xnyhz

+n2o+n2+e

‑→

sianboc+h2o+e-135.应理解,x、y、z以及a、b、c均为正整数,具体数值可以根据需求进行设定,以产生相应的产物。

136.值得注意的是,在上述第一钝化层200的钝化处理过程中,氮化硅中的氢键逐步反应,生成水蒸气,该水蒸气会挥发,并不会影响互连层100,因而可以保证半导体结构的结构稳定性。

137.为了进一步说明上述反应过程,sixnyhz的分子式如下:

[0138][0139]

值得注意的是,si

xnyhz

中包含n-h键和si-h键,结合图2和图3,现将具体反应步骤进行拆分,具体如下:

[0140]

n2o+e

‑→

n2+o

[0141]

n2+e

‑→

n+n+e-[0142]

n-h+n+o

→

n2+h2o

[0143]

si-hz+n+o

→

sianboc+h2o

[0144]

具体的,首先,n2o和电子反应,生成n2和氧原子;之后,n2和电子反应生成氮原子和电子;之后,氮化硅内的n-h键与氮原子和氧原子反应,生成氮气和水;同时,硅氢键202与氮原子还有氧原子反应,生成sianboc,即含氧化型氮化硅。

[0145]

当然,还可以采用sih4和n2制备氮化硅薄膜。值得注意的是,采用sih4和n2制备的氮化硅薄膜含有较少的氢和较多的氮,可以提升后续制备的第二钝化层300对互连层100的防护效果。

[0146]

在一个实施例中,请继续参考图4所示出的结构,采用等离子体增强化学的气相沉积工艺,至少对第一钝化层200的表面进行钝化处理的方法,示例性包括:

[0147]

持续输出硅烷(sih4)、氨气(nh3)和氮气(n2),控制硅烷的气体流量在1000sccm~1500sccm,控制氨气的气体流量在300sccm~700sccm;控制氮气的气体流量在5000sccm~15000sccm;

[0148]

将等离子体的处理功率调整为1000w~1500w,在衬底上形成第一钝化层200。

[0149]

需要说明的是,在钝化处理第一钝化层200过程中,硅烷和氨气的流量需要调整为0,以避免干涉钝化处理过程。

[0150]

现结合图4对本公开实施例提供的半导体结构的形成方法进行具体说明。应理解,图4中仅涉及2次钝化处理过程。如图4所示出的结构,在pecvd工艺设备中,具体步骤如下:

[0151]

在制备稳定期中:持续输出硅烷(sih4)、氨气(nh3)和氮气(n2),控制硅烷的气体流量在1000sccm~1500sccm,控制氨气的气体流量在300sccm~700sccm;控制氮气的气体流

量在5000sccm~15000sccm;

[0152]

之后,进入制备第一层第一钝化层200的沉积期:将射频能量的范围调整为1000w~1500w,硅烷(sih4)、氨气(nh3)和氮气(n2)流量维持不变;

[0153]

之后,进入对第一层第一钝化层200的处理期:将射频能量的范围调整为500w~1000w;将硅烷和氨气的流量调整为0,维持氮气的气体流量在5000sccm~15000sccm,同时,将一氧化二氮的气体流量由0调整为100sccm~500sccm;

[0154]

值得注意的是,在处理期结束后,第一层第一钝化层200形成第二钝化层300。在制备完第二钝化层300后,制备第二层第一钝化层200之前,需要先进入稳定期:持续输出硅烷(sih4)、氨气(nh3)和氮气(n2),控制硅烷的气体流量在1000sccm~1500sccm,控制氨气的气体流量在300sccm~700sccm;控制氮气的气体流量在5000sccm~15000sccm,以在第一层钝化层200上形成第二层第一钝化层200;

[0155]

之后,进入制备第二层第一钝化层200的沉积期:射频能量的范围调整为1000w~1500w,硅烷(sih4)、氨气(nh3)和氮气(n2)维持不变;

[0156]

之后,进入对第二层第一钝化层200的处理期:射频能量的范围调整为500w~1000w;硅烷和氨气的流量调整为0,维持氮气的气体流量在5000sccm~15000sccm,同时,将一氧化二氮的气体流量由0调整为100sccm~500sccm;

[0157]

值得注意的是,在处理期结束后,第二层第一钝化层200形成钝化层300,此时两层钝化层300形成第二钝化层300。请继续参考图4所示出的结构,在制备完成第二钝化层300后,pecvd设备进行抽真空操作,以完成制备过程。

[0158]

当然,第二钝化层300的数目并不限于2层,具体可以根据需求进行限制。当制备过程中的多层第一钝化层200均转化为第二钝化层300时,具体的制备工艺如图5所示。应理解,稳定期、沉积期以及处理期形成一层第二钝化层300的制备周期,因而,倘若第二钝化层300为m层,则在进行抽真空操作前,会存在m个稳定期、沉积期以及处理期形成的制备周期。应理解,m为大于等于2的正整数,且m=n+1.

[0159]

值得注意的是,本公开实施例提供的半导体结构中互连层100存在多种结构可能,具体可以根据需求进行设置。

[0160]

在一个实施例中,请参考图6a所示出的结构,互连层100包括依次层叠的三个金属层,其中,依次为第一金属层102、第二金属层105以及第三金属层109。值得注意的是,各金属层间采用氧化物或氮化物进行间隔,以避免发生短路。

[0161]

示例性的,第一金属层102制备于第一介质层101内,且第一金属层102覆盖有第一绝缘层103;第一绝缘层103上覆盖有第二介质层104,第二金属层105制备于第二介质层104内,且第二金属层105表面覆盖有第二绝缘层106;第二绝缘层106上覆盖有第三介质层107;第三介质层107一侧设有第三金属层109。

[0162]

应理解,第一介质层101、第二介质层104以及第三介质层107的制备材料可以为氧化物;第一绝缘层103以及第二绝缘层106的制备材料可以为氮化物。

[0163]

请继续参考图6a所示出的结构,在需要连接位置,金属层间采用过孔连接。示例性的,第一金属层102与第二金属层105采用过孔连接,第二金属层105与第三金属层109采用过孔连接。应理解,过孔的设置位置以及图案可以根据需求进行设置,在此不再赘述。

[0164]

此外,第一金属层102、第二金属层105以及第三金属层109的制备材料可以根据需

求进行,示例性的,第一金属层102的材料为铜,第二金属层105的材料为铜,第三金属层109的材料为铝。值得注意的是,由于第三金属层109较为靠近顶面,所以第三金属层109两侧设有保护层,示例性的,在第三金属层109朝向第二金属层105一侧设有第一保护层108,在第三金属层109背离第二金属层105一侧设有第二保护层110,第一保护层108和第二保护层110的材料可以为钛。

[0165]

请继续参考图6a所示出的结构,可以在第三金属层109顶部的第二保护层110上形成光刻胶111,且通过光刻胶111的镂空图案对第三金属层109以及第一保护层108和第二保护层110进行刻蚀,形成图6b所示出的图案。

[0166]

在制备形成第一钝化层200之前,可以在如图6b所示出的结构中形成第四介质层112,示例性的,如图6c所示出的结构,该第四介质层112可以对互连层100形成初步防护。

[0167]

值得注意的是,形成的第四介质层112中设有空气间隙a,该空气间隙a用于对相邻的第三金属图案进行间隔,以减小二者之间的寄生电容,以提升本公开实施例提供的半导体结构的结构性能。

[0168]

之后,可以在图6c所示出的结构中制备形成第一钝化层200和第二钝化层300,以形成图7所示出的结构。

[0169]

第二方面,本公开实施例提供了一种半导体结构,包括:

[0170]

衬底;

[0171]

互连层100,形成于衬底一侧;

[0172]

第一钝化层200,形成于互连层100背离衬底一侧,且第一钝化层200具有氢键;

[0173]

第二钝化层300,形成于第一钝化层200背离互连层100一侧,第二钝化层300部分由第一钝化层200转化形成,且第二钝化层300内的氢键数目小于第一钝化层200内的氢键数目。

[0174]

需要说明的是,本公开实施例提供的半导体结构中,互连层100表面的第二钝化层300经过钝化处理,该第二钝化层300内含有较少的氢键,可以有效防止水汽进入,从而可以对互连层100形成有效保护,增强器件的可靠性。同时,第一钝化层200部分再处理后形成第二钝化层300,该第二钝化层300与第一钝化层200形成叠层结构,可以提升对互连层100的防护效果。

[0175]

值得注意的是,本公开实施例还保护由上述任意技术方案提供的半导体结构的形成方法制备形成的半导体结构,具体在此不再赘述。

[0176]

第三个方面,本公开实施例提供了一种存储器,包括上述任意技术方案提供的半导体结构。

[0177]

需要说明的是,本公开实施例提供的存储器中,半导体结构内的互连层100表面的第二钝化层300经过钝化处理,该第二钝化层300内含有较少的氢键,可以有效防止水汽进入,从而可以对互连层100形成有效保护,增强器件的可靠性。

[0178]

应理解,半导体结构利用晶体管控制数位信号储存,应用于各种存储器。示例性的,该存储器可以为动态随机存取存储器(dynamic random access memory,dram),该dram存储器的主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit)是1还是0。

[0179]

由于在现实中晶体管会有漏电电流的现象,导致电容上所存储的电荷数量并不足

以正确的判别数据,而导致数据毁损。因此对于dram来说,周期性地充电是一个无可避免的要件。由于这种需要定时刷新的特性,因此被称为“动态”存储器。相对来说,静态存储器只要存入数据后,纵使不刷新也不会丢失记忆。

[0180]

本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其它实施方案。本公开旨在涵盖本发明的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说明书和示例实施方式仅被视为示例性的,本公开的真正范围和精神由所附的权利要求指出。

[0181]

应当理解的是,本公开并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本公开的范围仅由所附的权利要求来限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1