半导体装置及其制造方法与流程

本公开总体上涉及一种半导体装置,更具体地,涉及一种包括外延电极层和电介质外延层的半导体装置及其制造方法。

背景技术:

1、随着半导体芯片的特征尺寸减小,设置在半导体芯片中的电容器装置的尺寸也减小。然而,构成电容器装置的电介质层所需的电容必须保持在最小预定参考值,以确保可靠的装置操作。因此,增加这种电容器装置的电容是有利的,因此正在研究各种方法来增加电容器装置中使用的电介质层的电容。

2、作为各种方法的代表性示例,已经研究了将高k材料应用于电容器装置的电介质层的方法和减小电介质层厚度的方法。然而,随着电容器装置的尺寸不断减小,行业要求电容器装置满足对较高电容参考值的需求,同时保持低泄漏电流和高击穿电压。

技术实现思路

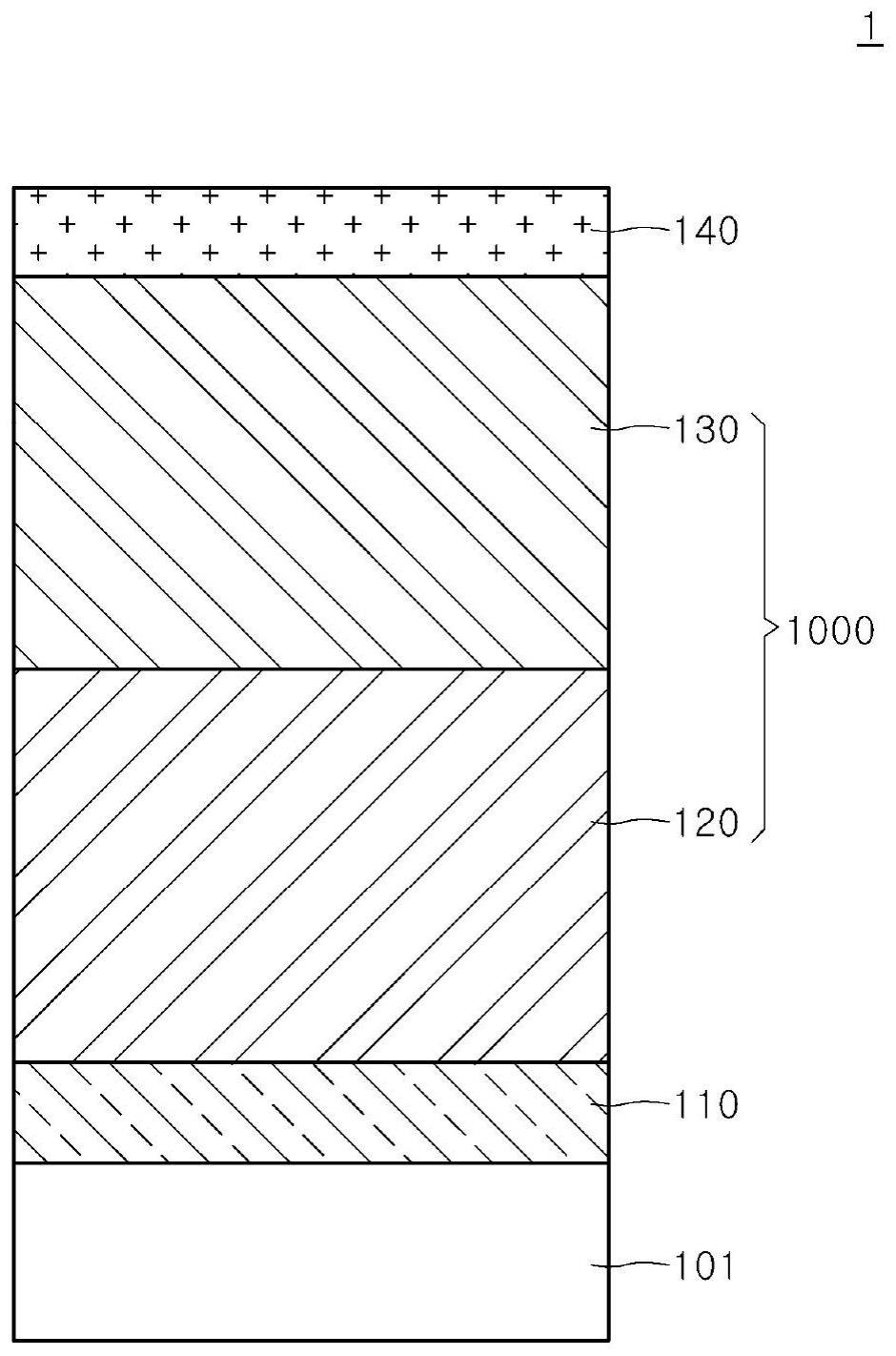

1、根据本发明实施例的一种半导体装置包括:衬底、设置在所述衬底上的第一外延电极层、设置在所述第一外延电极层上的铁电外延层、设置在所述铁电外延层上的电介质外延层,以及设置在所述电介质外延层上的第二外延电极层。所述第一外延电极层和所述第二外延电极层中的每一个包括导电烧绿石氧化物。所述铁电外延层和所述电介质外延层串联电连接。包括所述铁电外延层和所述电介质外延层的电介质结构是非铁电的。

2、根据本发明另一实施例的半导体装置包括:衬底、设置在所述衬底上的第一外延电极层、设置在所述第一外延电极层上的电介质外延层、设置在所述电介质外延层上的铁电外延层,以及设置在所述铁电外延层上的第二外延电极层。所述第一外延电极层和所述第二外延电极层中的每一个包括导电烧绿石氧化物。所述电介质外延层和所述铁电外延层串联电连接。包括所述电介质外延层和所述铁电外延层的电介质结构是非铁电的。

3、根据本公开的另一实施例的半导体装置包括衬底和设置在所述衬底上的电容器。所述电容器包括:储存节点外延电极、设置在所述储存节点外延电极上的铁电外延层、设置在所述铁电外延层上的电介质外延层,以及设置在所述电介质外延层上的板外延电极。所述储存节点外延电极和所述板外延电极中的每一个包括导电烧绿石氧化物。所述铁电外延层和所述电介质外延层串联电连接。所述电容器具有非铁电属性。

技术特征:

1.一种半导体装置,包括:

2.根据权利要求1所述的半导体装置,其中,所述铁电外延层具有负电容。

3.根据权利要求1所述的半导体装置,其中,所述导电烧绿石氧化物包括选自以下的至少一种:氧化铅铱(pb2ir2o7)、氧化镧铱(la2ir2o7)、氧化铈铱(ce2ir2o7)、氧化镨铱(pr2ir2o7)、氧化钕铱(nd2ir2o7)、氧化钐铱(sm2ir2o7)、氧化钆铱(gd2ir2o7)、氧化镱铱(yb2ir2o7)、氧化镧钌(la2ru2o7)、氧化铈钌(ce2ru2o7)、氧化镨钌(pr2ru2o7)、氧化钕钌(nd2ru2o7)、氧化钐钌(sm2ru2o7)、氧化钆钌(gd2ru2o7)、氧化镱钌(yb2ru2o7)、氧化铋钌(bi2ru2o7-δ,0<δ<1)、氧化铅钌(pb2ru2o7-δ,0<δ<1)、氧化铊钌(tl2ru2o7-δ,0<δ<1)、氧化铋铱(bi2ir2o7-δ,0<δ<1)、氧化铅铱(pb2ir2o7-δ,0<δ<1)以及氧化铊铱(tl2ir2o7-δ,0<δ<1)。

4.根据权利要求1所述的半导体装置,其中,所述铁电外延层包括氧化铪锆。

5.根据权利要求4所述的半导体装置,其中,所述铁电外延层包括掺杂在所述氧化铪锆中的掺杂剂,以及

6.根据权利要求1所述的半导体装置,其中,所述电介质外延层包括选自氧化铪、氧化锆和掺杂锆(zr)的氧化铪锆中的至少一种,以及

7.根据权利要求1所述的半导体装置,其中,所述铁电外延层具有正交晶系的晶体结构,以及

8.根据权利要求1所述的半导体装置,其中,所述铁电外延层和所述电介质外延层中的每一个具有1纳米至3纳米的厚度。

9.根据权利要求1所述的半导体装置,还包括设置在所述铁电外延层与所述电介质外延层之间的第一阻挡绝缘层。

10.根据权利要求9所述的半导体装置,其中,所述第一阻挡绝缘层包括选自氧化铝、氧化钇和氧化镁中的至少一种。

11.根据权利要求10所述的半导体装置,还包括设置在所述第一外延电极层与所述铁电外延层之间的第二阻挡绝缘层和设置在所述电介质外延层与所述第二外延电极层之间的第三阻挡绝缘层中的至少一个。

12.根据权利要求1所述的半导体装置,其中,所述衬底包括氧化钇稳定的氧化锆或氧化锶锡。

13.一种半导体装置,包括:

14.根据权利要求13所述的半导体装置,其中,所述铁电外延层具有负电容。

15.根据权利要求13所述的半导体装置,其中,所述导电烧绿石氧化物包括选自以下的至少一种:氧化铅铱(pb2ir2o7)、氧化镧铱(la2ir2o7)、氧化铈铱(ce2ir2o7)、氧化镨铱(pr2ir2o7)、氧化钕铱(nd2ir2o7)、氧化钐铱(sm2ir2o7)、氧化钆铱(gd2ir2o7)、氧化镱铱(yb2ir2o7)、氧化镧钌(la2ru2o7)、氧化铈钌(ce2ru2o7)、氧化镨钌(pr2ru2o7)、氧化钕钌(nd2ru2o7)、氧化钐钌(sm2ru2o7)、氧化钆钌(gd2ru2o7)、氧化镱钌(yb2ru2o7)、氧化铋钌(bi2ru2o7-δ,0<δ<1)、氧化铅钌(pb2ru2o7-δ,0<δ<1)、氧化铊钌(tl2ru2o7-δ,0<δ<1)、氧化铋铱(bi2ir2o7-δ,0<δ<1)、氧化铅铱(pb2ir2o7-δ,0<δ<1)以及氧化铊铱(tl2ir2o7-δ,0<δ<1)。

16.根据权利要求13所述的半导体装置,其中,所述铁电外延层包括氧化铪锆。

17.根据权利要求16所述的半导体装置,其中,所述铁电外延层包括掺杂在所述氧化铪锆中的掺杂剂,以及

18.根据权利要求13所述的半导体装置,还包括设置在所述铁电外延层与所述电介质外延层之间的第一阻挡绝缘层。

19.根据权利要求18所述的半导体装置,还包括设置在所述第一外延电极层与所述铁电外延层之间的第二阻挡绝缘层和设置在所述电介质外延层与所述第二外延电极层之间的第三阻挡绝缘层中的至少一个。

20.一种半导体装置,包括:

21.根据权利要求20所述的半导体装置,其中,所述铁电外延层实现负电容。

22.根据权利要求20所述的半导体装置,还包括设置在所述衬底上并电连接至所述电容器的场效应晶体管。

23.根据权利要求20所述的半导体装置,还包括设置在所述铁电外延层与所述电介质外延层之间的第一阻挡绝缘层。

24.根据权利要求23所述的半导体装置,还包括设置在所述储存节点外延电极与所述铁电外延层之间的第二阻挡绝缘层和设置在所述电介质外延层与所述板外延电极之间的第三阻挡绝缘层中的至少一个。

技术总结

根据本发明实施例的半导体装置包括:衬底、设置在衬底上的第一外延电极层、设置在第一外延电极层上的铁电外延层、设置在铁电外延层上的电介质外延层以及设置在电介质外延层上的第二外延电极层。铁电外延层实现负电容。第一外延电极层和第二外延电极层中的每一个包括导电烧绿石氧化物。铁电外延层和电介质外延层串联电连接。包括铁电外延层和电介质外延层的电介质结构是非铁电的。

技术研发人员:具元泰,徐东益

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!