一种红外探测器、成像芯片及其制备方法与流程

1.本发明涉及本发明实施例涉及光电子技术领域,尤其涉及一种红外探测器、成像芯片及其制备方法。

背景技术:

2.红外探测器的探测原理为:受红外线激发,探测器芯片传导电子增加,因而电导率增加,在外加偏压下,引起电流增加,增加的电流大小与光子数成比例。光电导探测器俗称光敏电阻。光电导又分本征型激发和非本征型(杂质型)激发两种。本征型是指红外光子把电子从价带激发至导带,产生电子—空穴对,即导带中增加电子,价带中产生空穴。杂质型是指红外光子把杂志能级的束缚电子(或空穴)激发至导带(或价带),使导带中增加电子(或价带中增加空穴)。应用最多的本征型光电导探测器有硫化铅、硒化铅、锑化铟、碲镉汞等;杂质型光电导探测器主要有锗掺汞、硅掺镓等。

3.光电集成可同时结合光子和电子电路的优势,打破传统微电子领域功耗以及信息传输的限制,促进信息产业的发展。光电集成方案中,硅基单片光电集成(光电集成芯片)具备可在同一衬底实现大部分光子器件(包括激光器、光电二极管、探测器等)和电子器件(包括放大器、信号调节器、读出电路等)集成、与传统微电子制造工艺兼容、可进行大规模量产的优势,具有良好的研究与应用前景。

4.现有技术中对光子器件和电子器件的集成工艺为:利用不同的衬底材料分别制备光子器件和电子器件,然后对这些分立的光子器件和电子器件进行集成来实现光电转换;这种方法工艺步骤复杂、耗时较长且集成度较低,还无法精确对准。

5.与硅相比,iii-v族半导体材料的载流子迁移率较高,有望用于先进cmos器件。目前,iii-v族晶体管的进展主要体现在器件性能和尺寸可微缩的3d器件架构两个方面。因此,迫切需要开发硅基iii-v族晶体管的集成方案。iii-voi技术作为soi的延伸技术,同样拥有介质隔离、寄生电容小、集成度高、速度快、工艺简单、短沟道效应小、低压低功耗、低漏电流等优势。特别是全耗尽iii-voi(fully depleted iii-voi)技术,其埋氧化层(box)和顶部iii-v材料厚度均较薄,相关器件拥有的寄生电容更小、工作速度更快、功耗更低、抗辐射性能极强。(全耗尽ingaas晶体管的优势)。因此,开发(fd)iii-voi衬底制造工艺是实现高性能场效应晶体管的重要研究内容。

6.ingaas材料电子迁移率极高,是非常重要的晶体管沟道候选材料;此外,ingaas还具有优异的光电特性,其在短波红外波段的吸收系数极高,可实现高性能的短波红外成像芯片。采用与inp晶格匹配的三元合金in0.53ga0.47as制造的短波红外探测器截止波长为1.7μm,器件性能极好,已在许多领域得到广泛应用。(fd)ingaasoi读出电路与ingaasoi短波红外焦平面阵列可实现单片光电集成,其制造工艺更加简单,有望实现更低成本、更低功耗、更高分辨率的短波红外相机。

7.目前商用的ingaas短波红外相机主要包括:光学系统、短波红外焦平面阵列芯片、硅读出电路、信号处理系统等。当短波红外焦平面阵列芯片与硅读出电路互联时,通常采用

异质集成的方式,面临制造工艺复杂,制造成本高,分辨率低,规模化生产困难等问题。值得注意的是:绝大多数均采用硅读出电路对探测器信号进行集成、放大与多路复用。与硅读出电路相比,(fd)ingaasoi读出电路性能更优。

8.现存的多数ingaasoi衬底尺度小,制造成本高,形成的探测器阵列规模小。采用smart cut

tm

技术制造(fd)ingaasoi衬底时,需要有大尺寸的ingaas衬底,存在制造成本高、层结构较薄等问题,无法实现ingaas短波红外探测器和(fd)ingaasoi场效应晶体管的单片光电集成,迫切需要开发新的(fd)ingaasoi衬底制造方案。

9.参考文献:1、“an ingaas on si platform for cmos with 200 mm ingaas-oi substrate,gate-first,replacement gate planar and finfets down to 120 nm contact pitch”;

10.2、“300 mm ingaasoi substrate fabrication using the smart cut tm technology”;

11.3、“advances in ingaas/inp single-photon detector systems for quantum communication”;

12.4、“an ingaas detector for the 1.0

–

1.7μm wavelength range”;

13.5、“high performance ingaas-on-insulator mosfets on si by novel direct wafer bonding technology applicable to large wafer size si”。

技术实现要素:

14.针对上述技术问题,本发明提供一种ingaasoi衬底上单片光电集成的短波红外成像芯片及其制备方法,该方法是将未制作出探测器结构的衬底键合在电子电路结构衬底中,再制作探测器结构,这样简化了集成流程,提高了集成度,还解决了无法精确对准的问题。

15.为了实现以上目的,本发明提供了以下技术方案:

16.一种光电探测器的集成方法,包括:

17.在第一衬底的表面由下至上依次形成缓冲结构层、垂直堆叠结构层和高迁移率沟道层,所述垂直堆叠结构层为p-i-n-i垂直堆叠结构或n-i-p-i垂直堆叠结构,然后在所述高迁移率沟道层的表面形成第一介质层,获得施主衬底;

18.在第二衬底的表面形成第二介质层,得到受主衬底;

19.以所述第一介质层和所述第二介质层为键合面,将所述受主衬底和所述施主衬底键合;

20.键合后去除第一衬底及缓冲结构层,形成第三衬底;

21.然后在所述第三衬底中自上至下进行垂直刻蚀至裸露出高迁移率沟道层,将第三衬底分隔成光电探测器区域和晶体管区域;

22.其中光电探测器区域形成光电探测器;

23.在晶体管区域刻蚀掉缓冲层、垂直堆叠结构,在裸露出的高迁移率沟道层上形成栅极和源漏极,形成晶体管;

24.将所述晶体管和所述光电探测器结构进行电连接。

25.一种探测器的集成结构,其包括:

26.绝缘衬底;

27.绝缘衬底上包括光电探测器和晶体管;

28.所述光电探测器为p-i-n-i垂直堆叠结构或n-i-p-i垂直堆叠结构,其中最下层为第一i-ingaas层;

29.绝缘衬底上的第二i-ingaas层上设置栅极和源漏极,形成晶体管;

30.其中第一i-ingaas层、第二i-ingaas层之间经刻蚀而电隔离;

31.将所述晶体管和所述平面型光电探测器进行电互连,用于读出光电探测器的光电流。

32.与现有技术相比,本发明达到了以下技术效果:

33.本发明提出的是一种将双异质结探测器与低功耗(fd)ingaas晶体管集成在同一ingaasoi衬底上的方案,借助ingaas材料的高迁移率及优异的光电性质,提供ingaasoi衬底上短波红外成像芯片的单片光电集成方案,简化制造工艺步骤,降低成本。

34.1)传统的ingaas探测器阵列是采用键合的方式与硅读出电路异质集成形成成像系统,而本专利采用fd-ingaas晶体管作为ingaas探测器阵列的读出电路,即读出电路与探测器阵列集成在同一衬底上,成像效果更好,制造工艺更加简单;

35.2)传统的inp/ingaas/inp探测器直接在inp或者si衬底上外延形成,器件的性能漏电流较大,无谐振腔作用,器件工作速度慢;而本专利中,采用键合的方式在绝缘体衬底上形成inp/ingaas/inp/ingaas的pini或者nipi结构,形成的探测器与晶体管性能均由于现有技术,且集成在同一衬底上,成像的工作速度更快,功耗更低。

36.3)本发明采用的多氧化层结构存在的谐振腔作用较强,有助于提升ingaas探测器的响应度等性能指标;通过合理的控制inp/ingaas/inp厚度,其谐振腔作用亦可得到提升,器件的工作速度更快,功耗更低。

附图说明

37.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。

38.图1为施主衬底100的示意图。

39.图2为受主衬底200的示意图。

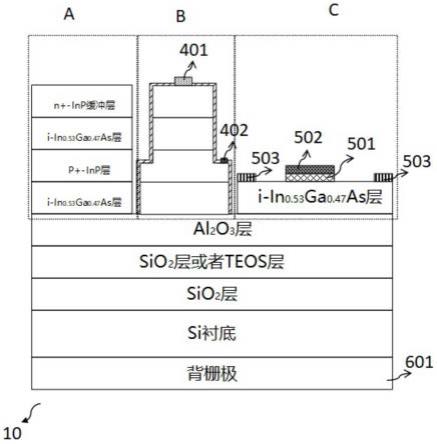

40.图3为键合后的施主衬底100、受主衬底200的示意图。

41.图4为ingaasoi衬底的示意图。

42.图5为ingaasoi衬底上形成sio2层的示意图。

43.图6为在sio2层开孔的示意图

44.图7为在ingaasoi衬底上形成光电探测器区域和晶体管区域的示意图

45.图8为在光电探测器外表面形成钝化膜的示意图

46.图9为在光电探测器外表面分别形成n型接触、p型接触的示意图。

47.图10为晶体管区域去掉nipi/pini结构、形成金属栅的示意图。

48.图11位本发明光电探测器的集成结构的示意图。

具体实施方式

49.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

50.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

51.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

52.本发明提供ingaasoi衬底上单片光电集成的短波红外成像芯片制备方法,具体包括如下步骤:

53.步骤一:形成施主衬底100

54.参见图1,提供斜切6

°

角si衬底101作为初始衬底,然后在其上依次外延生长,分别形成低温ge层102、高温ge层103,然后对高温ge层103上表面进行化学机械抛光(cmp)处理,再依次外延生长,自下至上分别形成gaas缓冲层104、n+-inp缓冲层105、i-in

0.53

ga

0.47

as层106、p+-inp层107、i-in

0.53

ga

0.47

as缓冲层108、al2o3层109,如此形成施主衬底100。其中,inp与in

0.53

ga

0.47

as是完全晶格匹配的,形成的材料无缺陷,且为inp/ingaas/inp形成的是双异质结结构,相较于同质结来说,双异质结结构对载流子的限制作用强,采用该双异质结结构制造的光电探测器工作速度快,灵敏度高。在本实施例中,外延生长采用分子束外延(mbe)。

55.上述形成的为施主衬底在后续的步骤中形成探测器垂直结构为nipi结构,在另一个实施例中,n+-inp缓冲层105、p+-inp层107的形成顺序可以互换,导致二者的位置也互换,由此后续形成的探测器垂直结构为pini结构。

56.在另一实施例中,如图1中虚线框中的斜切6

°

角si衬底101、低温ge层102、高温ge层103、gaas缓冲层104、n+-inp缓冲层105可以整体替换为n+-inp衬底。

57.步骤二:形成受主衬底200

58.参见图2,提供常规si衬底201作为初始衬底,在其上通过热氧化工艺形成厚度为10-500nm sio2层202,其便于后续增加键合强度;然后再通过热氧化工艺形成sio2层或者teos层203,厚度为10-500nm,其便于增加键合强度,并增加探测器的谐振腔作用,如此形成受主衬底200。

59.步骤一形成施主衬底100和步骤二形成受主衬底200的顺序可以颠倒或者同时进行。

60.步骤三:将施主衬底100、受主衬底200进行键合,形成ingaasoi衬底。

61.如图3所示,首先,进行对施主衬底100键合面进行活化处理,即对al2o3层109的上表面进行活化处理。通过利用o2和/或n2等离子体的等离子活化,来补充施主衬底的活化。将

要被键合的施主衬底100的al2o3层109的上表面暴露给氧等离子体或含o2的等离子体。

62.接着,对受主衬底200的活化包括:表面清洗,例如利用sc1在30℃至80℃清洗约10分钟;在如上文所述对施主衬底100活化的相同条件下,对受主衬底200的键合面进行等离子活化,即对sio2层或者teos层203进行等离子活化。

63.活化工艺步骤的作用是制备用于键合的表面,以便实现高键合能。

64.随后,将施主衬底100和受主衬底200置于键合室中,受主衬底200上的sio2层或者teos层203的表面面对施主衬底100的al2o3层109的表面。通常,依据两个衬底的对准标记来对准这两个衬底。在这些衬底被放入并被对准之后,封闭该键合室且抽真空到约1-50torr,优选为1-20torr。通常,这个过程持续约2-3分钟,而对于本发明的目的来说,这个等级的低真空使得在适度时间内(例如,与高真空或超高真空相比)增加了键合能。

65.在本实施方式的键合室中的气氛主要包括干燥气氛(特别是h2o分子少于100ppm的气氛)和/或进一步优选的例如由氩和/或氮构成的中性气氛。键合室保持在室温,因此处于18℃至26℃的温度范围内为佳。

66.当达到所需压力等级时,使得受主衬底200上的sio2层或者teos层203的表面面对施主衬底100的al2o3层109的表面开始接触,如图3所示的,并且开始键合。通常,键合发生在一点且键合波传播开来,以使得上述两层的表面最终通过分子间接合力(范德华力)彼此连接,并形成施主-受主复合体。在一个实施例中,可通过机械指在一侧或中心施加轻微的压力而实现初始接触。

67.由于表面活化步骤与在低真空下的接触相结合地实施而带来的有利协同效果,借助于所描述的键合方法能够实现至少700-1000mjoule/m2范围内的键合能,同时降低了键合缺陷的程度或甚至没有键合缺陷。而且,无需在大于500℃的高温下实施键合后退火(post-bonding anneal)就能实现这些结果。已经观测到,除了由键合之前就存在于两个表面之一上的颗粒而产生的空隙之外,可以抑制或限制(与现有键合方法相比,可达到至少一个数量级)边缘空隙的出现。

68.接着如图4所示,施主衬底100被减薄,复合体的顶部斜切6

°

角si衬底101被减薄。所述减薄过程为:通过研磨和/或抛光步骤,随后进行化学蚀刻,该化学蚀刻终止在低温ge层102处。通过tmah溶液对低温ge层102、高温ge层103、gaas层105选择性刻蚀,裸露出n+-inp缓冲层106。

69.在一个实施例中,斜切6

°

角si衬底101、低温ge层102、高温ge层103、gaas缓冲层104、n+-inp缓冲层105可以整体替换为n+-inp衬底,此时仅需要对n+-inp衬底进行减薄,减薄至合适的厚度,优选减薄至100-2000nm。

70.然后可以实施其他完成步骤,例如边缘抛光和/或研磨,例如进行化学机械抛光(cmp)后得到本发明需要的ingaasoi衬底300。

71.步骤四:形成垂直结构的ingaasoi探测器

72.在上述步骤三中获得的ingaasoi衬底300的上表面,即暴露出的n+-inp缓冲层104的表面通过热氧化工艺形成sio2层301,如图5所示。然后通过物理或化学刻蚀sio2层301,使得在sio2层301上开孔,形成孔302,其直径为10-200μm,如图6所示。

73.参见图7,接着以剩余的sio2层301为掩膜,对ingaasoi衬底300进行刻蚀,刻蚀至al2o3层109的上表面,在孔302的位置下形成台面。由图7的纵向剖面图可知,此时的

ingaasoi衬底300被分成了三部分,从左至右分别为a区、b区、c区。其中台面位于中间的b区。台面各层的组分与a区各层的组分相同,台面的台阶位置形成在p+-inp层107中。在一个实施例中a区可以不被保留;b区的后续的步骤中形成垂直结构的探测器(指pn结构的设置方向),本发明中用于探测短波红外线;c区在后续步骤中形成晶体管,晶体管可以为读出电路,读出探测器中的电学信号,包括但不限于放大器、信号调节器中的一种或多种集成。

74.b区中从上到下的结构依次为n+-inp缓冲层105、i-in

0.53

ga

0.47

as层106、p+-inp层107、i-in

0.53

ga

0.47

as层108,形成n-i-p-i堆叠结构,构成成光电探测器件的核心nipi结。

75.在一个实施例中,n+-inp缓冲层105、p+-inp层107的形成顺序可以互换,导致二者的位置也互换,此时b区的探测器从上到下的结构依次为p+-inp层107、i-in

0.53

ga

0.47

as层106、n+-inp缓冲层105、i-in

0.53

ga

0.47

as层108,形成p-i-n-i堆叠结构,构成光电探测器件的核心pin结。

76.随后在b区的台面表面形成钝化层400,钝化层400可增强器件的稳定性和可靠性,屏蔽外界杂质、离子电荷、水汽等对器件的有害影响。钝化层400的形成可采用物理/化学气相沉积工艺,包括但不限于lpcvd、rtcvd、pecvd或热氧化法等,钝化层400的材质为sio2、hfo2或al2o3,如图8所示。

77.在钝化层400顶部开孔,使得部分p+-inp缓冲层105暴露出来,在上述孔的位置形成掺杂有n型光吸收层401,在一个实施例中n型光吸收层401为n型inp层,掺杂元素为是s、sn,掺杂浓度为5e

18-5e

19

,形成工艺为原位掺杂、扩散或者离子注入;掺杂厚度100-2000nm;在台阶上表面开孔,使得p+-inp层107暴露出来,在上述孔的位置形成掺杂有p型的光吸收层402,p型的光吸收层402为p型inp,掺杂元素是zn,掺杂浓度是5e

18-6e

19

;形成工艺为原位掺杂、扩散或者离子注入,掺杂厚度是100-2000nm,如图9所示。

78.步骤五:形成全耗尽型ingaasoi晶体管

79.参见图10,去除c区域的n-i-p堆叠结构或者p-i-n堆叠结构,即依次刻蚀掉c区域的n+-inp缓冲层105、i-in

0.53

ga

0.47

as层106、p+-inp层107,刻蚀工艺可采用所述刻蚀工艺为干法刻蚀或湿法刻蚀,在一个实施例中可采用反应离子刻蚀(rie)。在c区域裸露出的i-in

0.53

ga

0.47

as层108的上表面依次沉积高k介质层501、栅金属层502,然后通过刻蚀工艺刻蚀高k介质层501、栅金属层502,刻蚀掉两侧的高k介质层501、栅金属层502,保留中间的高k介质层501、栅金属层502,并在高k介质层501、栅金属层502两侧、裸露出i-in

0.53

ga

0.47

as层108的上表面的位置分别沉积源漏极503,由此形成了读出电路。在本实施例中,读出电路为放大电路,放大来自b区探测器的电信号。

80.进行快速热退火,使得b区中的n-i-p-i堆叠结构或者p-i-n-i结构中的pi或者ni层互扩,从而形成nipi结构或者pini结构。

81.最后,通过tsv工艺将读出电路结构和探测器结构互连,得到如图11所示的结构(图中未示出详细的电路结构)。

82.该方法适用于任意需要集成在单片硅基芯片上的垂直型(指pn结构的设置方向)光电器件,因此对读出电路结构和探测器结构无具体要求,读出电路结构可替换为其他单功能或多功能结构,例如包括放大器、信号调节器中的一种或多种集成。

83.本发明提出的是一种将ingaasoi探测器和(fd)ingaasoi晶体管集成在同一衬底的方案,晶体管类型包括但不限于平面结构的(fd)ingaasoi晶体管,还可以包括:平面结构

的部分耗尽(partially depleted,pd)型晶体管、三维结构的多栅晶体管(比如,双栅晶体管、pi(п)栅晶体管、omega(ω)栅晶体管)、鳍状(fin)场效应晶体管等。

84.图11示出了光电检测器10的第一示例的示意性纵向剖面,用于探测短波红外线的截止波长为1.7μm。

85.以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1