一种SOI上单片光电集成的台面型雪崩光电探测阵列芯片及其制备方法与流程

一种soi上单片光电集成的台面型雪崩光电探测阵列芯片及其制备方法

技术领域

1.本发明涉及光电子技术领域,尤其涉及一种soi上单片光电集成的台面型锗雪崩光电探测阵列芯片及其制备方法。

背景技术:

2.soi技术拥有寄生电容小、集成度高、工作速度快、工艺简单、低压低功耗和低漏电流等。特别是全耗尽型soi(fully depleted soi,fd-soi)mosfet,其寄生电容更小、工作速度更快、功耗更低、抗辐射性能极强,引起了学术界与工业界的极大兴趣。鉴于硅材料拥有较高的倍增系数,soi技术可兼顾锗雪崩光电探测器(avalanche photodiode,apd)和晶体管的关键性能指标,顶部硅层既可作为锗apd的倍增层,亦可作为fdsoi晶体管的沟道材料。对于锗apd而言,吸收层通常采用异质外延的锗材料,其拥有较高的吸收系数,是非常重要的硅基光电子材料。因此,soi衬底上同时实现高性能的锗apd和fdsoi晶体管显得尤为重要,是实现高性能短波红外成像芯片的重要研究内容。

3.雪崩光电二极管(apd)比普通的二极管灵敏度更高。它的优势是低光探测和光子计数。用apd代替普通的pin光电探测器可提高器件的灵敏度。对于长波长的光信号锗材料作为吸收层,但是由于硅有更低的倍增噪声,因此apd器件的倍增层经常使用硅材料。由于他们各自具有性能优势,apd主要应用于测量低波长光信号、光谱信号、通信传输、光纤通信、测距、工业检验和其他各种医学科学仪器。

4.当前,多数ge apds是在si衬底上直接生长;尽管有个别的文献报道在soi衬底上实现ge apds阵列,但其没有与硅读出电路连接,且ge apds阵列仅可以通过键合的方式与硅读出电路连接,从而实现对信号的集成、放大与多路复用,与读出电路键合是目前主流的方式,该方法存在热预算的问题,制备工艺难度较大且工艺稳定性差;

5.尽管已有锗红外探测器与fdsoi读出电路通过键合的方式实现异质芯片集成,但其制备工艺复杂,制备成本高,分辨率低,规模化生产困难,实现单片集成的短波红外成像芯片有利于简化制备工艺,可实现更低成本、更低功耗、更高分辨率的短波红外相机。

6.目前,基于soi衬底的光子器件与电子器件研究进展迅速,主要包括:soi基激光器、soi基探测器、soi基调制器、soi基光波导、soi基晶体管等,器件的关键性能均显著提升。特别是fd-soi(full-depleted soi)技术,其埋氧化层(box)和顶部硅厚度均较薄,寄生电容更小、速度更快、功耗更低、抗辐射性能极强,可实现对先进纳米节点工艺制程下晶体管电流的有效控制和阈值电压的灵活调控。现在随着fdsoi技术逐渐成熟,fd-soi生态圈已初具规模,相关技术产品可广泛应用于汽车电子、it网路基础设施、伺服器、消费电子、物联网、雷达、供电电池、可穿戴电子、网络机器学习、人工智能和智能驾驶等领域,具有重大的科学价值与经济利益。此外,将fdsoi晶体管与锗apd集成在同一衬底上,其制备工艺更加简单,有望实现更低成本、更低功耗、更高分辨率的短波红外成像芯片。

7.参考文献:

8.1、“geiger-mode avalanche photodiode arrays fabricated on soi engineered-substrates”;

9.2、“development for germanium blocked impurity band far-infrared image sensors with fully-depleted silicon-on-insulator cmos readout integrated circuit”;

10.3、“high-definition visible-swir ingaas image sensor using cu-cu bonding of iii-v to silicon wafer”。

技术实现要素:

11.针对上述技术问题,本发明提供了一种在soi衬底上实现拥有p+-ge/i-ge/p-si/i-si/n+-si垂直结构的ge/soi衬底的制备方法,旨在为锗apd阵列芯片和fd-soi读出电路的单片光电集成提供衬底材料基础;借助soi衬底顶部硅材料拥有较高的倍增系数与载流子迁移率,兼顾锗apd和fdsoi晶体管性能;同时本发明提供soi衬底上锗apd阵列芯片的单片光电集成方案,简化制备工艺步骤,降低成本。

12.为了实现以上目的,本发明提供了以下技术方案:

13.一种soi上单片光电集成的台面型锗雪崩光电探测阵列芯片制备方法,其特征在于,包括:

14.在soi由下至上依次形成垂直堆叠结构层,所述垂直堆叠结构层为pi-pin垂直堆叠结构,形成衬底;

15.然后在所述第三衬底中自上至下进行垂直刻蚀至裸露出soi的box层,将衬底分隔成光电探测器区域和晶体管区域;

16.其中光电探测器区域形成apd;

17.在晶体管区域刻蚀掉垂直堆叠结构,在裸露出的soi的i-si层上形成栅极和源漏极,形成晶体管;

18.将所述晶体管和所述光电探测器结构进行电互连。

19.一种soi上单片光电集成的平面型雪崩光电探测阵列芯片,在soi衬底上包括多个探测器单元,每个探测器单元包括台面型光电探测器和晶体管;

20.所述台面型光电探测器,其设置在soi衬底上,其为pi-pin垂直堆叠结构;

21.soi衬底的i-si层上设置栅极和源漏极,形成晶体管;

22.将所述晶体管和所述平面型光电探测器进行电互连,用于读出平面型光电探测器的光电流。

23.与现有技术相比,本发明达到了以下技术效果:

24.本发明提供在soi衬底上实现拥有p+-ge/i-ge/p-si/i-si/n+-si垂直结构的ge/si/soi衬底制备方法,旨在为锗apd阵列芯片和fd-soi读出电路的单片光电集成提供衬底材料基础;借助soi衬底顶部硅材料拥有较高的倍增系数与载流子迁移率,兼顾锗apd和fdsoi晶体管性能;提供soi衬底上锗apd阵列芯片的单片光电集成方案,简化制备工艺步骤,降低成本。

附图说明

25.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。

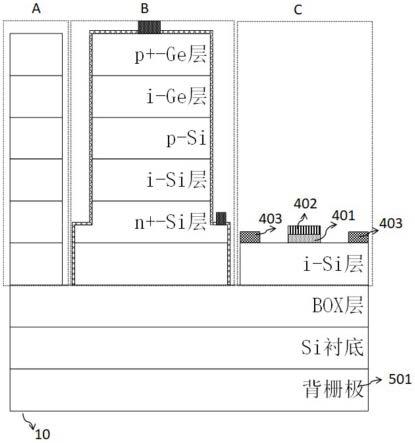

26.图1为在soi衬底上形成垂直结构p+-ge/i-ge/p-si/i-si/n+-si/soi衬底100的示意图。

27.图2为在衬底100上形成光电探测器区域和晶体管区域的示意图

28.图3为在光电探测器外表面分别形成钝化膜、n型接触、p型接触的示意图。

29.图4为本技术光电探测器的集成结构的示意图。

具体实施方式

30.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

31.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制备公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

32.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

33.本发明提供soi衬底上单片光电集成的短波红外成像芯片制备方法,具体包括如下步骤:

34.步骤一:形成垂直结构p+-ge/i-ge/p-si/i-si/n+-si/soi衬底100

35.参见图1,提供soi衬底101作为初始衬底,soi衬底101自下至上依次包括si衬底、box层、i-si层。将soi衬底101外延生长厚度为0.5-2μm的n型重掺杂si层102。然后在n型重掺杂si层102上外延生长厚度为0.5-2μm的本征i-si层103,本征i-si层103为雪崩倍增层。在本征i-si层103上外延生长形成厚度为100nm的p-si层104,p-si层104为电子调节(电荷层)层。然后在本征i-si层103、p-si层104上分别外延生长厚度为0.5-3μm的本征i-ge层105,本征i-ge层105为吸收层。在本征i-ge层105上外延生长厚度为100nm的p+-ge层106,p+-ge层106为接触层。如此经过上述工艺形成垂直结构的p+-ge/i-ge/p-si/i-si/n+-si/soi衬底100,即pi-pin型结构。在本实施例中,外延生长采用分子束外延(mbe)。

36.步骤二:形成锗apd台面结构

37.在上述步骤一中获得的衬底100的上表面,即p+-ge层106的表面通过热氧化工艺形成sio2层201,如图2所示。然后通过物理或化学刻蚀sio2层201,使得在sio2层301上开孔,形成孔202,孔202直径为10-200μm,如图2所示。

38.参见图2,接着以剩余的sio2层201为掩膜,对衬底100进行刻蚀,刻蚀至衬底101的

box层的上表面,在孔302的位置下形成台面。由图2的纵向剖面图可知,此时的衬底300被分成了三部分,从左至右分别为a区、b区、c区。其中台面位于中间的b区。台面各层的组分与a区各层的组分相同,台面的台阶位置分别形成在n+-si层102、本征i-si层103中。在一个实施例中a区可以不被保留;b区的后续的步骤中形成垂直结构的探测器(指pn结构的设置方向),本发明中用于探测短波红外线;c区在后续步骤中形成晶体管,晶体管可以为读出电路,读出探测器中的电学信号,包括但不限于放大器、信号调节器中的一种或多种集成。

39.b区中从上到下的结构依次为p+-ge层106、i-ge层105、p-si层104、本征i-si层103、n型重掺杂si层102,其中p+-ge层106、i-ge层105、p-si层104、本征i-si层103、n型重掺杂si层102形成pi-pin型堆叠结构,构成光电探测器件的核心pn结。

40.随后在b区的台面表面形成钝化层300,钝化层300可增强器件的稳定性和可靠性,屏蔽外界杂质、离子电荷、水汽等对器件的有害影响。钝化层300的形成可采用物理/化学气相沉积工艺,包括但不限于lpcvd、rtcvd、pecvd或热氧化法等,如图2所示。

41.在钝化层300顶部开孔,使得部分p+ge106暴露出来,在上述孔的位置形成掺杂有p型光吸收层301,在台阶上表面开孔,使得n+-si层103暴露出来,在上述孔的位置形成掺杂有p型的光吸收层302,然后去掉剩余的sio2层201,如图2所示。

42.步骤三:形成全耗尽型soi晶体管

43.参见图3,去除c区域的pi-pin型堆叠结构,即依次刻蚀掉c区域的p+-ge层106、i-ge层105、本征i-si层103、n型重掺杂si层102,刻蚀工艺可采用所述刻蚀工艺为干法刻蚀或湿法刻蚀,在一个实施例中可采用反应离子刻蚀(rie)。在c区域裸露出的soi衬底i-si层的上表面依次沉积高k介质层401、栅金属层402,然后通过刻蚀工艺刻蚀高k介质层401、栅金属层402,刻蚀掉两侧的高k介质层401、栅金属层402,保留中间的高k介质层401、栅金属层402,并在高k介质层401、栅金属层402两侧、裸露出soi衬底i-si层的上表面的位置分别沉积源漏极403,由此形成了读出电路。在本实施例中,读出电路为放大电路,放大来自b区探测器的电信号。

44.然后在soi衬底底部表面镀一层金属,使得soi衬底的si层形成背栅极501。

45.进行快速热退火,使得soi基锗apd中的本征si层与n型重掺杂si层互扩,从而在soi衬底上形成pi-pin结构。

46.最后,通过tsv工艺将读出电路结构和探测器结构互连,得到如图4所示的结构(图中未示出详细的电路结构)。

47.该方法适用于任意需要集成在单片硅基芯片上的垂直型(指pn结构的设置方向)光电器件,因此对读出电路结构和探测器结构无具体要求,读出电路结构可替换为其他单功能或多功能结构,例如包括放大器、信号调节器中的一种或多种集成。

48.本发明提出的是一种将soi基锗apd像元和fdsoi晶体管集成在同一衬底的技术方案,晶体管类型不限于平面结构的fdsoi晶体管,还可以包括:平面结构的部分耗尽(partially depleted,pd)型晶体管、三维结构的多栅晶体管(比如,双栅晶体管、pi(п)栅晶体管、omega(ω)栅晶体管)、鳍状(fin)场效应晶体管等

49.以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的

范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1