封装结构及其形成方法与流程

1.本发明实施例涉及一种半导体制造技术,特别涉及一种半导体封装结构及其形成方法。

背景技术:

2.半导体集成电路(integrated circuit,ic)产业经历了快速成长。半导体制造工艺的持续进步导致半导体装置具有更精细的特征及/或更高的整合度。功能密度(即,每个芯片面积的互连装置的数量)普遍增加,而特征尺寸(即,可以使用制造工艺创建的最小部件)则减小。这种缩小化(scaling-down)工艺通常通过提高生产效率和降低相关成本来提供好处。

3.芯片封装不仅可以保护半导体装置免受环境污染,还可以为封装在其中的半导体装置提供连接接口。已开发出利用较小面积或较低高度的较小封装结构来封装半导体装置。

4.已开发出新的封装技术以进一步改善半导体晶粒的密度和功能。这些相对新型的半导体晶粒封装技术面临制造挑战。

技术实现要素:

5.本公开一些实施例提供一种封装结构,包括:重分布结构,位于基板上方;半导体晶粒,位于重分布结构上方并电耦接到基板;以及底部填充材料,位于基板上方并密封重分布结构和半导体晶粒,其中底部填充材料包括与半导体晶粒的角落重叠并延伸到基板中的延伸部分。

6.本公开一些实施例提供一种封装结构,包括:多个接合元件,位于基板上方;重分布结构,位于所述接合元件上方;半导体晶粒,位于重分布结构上方;以及底部填充材料,包括:第一部分,围绕所述接合元件;以及第二部分,嵌入基板中,其中在平面图中,半导体晶粒的角落局限(confined)在第二部分的区域内。

7.本公开一些实施例提供一种形成封装结构的方法,包括:将半导体晶粒接合到重分布结构的第一表面;将重分布结构的第二表面接合到基板,其中基板包括与半导体晶粒的角落重叠的第一沟槽;以及用底部填充材料密封半导体晶粒和重分布结构,其中基板的第一沟槽填充有底部填充材料。

附图说明

8.根据以下的详细说明并配合说明书附图做完整公开。须注意的是,根据本产业的一般作业,图示并未必按照比例绘制。事实上,可能任意的放大或缩小元件的尺寸,以做清楚的说明。

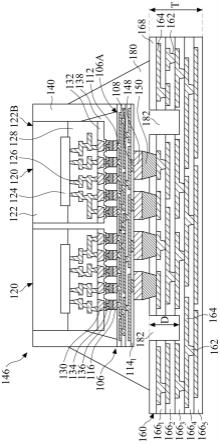

9.图1a至图1g是示出根据本公开一些实施例的在形成一封装结构的各个中间阶段的剖面图。

10.图1a-1是根据本公开一些实施例的图1a中所示的封装结构的平面图。

11.图1b-1是根据本公开一些实施例的图1b中所示的封装结构的平面图。

12.图1e-1是根据本公开一些实施例的图1e中所示的封装结构的平面图。

13.图1f-1是根据本公开一些实施例的图1f中所示的封装结构的平面图。

14.图1f-2是图1f-1中所示的区域r的放大平面图,示出根据本公开一些实施例的一封装结构的细节。

15.图1g-1是图1g对应于图1f-1中所示的区域r的放大平面图,示出根据本公开一些实施例的一封装结构的细节。

16.图2是根据本公开一些实施例的图1g-1的修改。

17.图3是根据本公开一些实施例的图1g-1的修改。

18.图4是根据本公开一些实施例的图1g-1的修改。

19.图5是根据本公开一些实施例的图1g-1的修改。

20.图6-1是根据本公开一些实施例的图1g的封装结构的修改的平面图。

21.图6-2是根据本公开一些实施例的图6-1中所示的区域r的放大平面图。

22.图7-1是根据本公开一些实施例的图1g的封装结构的修改的平面图。

23.图7-2是根据本公开一些实施例的图7-1中所示的区域r的放大平面图。

24.图8是根据本公开一些实施例的图1g中所示的剖面图的修改。

25.图8-1是根据本公开一些实施例的图8中所示的封装结构的平面图。

26.图8-2是图8-1中所示的区域r的放大平面图,示出根据本公开一些实施例的一封装结构的细节。

27.图9是根据本公开一些实施例的图8-1的封装结构的修改的平面图。

28.【附图标记列表】

29.102:载体基板

30.104:胶带

31.106:重分布结构

32.106a:顶表面

33.106b:底表面

34.106i:扇入区

35.106o:扇出区

36.106c1,106c2,106c3,106c4:角落

37.106s1,106s2,106s3,106s4:侧壁

38.108:导电特征

39.110:导电特征

40.112:导电特征/导电通孔

41.1141,1142,1143,1144:绝缘层

42.116:凸块下金属化结构

43.120:半导体晶粒

44.120c1,120c2,120c3,120c4:角落

45.120s1,120s2,120s3,120s4:侧壁

46.122:半导体基板

47.122b:背面

48.122f:正面

49.124:集成电路

50.126:互连结构

51.128:金属间介电层

52.130:导电垫

53.132:钝化层

54.134:凸块下金属化结构

55.136:接合元件

56.138:底部填充材料

57.140:模塑料

58.142:胶带

59.144:载体基板

60.146:封装结构

61.148:凸块下金属化结构

62.150:接合元件

63.160:基板

64.162:导电特征/导电垫

65.164:导电特征

66.1661,1662,1663,1664,1665:绝缘层

67.168:阻焊层

68.170:沟槽

69.170c:纵向

70.170l:第一侧壁

71.170o:部分

72.170w1,170w2:第二侧壁

73.180:底部填充材料

74.182:延伸部分

75.182a:第一侧壁

76.182b1,182b2:第二侧壁

77.182c:纵向

78.182e:边缘

79.182l:第一侧壁

80.182o:部分

81.182w1,182w2:第二侧壁

82.202:封装

83.202c:角落

84.204:存储器芯片

85.206:导电贯通孔

86.208:导电垫

87.3021,3022,3023,3024,3025,3026,3027,3028,3029,302

10

:封装部件

88.302c:角落

89.d:深度

90.d1,d2,d3,d4:距离

91.l:尺寸

92.r:区域

93.t:厚度

94.w:尺寸

95.np:中性点/几何中心

96.dnp:到中性点的距离

97.i-i:线

98.θ1,θ2:夹角

具体实施方式

99.以下的公开内容提供许多不同的实施例或范例以实施本公开的不同特征。以下描述具体的构件及其排列方式的实施例以阐述本公开。当然,这些实施例仅作为范例,而不该以此限定本公开的范围。例如,在说明书中叙述了一第一特征形成于一第二特征之上或上方,其可能包含第一特征与第二特征是直接接触的实施例,亦可能包含了有附加特征形成于第一特征与第二特征之间,而使得第一特征与第二特征可能未直接接触的实施例。另外,在本公开不同范例中可能使用重复的参考符号及/或标记,此重复为了简化与清晰的目的,并非用于限定所讨论的各个实施例及/或结构之间有特定的关系。

100.再者,空间相关用语,例如“在

…

下方”、“下方”、“较低的”、“在

…

上方”、“较高的”及类似的用语,是为了便于描述附图中一个元件或特征与另一个(些)元件或特征之间的关系。除了在附图中示出的方位外,这些空间相关用语意欲包含使用中或操作中的装置的不同方位。设备可能被转向不同方位(旋转90度或其他方位),则在此使用的空间相关词也可依此相同解释。

101.说明书中的用语“基本上(substantially)”,例如“基本上平坦”或“基本上共平面”等为本领域技术人员所能理解的。在一些实施例中,形容词可以基本上被去除。在适用的情况下,用语“基本上”也可以包括“全部(entirely)”、“完全(completely)”、“所有(all)”等的实施例。在适用的情况下,用语“基本上”也可以涉及90%或更高,例如95%或更高,特别是99%或更高,包括100%。此外,例如“基本上平行”或“基本上垂直”之类的用语应被解释成不排除相较于特定布置的微小偏差,并且例如可包括例如高达10

°

的偏差。用语“基本上”不排除“完全”,例如“基本上不含(substantially free)”y的组合物可以是完全不含y。

102.与特定距离或尺寸结合使用的用语,例如“约”,应被解释成不排除相较于特定距离或尺寸的微小偏差,并且可包括例如高达10%的偏差。用于数值x的用语“约”可能表示x

±

5或10%。

103.本公开的一些实施例被描述。可以在这些实施例中描述的阶段之前、期间及/或之后提供额外的操作。对于不同的实施例,可以替换或消除所描述的一些阶段。可以将附加特征添加到半导体装置结构中。对于不同的实施例,下面描述的一些特征可以被替换或消除。尽管讨论了一些具有以特定顺序执行的操作的实施例,但是这些操作可以以其他逻辑顺序来执行。

104.本公开的实施例可以与3d封装或3d-ic装置有关。也可以包括其他特征和工艺,例如,可以包括测试结构以帮助对3d封装或3d-ic装置进行验证测试。测试结构可以包括例如在一重分布层中或一基板上形成的测试垫,其允许测试3d封装或3d-ic、使用探针及/或探针卡等。验证测试可以在中间结构以及最终结构上执行。此外,本文中公开的结构和方法可以与结合已知良品晶粒(known good dies)的中间验证的测试方法结合使用,以提高产量并降低成本。

105.提供一封装结构的实施例。封装结构可以包括在基板上方的重分布结构以及在重分布结构上方并电耦接到基板的半导体晶粒。基板可以包括与半导体晶粒的角落重叠并填充有底部填充材料的沟槽。结果,可以减小或减轻集中在半导体晶粒的角落处的拉伸应力。因此,可以降低底部填充材料破裂的风险,从而提高封装结构的性能和可靠性。

106.图1a至图1g是示出根据本公开一些实施例的在形成一封装结构的各个中间阶段的剖面图。

107.根据一些实施例,接收或提供一载体基板102,如图1a所示。在一些实施例中,载体基板102是陶瓷基板、玻璃基板、聚合物基板、半导体基板或其他合适的基板。

108.根据一些实施例,在载体基板102上方设置一胶带104,如图1a所示。在一些实施例中,胶带104是对能量束照射敏感的。在一些实施例中,胶带104是由光热转换(light-to-heat conversion,lthc)材料制成或包括光热转换材料的一释放层。举例来说,在后续工艺中,可以使用激光束照射胶带104。照射可以允许形成在胶带104上方的封装结构与载体基板102分离。

109.根据一些实施例,在胶带104上方形成一重分布结构106,如图1a所示。重分布结构106配置用于布线,这使得能够形成具有扇出(fan-out)特征的封装结构。重分布结构106也可称作一中介层。根据一些实施例,重分布结构106具有面向载体基板102的底表面106b以及背对载体基板102的顶表面106a。

110.在一些实施例中,重分布结构106包括多个绝缘层例如绝缘层1141、1142、1143和1144、以及形成在所述绝缘层中的多个导电特征例如导电特征108、110和112。虽然图1a示出了四个绝缘层1141、1142、1143和1144,但是绝缘层的数量不以此限,且重分布结构106可以包括更少或更多的绝缘层。

111.在一些实施例中,导电特征108被绝缘层1141围绕及/或嵌入绝缘层1141中。在一些实施例中,导电特征108是导电通孔(vias)。在一些实施例中,导电特征108配置用于提供垂直电气布线。在一些实施例中,导电特征108将从重分布结构106的底表面106b暴露或突出,并用于固持或接收凸块下金属化(under bump metallurgy,ubm)结构和接合(bonding)元件。

112.在一些实施例中,导电特征110被绝缘层1142、1143和1144围绕及/或嵌入绝缘层1142、1143和1144中。在一些实施例中,导电特征110包括导电垫、导电线及/或导电迹线,配

置用于提供水平电气布线。在一些实施例中,导电特征108与绝缘层1142中的导电特征110(例如,导电垫)接触。

113.在一些实施例中,导电特征112被绝缘层1142、1143和1144围绕及/或嵌入绝缘层1142、1143和1144中。在一些实施例中,导电特征112是导电通孔,并配置用于提供垂直电气布线。在一些实施例中,导电特征112落在(land)导电特征110的导电垫上,从而将不同绝缘层114中的导电特征110电耦接。在一些实施例中,绝缘层1144中的导电特征112从重分布结构106的绝缘层1144的顶表面106a暴露及/或突出,并用于固持或接收凸块下金属化结构和接合元件。

114.在一些实施例中,绝缘层114可以由一或多种聚合物材料制成。聚合物材料可以包括聚苯并恶唑(polybenzoxazole,pbo)、苯并环丁烯(benzocyclobutene,bcb)、聚酰亚胺(polyimide,pi)、环氧基树脂、一或多种其他合适的聚合物材料、或其组合。在一些实施例中,聚合物材料是光敏的,因此可以使用光刻工艺在绝缘层1141、1142、1143和1144中形成具有所需图案的开口。在替代实施例中,绝缘层114由一或多种介电材料制成,例如氧化硅、氮化硅及/或氮氧化硅。

115.在一些实施例中,导电特征108、110和112由金属材料制成,例如铜、铝、金、钯、钴、钛、镍、银、石墨烯、一或多种其他合适的导电材料、其合金、或其组合。在一些实施例中,导电特征108、110和112由非焊料(non-solder)金属材料制成。在一些实施例中,导电特征108、110和112包括多个子层,例如,导电特征108、110和112中的每一个都包含多个子层,包括ti/cu、ti/ni/cu、ti/cu/ti、al/ti/ni/ag、其他合适的子层、或其组合。

116.重分布结构106的形成可以涉及多个沉积工艺、多个图案化工艺及/或多个平坦化工艺。沉积工艺可用于形成绝缘层及/或导电层。沉积工艺可以包括旋涂工艺、电镀工艺、化学镀工艺、化学气相沉积(chemical vapor deposition,cvd)工艺、物理气相沉积(physical vapor deposition,pvd)工艺、原子层沉积(atomic layer deposition,ald)工艺、一或多种其他适用的工艺、或其组合。

117.图案化工艺可用于图案化形成的绝缘层及/或形成的导电层。图案化工艺可以包括光刻工艺、能量束钻孔工艺(例如,激光束钻孔工艺、离子束钻孔工艺或电子束钻孔工艺)、蚀刻工艺、机械钻孔工艺、一或多种其他适用的工艺、或其组合。

118.平坦化工艺可用于为形成的绝缘层及/或形成的导电层提供平坦的顶表面,以利后续的工艺。平坦化工艺可以包括机械研磨工艺、化学机械抛光(chemical mechanical polishing,cmp)工艺、干式抛光工艺、一或多种其他适用的工艺、或其组合。

119.图1a-1是根据本公开一些实施例的图1a中所示的封装结构的平面图。图1a-1示出了重分布结构106,其可以包括扇入(fan-in)区106i以及与扇入区106i邻接的扇出(fan-out)区106o,半导体晶粒将相应地设置在扇入区106i中。根据一些实施例,扇出区106o连续地围绕扇入区106i。

120.再回到图1a,根据一些实施例,在重分布结构106的顶表面106a上方形成凸块下金属化结构116。在一些实施例中,凸块下金属化结构116对应并接触从绝缘层1144暴露的导电通孔112。

121.在一些实施例中,凸块下金属化结构116用于固持或接收接合元件(例如焊球)。凸块下金属化(ubm)材料可以用于增加焊料的粘附性(例如,通过提供焊料的可焊性和润湿

性)、提供焊料扩散屏障、在焊料与导电通孔112之间的连接中提供一些应力消除、以及在与导电通孔112的接触中提供低阻抗。

122.在一些实施例中,凸块下金属化结构116由金属材料制成或包括金属材料,例如钛、铜、镍、钽、钒、铬、金、钨、其合金、其多层、或其组合。在一些实施例中,凸块下金属化结构116由非焊料金属材料制成。在一些实施例中,使用溅镀、蒸镀、电镀、其他合适的技术及/或其组合来形成凸块下金属化结构116。

123.根据一些实施例,半导体晶粒120设置在重分布结构106的顶表面106a上方,如图1b所示。根据一些实施例,半导体晶粒120设置在重分布结构106的扇入区106i内。

124.半导体晶粒120可以包括应用处理器、电源管理集成电路、逻辑装置、存储器装置(例如,静态随机存取存储器(static random access memories,srams))、射频(radio frequency,rf)装置、输入/输出(input/output,i/o)装置、系统芯片(system-on-chip,soc)装置、特定应用集成电路(application-specific integrated circuit,asic)、一或多种其他合适的电路、或其组合。

125.在一些实施例中,半导体晶粒120包括具有背面122b和正面122f的半导体基板122。在一些实施例中,半导体晶粒120也包括形成在半导体基板122的正面122f中及/或上的集成电路124。在一些实施例中,半导体晶粒120也包括互连结构126,互连结构126被金属间(intermetal,imd)介电层128围绕并电耦接到集成电路124。在一些实施例中,半导体晶粒120也包括导电垫130,导电垫130形成在互连结构126上方并电耦接到互连结构126。在一些实施例中,半导体晶粒120也包括钝化层132,钝化层132部分地覆盖导电垫130并具有部分地暴露导电垫130的开口。

126.根据一些实施例,在半导体晶粒120的导电垫130上方形成凸块下金属化结构134。凸块下金属化结构134穿过钝化层132并覆盖导电垫130的暴露表面。

127.在一些实施例中,凸块下金属化结构134用于固持或接收接合元件136。在一些实施例中,凸块下金属化结构134由金属材料制成或包括金属材料,例如钛、铜、镍、钽、钒、铬、金、钨、其合金、其多层、或其组合。在一些实施例中,凸块下金属化结构134由非焊料金属材料制成。在一些实施例中,使用溅镀、蒸镀、电镀、其他合适的技术及/或其组合来形成凸块下金属化结构134。

128.在一些实施例中,执行电镀工艺以在凸块下金属化结构134上方形成接合元件136。在替代实施例中,接合元件136被预先形成并放置在凸块下金属化结构116上方。

129.在一些实施例中,接合元件136是焊料接点、微凸块、焊料凸块、焊球、球栅阵列(ball grid array,bga)球、受控塌陷芯片连接(controlled collapse chip connection,c4)凸块、其他合适的接合元件及/或其组合。在一些实施例中,接合元件136是含锡焊球凸块或焊球。含锡焊球凸块或焊球可以包括铜、银、金、铝、铅、一或多种其他合适的材料、或其组合。在一些实施例中,接合元件136不含铅。

130.根据一些实施例,半导体晶粒120的导电垫130通过凸块下金属化结构134、接合元件136以及凸块下金属化结构116接合到重分布结构106的导电通孔112。在一些实施例中,进行热回焊操作。在一些实施例中,接合元件136对应并连接凸块下金属化结构134和凸块下金属化结构116。因此,根据一些实施例,集成电路124电耦接到重分布结构106的导电特征108、110和112。

131.图1b-1是根据本公开一些实施例的图1b中所示的封装结构的平面图。在一些实施例中,半导体晶粒120并排布置。

132.在一些实施例中,半导体晶粒120具有矩形或正方形轮廓,如图1b-1所示。在一些实施例中,半导体晶粒120的边缘(或外围)与重分布结构106的扇入区106i和扇出区106o之间的边界对齐。在一些实施例中,每个半导体晶粒120的边缘包括四个侧壁120s1、120s2、120s3和120s4。侧壁120s1和120s2相交于角落120c1,侧壁120s2和120s3相交于角落120c2,侧壁120s3和120s4相交于角落120c3,侧壁120s4和120s1相交于角落120c4。

133.在一些实施例中,一个半导体晶粒120的侧壁120s3及角落120c2和120c3紧邻另一个半导体晶粒120的侧壁120s3及角落120c2和120c3设置。在一些实施例中,半导体晶粒120的角落120c1和120c4不与任何其他半导体晶粒相邻设置。因此,角落120c2和120c3被称为封闭(closed)角落,而角落120c1和120c4被称为开放(open)角落。

134.根据一些实施例,在重分布结构106的顶表面106a上方形成一底部填充材料138,从而密封及/或围绕半导体晶粒120、接合元件136以及凸块下金属化结构116和134,如图1c所示。根据一些实施例,底部填充材料138填充接合元件136之间的间隙。

135.在一些实施例中,底部填充材料138是电绝缘粘合剂,用于保护接合元件136以及凸块下金属化结构116和134及/或固定半导体晶粒120。在一些实施例中,底部填充材料138由环氧树脂、树脂、环氧模塑料、其他合适的底部填充材料及/或其组合。

136.根据一些实施例,在重分布结构106的顶表面106a上方形成一模塑料(molding compound)140,从而密封及/或围绕底部填充材料138和半导体晶粒120,如图1c所示。在一些实施例中,模塑料140是单层薄膜或复合堆叠。在一些实施例中,模塑料140包括各种材料,例如模制底部填充物(molding underfill)、环氧树脂、树脂等。在一些实施例中,模塑料140具有高导热性、低吸湿率和高抗弯强度。

137.根据一些实施例,然后将模塑料140平坦化,直到暴露出半导体基板122的背面122b。平坦化工艺可以包括机械研磨工艺、化学机械抛光(cmp)工艺、干式抛光工艺、一或多种其他适用的工艺、或其组合。

138.根据一些实施例,将图1c的结构的上表面(例如,半导体基板122的背面122b)附接到一载体基板144,然后倒置,如图1d所示。根据一些实施例,载体基板144通过一胶带142附接到半导体基板122和模塑料140,从而覆盖半导体基板122和模塑料140。根据一些实施例,载体基板144配置用于保护半导体基板122在随后的工艺中免受损坏。

139.在一些实施例中,载体基板144是陶瓷基板、玻璃基板、聚合物基板、半导体基板或其他合适的基板。在一些实施例中,胶带142是由光热转换(lthc)材料制成或包括光热转换材料的一释放层。在一些实施例中,胶带142由与胶带104不同的材料制成。

140.根据一些实施例,然后通过将胶带104与载体基板102和重分布结构106分离,将载体基板102从重分布结构106上取下,如图1e所示。举例来说,可以通过用能量束(例如激光束、紫外光或其他合适的能量束)照射结构来执行释放工艺。在照射之后,胶带104的黏合特性可以被破坏或降低。在一些实施例中,即使被能量束照射,胶带142也可以保持黏性。根据一些实施例,在释放工艺之后,暴露出重分布结构106的绝缘层1141。

141.根据一些实施例,对重分布结构106的绝缘层1141进行平坦化工艺,直到导电特征108从绝缘层1141暴露出,如图1e所示。平坦化工艺可以包括机械研磨工艺、化学机械抛光

(cmp)工艺、干式抛光工艺、一或多种其他适用的工艺、或其组合。根据一些实施例,执行锯切操作以将结构切割成彼此分离的多个封装结构146,如图1e所示。图1e示出了得到的封装结构146之一者的剖面图。

142.图1e-1是根据本公开一些实施例的图1e中所示的封装结构的平面图。在一些实施例中,重分布结构106具有矩形或正方形轮廓。在一些实施例中,重分布结构106的边缘(或外围)包括四个侧壁106s1、106s2、106s3和106s4。侧壁106s1和106s2相交于角落106c1,侧壁106s2和106s3相交于角落106c2,侧壁106s3和106s4相交于角落106c3,侧壁106s4和106s1相交于角落106c4。

143.图1e-1也示出重分布结构106的中性点(neutral point)np。根据一些实施例,重分布结构106的中性点是指重分布结构106的最中心点。在一些实施例中,在平面图中,重分布结构106的中性点np是重分布结构106的轮廓的几何中心,例如对角线的交点。

144.根据一些实施例,然后通过将胶带142与载体基板144和半导体晶粒120(及模塑料140)分离,将载体基板144从封装结构146中取出。举例来说,可以通过用能量束(例如激光束、紫外光或其他合适的能量束)照射结构来执行释放工艺。在照射之后,胶带142的粘合特性可以被破坏或降低。

145.根据一些实施例,封装结构146设置在一基板160上方并通过接合元件150接合到基板160,如图1f所示。在一些实施例中,基板160是印刷电路板(printed circuit board,pcb)。在替代实施例中,基板160是中介层基板,其后续可以接合到另一基板。在一些实施例中,基板160上制造有预定的功能电路。在一些实施例中,基板160的厚度t介于约1毫米至约2.5豪米的范围。

146.在一些实施例中,基板160包括多个绝缘层例如绝缘层1661、1662、1663、1664和1665,以及形成在所述绝缘层中的多个导电特征例如导电特征162和164。虽然图1f示出了五个绝缘层1661、1662、1663、1664和1665,但是绝缘层的数量不以此限,且基板160可以包括更少或更多的绝缘层。此外,基板160可以包括主动电路部件,例如晶体管、二极管等。

147.在一些实施例中,导电特征162被绝缘层166

1-1664围绕及/或嵌入绝缘层166

1-1664中。在一些实施例中,导电特征162是导电通孔,配置用于提供垂直电气布线。在一些实施例中,导电特征164被绝缘层166

1-1665围绕及/或嵌入绝缘层166

1-1665中。在一些实施例中,导电特征164包括导电垫、导电线及/或导电迹线,配置用于提供水平电气布线。在一些实施例中,导电特征162落在导电特征164的导电垫上,从而将不同绝缘层166中的导电特征164电耦接。

148.在一些实施例中,绝缘层166和底部填充材料180由不同的绝缘材料制成。在一些实施例中,绝缘层166可以由味之素积层膜(ajinomoto build-up film,abf)、其他适用的材料及/或其组合制成。

149.在一些实施例中,导电特征162和164由金属材料制成,例如铜、铝、金、钯、钴、钛、镍、银、石墨烯、一或多种其他合适的导电材料、其合金、或其组合。

150.在一些实施例中,基板160也包括一阻焊层168,阻焊层168设置在绝缘层1661上方并部分地覆盖绝缘层1661中的导电特征164。在一些实施例中,绝缘层1661中的导电特征164是导电垫,用于固持或接收接合元件150。

151.根据一些实施例,基板160也包括预先形成的沟槽170。在一些实施例中,沟槽170

直接位于(located directly)半导体晶粒120的开放角落120c1和120c4下方。在一些实施例中,沟槽170从基板160的顶表面延伸到基板160的内部。

152.举例来说,沟槽170的底表面可以位于绝缘层166

2-1665之一者内,例如在绝缘层1663内,如图1f所示。在一些实施例中,沟槽170的深度d介于约50微米至约250微米的范围。在一些实施例中,深度d与厚度t的比值介于约0.02至约0.25的范围。根据一些实施例,导电特征164没有从沟槽170中暴露出。在一些实施例中,没有一个接合元件直接设置在沟槽170上方。

153.在一些实施例中,接合工艺包括在从绝缘层1141暴露出的导电特征108上方形成凸块下金属化结构148。在一些实施例中,凸块下金属化结构148对应并与导电特征108接触。

154.在一些实施例中,凸块下金属化结构148用于固持或接收接合元件150。在一些实施例中,凸块下金属化结构148由金属材料制成或包括金属材料,例如钛、铜、镍、钽、钒、铬、金、钨、其合金、其多层、或其组合。在一些实施例中,凸块下金属化结构148由非焊料金属材料制成。在一些实施例中,使用溅镀、蒸镀、电镀、其他合适的技术及/或其组合来形成凸块下金属化结构148。

155.在一些实施例中,执行电镀工艺以在凸块下金属化结构148上方形成接合元件150。在替代实施例中,接合元件150被预先形成并放置在基板160的导电垫162上方。

156.在一些实施例中,接合元件150是焊料接点、受控塌陷芯片连接(c4)凸块、焊料凸块、焊球、球栅阵列(ball grid array,bga)球、其他合适的接合元件及/或其组合。在一些实施例中,接合元件150是含锡焊球凸块或焊球。含锡焊球凸块或焊球可以包括铜、银、金、铝、铅、一或多种其他合适的材料、或其组合。在一些实施例中,接合元件150不含铅。

157.根据一些实施例,封装结构146的重分布结构106的导电特征108通过凸块下金属化结构148和接合元件150接合到基板160的绝缘层1661中的导电特征164(例如,导电垫)。在一些实施例中,进行热回焊操作。根据一些实施例,接合元件150的较低部分被阻焊层160围绕。在一些实施例中,接合元件150对应并连接凸块下金属化结构148和导电垫162。因此,根据一些实施例,半导体晶粒120的集成电路124电耦接到基板160的导电特征及/或功能电路。

158.图1f-1是根据本公开一些实施例的图1f中所示的封装结构的平面图,其中图1f是沿图1f-1中的线i-i获取的。图1f-1示出了半导体晶粒120和重分布结构106投影在基板160上的足迹(或投影)。在一些实施例中,沟槽170直接位于半导体晶粒120的开放角落120c1和120c4下方并与开放角落120c1和120c4重叠。在一些实施例中,没有沟槽170直接位于半导体晶粒120的封闭角落120c2和120c3下方。

159.图1f-2是图1f-1中所示的区域r的放大平面图,示出根据本公开一些实施例的靠近一个半导体晶粒120的一个开放角落120c1的沟槽170的细节。为了说明简单,下面使用靠近一个半导体晶粒120的开放角落120c1的沟槽170来描述封装结构的特征,但是这些特征可适用于封装结构的其他区域,例如靠近所述半导体晶粒120的开放角落120c4的沟槽170以及靠近其他半导体晶粒120的开放角落120c1和120c4的沟槽170。

160.根据一些实施例,半导体晶粒120的角落120c1与沟槽170重叠。在图1f-2中,根据一些实施例,半导体晶粒120的角落120c1局限(confined)在沟槽170的区域内。根据一些实

施例,沟槽170的大部分位于重分布结构106的区域内。在所示实施例中,沟槽170分别在侧壁106s1和侧壁106s2处包括在重分布结构106的区域之外的两个部分170o。

161.基板160与半导体晶粒120之间可能存在较大的热膨胀系数(coefficients of thermal expansion,cte)差异,因此在可靠性测试、封装结构的操作及/或热处理过程中可能产生拉伸应力(tensile stress)并将其施加到底部填充材料138。拉伸应力可能集中,尤其是在半导体晶粒120的开放角落120c1和120c4处。拉伸应力的集中可能导致在底部填充材料138内形成裂纹。裂纹可能传播到模塑料140中。

162.根据本公开一些实施例,基板160包括直接位于开放角落120c1和120c4下方的沟槽170,从而可减小或减轻集中在半导体晶粒120的角落处的拉伸应力。结果,可以降低底部填充材料138破裂的风险,从而提高封装结构的性能和可靠性。

163.在一些实施例中,沟槽170具有矩形轮廓,如图1f-2所示。沟槽170的形状不以此为限,且沟槽170可以包括弯曲/弧形(arcuate)侧壁。在一些实施例中,沟槽170沿其纵向170c延伸。根据一些实施例,纵向170c也是沟槽170的对称轴。

164.根据一些实施例,沟槽170的边缘包括平行于纵向170c的第一侧壁170l(例如,矩形轮廓的长边)以及垂直于纵向170c的第二侧壁170w1和170w2(例如,矩形轮廓的短边)。在一些实施例中,第一侧壁170l以及第二侧壁170w1和170w2为线性表面。根据一些实施例,第二侧壁170w1位于半导体晶粒120的区域内,而第二侧壁170w2位于半导体晶粒120的区域之外。

165.在一些实施例中,沟槽170具有沿纵向170c测量的尺寸l(即,沟槽170的长度)。在一些实施例中,尺寸l介于约1.0毫米至约2.0毫米的范围。在一些实施例中,沟槽170具有沿垂直于纵向170c的方向测量的尺寸w(即,沟槽170的宽度)。在一些实施例中,尺寸w介于约0.5毫米至约1.0毫米的范围。在一些实施例中,沟槽170的纵横比(w/d)介于约2至约20的范围。

166.举例来说,如果尺寸l及/或尺寸w太大,可能会降低所得封装结构的布线密度。如果尺寸l及/或尺寸w太小,则集中在半导体晶粒120的角落处的拉伸应力不能得到有效缓解,从而增加了底部填充材料138破裂的风险。

167.在一些实施例中,尺寸l大于尺寸w。如果尺寸l小于尺寸w,则集中在半导体晶粒120的角落处的拉伸应力不能得到有效缓解,从而增加了底部填充材料138破裂的风险。

168.在一些实施例中,沟槽170的纵向170c基本上平行于到中性点的距离(distance to a neutral point,dnp)的方向。dnp方向定义为从重分布结构106的几何中心np到半导体晶粒120的开放角落(例如,角落120c1及/或角落120c4)。

169.在所示实施例中,dnp方向与纵向170c的夹角约为0度。也就是说,在所示实施例中,dnp方向与第二侧壁170w1的夹角θ1约为90度。在替代实施例中,dnp方向与纵向170c的夹角大于0度且小于约15度。举例来说,如果dnp方向与纵向170c的夹角太大,则集中在半导体晶粒120的角落处的拉伸应力不能得到有效缓解,从而增加了底部填充材料138破裂的风险。

170.在一些实施例中,dnp方向与纵向170c对齐或共线。在一些实施例中,纵向170c穿过角落120c1。

171.在一些实施例中,沿纵向170c测量时,第二侧壁170w1(在半导体晶粒120的区域

内)与角落120c1相距最小距离d1。在一些实施例中,距离d1介于约0.5毫米至约1.5毫米的范围。在一些实施例中,距离d1为尺寸l的约0.5至约0.75。

172.在一些实施例中,沿纵向170c测量时,第二侧壁170w2(在半导体晶粒120的区域之外)与角落120c相距最小距离d2。在一些实施例中,距离d2介于约0.25毫米至约1毫米的范围。在一些实施例中,距离d1及距离d2的总和等于尺寸l。在一些实施例中,距离d2为尺寸l的约0.25至约0.5。

173.举例来说,如果距离d1及/或距离d2太大,可能会降低所得封装结构的布线密度。如果距离d1及/或距离d2太小,则集中在半导体晶粒120的角落处的拉伸应力不能得到有效缓解,从而增加了底部填充材料138破裂的风险。

174.在一些实施例中,距离d1大于或等于距离d2。在一些实施例中,距离d1与距离d2的比值介于约1至约3的范围,例如约1.25至约1.75。举例来说,如果距离d1与距离d2的比值太大或太小,则集中在半导体晶粒120的角落处的拉伸应力不能得到有效缓解,从而增加了底部填充材料138破裂的风险。

175.在一些实施例中,沿纵向170c测量时,第二侧壁170w2与重分布结构106的角落106c1相距最小距离d3。在一些实施例中,距离d3小于约0.1毫米。在一些实施例中,距离d3小于距离d2。

176.根据一些实施例,一底部填充材料180形成在基板160的上表面上方,并密封及/或围绕封装结构146、凸块下金属化结构148和接合元件150,如图1g所示。根据一些实施例,底部填充材料180填充接合元件150之间的间隙。根据一些实施例,底部填充材料180填充沟槽170。底部填充材料180嵌入基板160中的部分被称为延伸部分182。在一些实施例中,延伸部分182通过绝缘层166与导电特征162和164隔离。根据一些实施例,底部填充材料180覆盖模塑料140的侧壁和重分布结构106的侧壁。

177.在一些实施例中,底部填充材料180是电绝缘粘合剂,用于保护结合元件150及/或固定封装结构146。在一些实施例中,底部填充材料180由环氧树脂、树脂、环氧模塑料、其他合适的底部填充材料及/或其组合。

178.图1g-1是图1g对应于图1f-1中所示的区域r的放大平面图,示出根据本公开一些实施例的延伸部分182的细节。图1g-1示出了半导体晶粒120、重分布结构106和延伸部分182投影在基板160上的足迹(或投影)。为了说明简单,下面使用靠近一个半导体晶粒120的开放角落120c1的延伸部分182来描述封装结构的特征,但是这些特征可适用于封装结构的其他区域,例如靠近所述半导体晶粒120的开放角落120c4的延伸部分182以及靠近其他半导体晶粒120的开放角落120c1和120c4的延伸部分182。

179.根据一些实施例,延伸部分182直接位于半导体晶粒120的角落120c1下方并与角落120c1重叠。在图1g-1中,根据一些实施例,半导体晶粒120的角落120c1局限在延伸部分182的区域内。根据一些实施例,延伸部分182的大部分位于重分布结构106的区域内。在所示实施例中,延伸部分182分别在侧壁106s1和侧壁106s2处包括在重分布结构106的区域之外的两个部分182o。

180.在一些实施例中,填入沟槽170中的延伸部分182具有与沟槽170基本上相同的轮廓,例如矩形轮廓,如图1g-1所示。在一些实施例中,延伸部分182沿其纵向182c延伸。根据一些实施例,纵向182c也是延伸部分182的对称轴。

181.根据一些实施例,延伸部分182的边缘包括平行于纵向182c的第一侧壁182l(例如,矩形轮廓的长边)以及垂直于纵向182c的第二侧壁182w1和182w2(例如,矩形轮廓的短边)。在一些实施例中,第一侧壁182l以及第二侧壁182w1和182w2为线性表面。根据一些实施例,第二侧壁182w1位于半导体晶粒120的区域内,而第二侧壁182w2位于半导体晶粒120的区域之外。

182.在一些实施例中,延伸部分182具有沿纵向182c测量的尺寸l(即,延伸部分182的长度)。在一些实施例中,尺寸l介于约1.0毫米至约2.0毫米的范围。在一些实施例中,延伸部分182具有沿垂直于纵向182c的方向测量的尺寸w(即,延伸部分182的宽度)。在一些实施例中,尺寸w介于约0.5毫米至约1.0毫米的范围。在一些实施例中,尺寸l大于尺寸w。

183.在一些实施例中,延伸部分182的纵向182c基本上平行于dnp方向。在一些实施例中,dnp方向与纵向182c的夹角约为0度。也就是说,在所示实施例中,dnp方向与第二侧壁182w1的夹角θ1约为90度。在替代实施例中,dnp方向与纵向182c的夹角大于0度且小于约15度。

184.在一些实施例中,dnp方向与纵向182c对齐或共线。在一些实施例中,纵向182c穿过角落120c1。

185.在一些实施例中,沿纵向182c测量时,第二侧壁182w1(在半导体晶粒120的区域内)与角落120c1相距最小距离d1。在一些实施例中,距离d1介于约0.5毫米至约1.5毫米的范围。在一些实施例中,距离d1为尺寸l的约0.5至约0.75。

186.在一些实施例中,沿纵向182c测量时,第二侧壁182w2(在半导体晶粒120的区域之外)与角落120c1相距最小距离d2。在一些实施例中,距离d2介于约0.25毫米至约1毫米的范围。在一些实施例中,距离d1及距离d2的总和等于尺寸l。在一些实施例中,距离d2为尺寸l的约0.25至约0.5。

187.在一些实施例中,距离d1大于或等于距离d2。在一些实施例中,距离d1与距离d2的比值介于约1至约3的范围,例如约1.25至约1.75。

188.在一些实施例中,沿纵向182c测量时,第二侧壁182w2与重分布结构106的角落106c1相距最小距离d3。在一些实施例中,距离d3小于约0.1毫米。在一些实施例中,距离d3小于距离d2。

189.根据本公开一些实施例,延伸部分182直接位于半导体晶粒120的开放角落120c1和120c4下方并嵌入基板160中。结果,可以降低底部填充材料138破裂的风险,从而提高封装结构的性能和可靠性。

190.图2是根据本公开一些实施例的图1g-1的修改。图2的封装结构类似于图1g-1的封装结构,除了延伸部分182没有任何部分在重分布结构106之外。

191.根据一些实施例,延伸部分182基本上完全局限在重分布结构106的区域内。因此,根据一些实施例,延伸部分182没有任何部分在重分布结构106之外。

192.图3是根据本公开一些实施例的图1g-1的修改。图3的封装结构类似于图1g-1的封装结构,除了延伸部分182的第二侧壁182w2(在半导体晶粒120之外)穿过重分布结构106的角落106c1之外。因此,第二侧壁182w2与角落106c1之间的最小距离d3为零。

193.图4是根据本公开一些实施例的图1g-1的修改。图4的封装结构类似于图1g-1的封装结构,除了延伸部分182的纵向182c不平行于dnp方向之外。

194.在所示实施例中,dnp方向与纵向182c的夹角θ2大于0度且小于约15度。也就是说,在所示实施例中,dnp方向与第二侧壁182w1的夹角θ2大于75度且小于90度。

195.图5是根据本公开一些实施例的图1g-1的修改。图5的封装结构类似于图1g-1的封装结构,除了dnp方向与纵向182c不对齐或共线之外。

196.在一些实施例中,纵向182c从dnp方向偏移一距离d4。在一些实施例中,纵向182c不穿过角落120c1。在所示实施例中,延伸部分182仅在侧壁106s2处包括在重分布结构106的区域之外的一部分。

197.在一些实施例中,距离d4与尺寸w的比值小于约0.2。举例来说,如果距离d4与尺寸w的比值太大或太小,则集中在半导体晶粒120的角落处的拉伸应力不能得到有效缓解,从而增加了底部填充材料138破裂的风险。

198.图6-1是根据本公开一些实施例的图1g的封装结构的修改的平面图。图6-1的封装结构类似于图1g-1的封装结构,除了延伸部分182具有圆角矩形轮廓之外。

199.图6-2是根据本公开一些实施例的图6-1中所示的区域r的放大平面图。为了说明简单,下面使用靠近一个半导体晶粒120的开放角落120c1的延伸部分182来描述封装结构的特征,但是这些特征可适用于封装结构的其他区域,例如靠近所述半导体晶粒120的开放角落120c4的延伸部分182以及靠近其他半导体晶粒120的开放角落120c1和120c4的延伸部分182。

200.根据一些实施例,延伸部分182的边缘包括第一侧壁182a以及第二侧壁182b1和182b2。在一些实施例中,第一侧壁182a平行于纵向182c并且是线性表面。在一些实施例中,第二侧壁182b1和182b2是弧形表面。举例来说,第一侧壁182a可以在第一侧壁182a与第二侧壁182b1及/或第二侧壁182b2的连接处与第二侧壁182b1及/或182b2相切(tangent)。

201.在一些实施例中,第二侧壁182b1位于半导体晶粒120的区域内,而第二侧壁182b2位于半导体晶粒120的区域内之外。根据一些实施例,延伸部分182基本上完全局限在重分布结构106的区域内。

202.在一些实施例中,延伸部分182具有沿纵向182c测量的最大尺寸l。在一些实施例中,尺寸l介于约1.0毫米至约2.0毫米的范围。在一些实施例中,延伸部分182具有沿垂直于纵向182c的方向测量的最大尺寸w。在一些实施例中,尺寸w介于约0.5毫米至约1.0毫米的范围。在一些实施例中,尺寸l大于尺寸w。在一些实施例中,第二侧壁182b1及/或182b2的曲率半径基本上等于尺寸w的一半。

203.在一些实施例中,沿纵向182c测量时,第二侧壁182b1(在半导体晶粒120的区域内)与角落120c1相距最大距离d1。在一些实施例中,距离d1介于约0.5毫米至约1.5毫米的范围。在一些实施例中,距离d1为尺寸l的约0.5至约0.75。

204.在一些实施例中,沿纵向182c测量时,第二侧壁182b2(在半导体晶粒120的区域之外)与角落120c1相距最大距离d2。在一些实施例中,距离d2介于约0.25毫米至约1毫米的范围。在一些实施例中,距离d1及距离d2的总和等于尺寸l。在一些实施例中,距离d2为尺寸l的约0.25至约0.5。

205.在一些实施例中,距离d1大于或等于距离d2。在一些实施例中,距离d1与距离d2的比值介于约1至约3的范围,例如约1.25至约1.75。

206.在一些实施例中,沿纵向182c测量时,第二侧壁182b2与重分布结构106的角落

106c1相距最小距离d3。在一些实施例中,距离d3小于约0.1毫米。在一些实施例中,距离d3小于距离d2。

207.图7-1是根据本公开一些实施例的图1g的封装结构的修改的平面图。图7-1的封装结构类似于图1g-1的封装结构,除了延伸部分182的边缘182e具有椭圆形轮廓之外。

208.图7-2是根据本公开一些实施例的图7-1中所示的区域r的放大平面图。为了说明简单,下面使用靠近一个半导体晶粒120的开放角落120c1的延伸部分182来描述封装结构的特征,但是这些特征可适用于封装结构的其他区域,例如靠近所述半导体晶粒120的开放角落120c4的延伸部分182以及靠近其他半导体晶粒120的开放角落120c1和120c4的延伸部分182。

209.根据一些实施例,延伸部分182基本上完全局限在重分布结构106的区域内。在一些实施例中,延伸部分182具有沿纵向182c测量的尺寸l(即,椭圆形轮廓的长轴)。在一些实施例中,尺寸l介于约1.0毫米至约2.0毫米的范围。在一些实施例中,延伸部分182具有沿垂直于纵向182c的方向测量的尺寸w(即,椭圆形轮廓的短轴)。在一些实施例中,尺寸w介于约0.5毫米至约1.0毫米的范围。在一些实施例中,尺寸l大于尺寸w。

210.在一些实施例中,沿纵向182c测量时,边缘182e在半导体晶粒120的区域内的部分与角落120c1相距最大距离d1。在一些实施例中,距离d1介于约0.5毫米至约1.5毫米的范围。在一些实施例中,距离d1为尺寸l的约0.5至约0.75。

211.在一些实施例中,沿纵向182c测量时,边缘182e在半导体晶粒120的区域之外的部分与角落120c1相距最大距离d2。在一些实施例中,距离d2介于约0.25毫米至约1毫米的范围。在一些实施例中,距离d1及距离d2的总和等于尺寸l。在一些实施例中,距离d2为尺寸l的约0.25至约0.5。

212.在一些实施例中,距离d1大于或等于距离d2。在一些实施例中,距离d1与距离d2的比值介于约1至约3的范围,例如约1.25至约1.75。

213.在一些实施例中,沿纵向182c测量时,边缘182e在半导体晶粒120的区域之外的部分与重分布结构106的角落106c1相距最小距离d3。在一些实施例中,距离d3小于约0.1毫米。在一些实施例中,距离d3小于距离d2。

214.图8是根据本公开一些实施例的图1g中所示的剖面图的修改。图8的封装结构类似于图1g的封装结构,除了图8的封装结构包括一封装202之外。

215.根据一些实施例,封装202设置在重分布结构106的顶表面106a上方,如图8所示。在一些实施例中,封装202包括高带宽存储器(high bandwidth memory,hbm)装置。举例来说,封装202包括多个堆叠的存储器芯片204以及与存储器芯片204电耦接的导电贯通孔206。根据一些实施例,封装202也包括导电垫208,导电垫208与导电贯通孔206接触并通过接合元件136和凸块下金属化结构116接合到重分布结构106的导电通孔112。因此,根据一些实施例,封装202电耦接到基板160。

216.图8中所示的封装202的部件仅用于说明目的。在替代实施例中,封装202是芯片级封装(chip-scale package,csp)、基板上晶圆上芯片(chip on wafer on substrate,cowos)封装、系统整合芯片(system on integrated chip,soic)封装及/或三维集成电路(three dimensional integrated circuit,3dic)。

217.根据一些实施例,基板160包括预先形成的沟槽170。在一些实施例中,沟槽170直

接位于封装202的开放角落下方。根据一些实施例,底部填充材料180包括填充沟槽170的延伸部分182。

218.图8-1是根据本公开一些实施例的图8中所示的封装结构的平面图,其中图8是沿图8-1中的线i-i获取的。图8-1示出了半导体晶粒120、封装202、重分布结构106和延伸部分182投影在基板160上的足迹(或投影)。根据一些实施例,延伸部分182与封装202的开放角落202c重叠,如图8-1所示。

219.图8-2是图8-1中所示的区域r的放大平面图,示出根据本公开一些实施例的靠近封装202的一个开放角落202c的延伸部分182的细节。图8-2中所示的延伸部分182的配置与图1g-1中所示的延伸部分182的配置基本上相同,因此不再重复描述。此外,可以对图8-2中的延伸部分182进行如上面参照图2、3、4、5、6-2及/或7-2所描述的修改。

220.根据本公开一些实施例,延伸部分182直接位于装202的开放角落202c下方并嵌入基板160,因此可以减小或减轻集中在封装202的角落处的拉伸应力。结果,可以降低底部填充材料138破裂的风险,从而提高封装结构的性能和可靠性。

221.图9是根据本公开一些实施例的图8-1的封装结构的修改的平面图。图9的封装结构类似于图8-1的封装结构,除了封装结构包括多个封装部件302之外。

222.根据一些实施例,封装部件302(包括封装部件302

1-302

10

)可以是上述的半导体晶粒120或封装202。举例来说,封装部件302

1-3022可以是包括soc装置的半导体晶粒,而封装部件302

3-302

10

可以是包括hbm装置的封装。

223.根据一些实施例,每个封装部件302包括通过接合元件136和凸块下金属化结构116接合到重分布结构106的导电通孔112的导电垫(未示出)。因此,根据一些实施例,封装部件302电耦接到基板160。

224.在一些实施例中,封装部件3023、3026、3027和302

10

的每一者具有不与任何封装部件相邻设置的一开放角落302c。根据一些实施例,基板160包括预先形成的沟槽170。在一些实施例中,沟槽170直接位于封装部件3023、3026、3027和302

10

的开放角落302c下方。根据一些实施例,底部填充材料180包括填充沟槽170的延伸部分182。

225.在一些实施例中,没有沟槽170直接位于封装部件302

1-302

10

的封闭角落下方,该些封闭角落紧邻其他封装部件设置。

226.根据一些实施例,延伸部分182与封装部件3023、3026、3027和302

10

的开放角落302c重叠,如图9所示。图9中所示的延伸部分182的配置与图1g-1中所示的延伸部分182的配置基本上相同,因此不再重复描述。此外,可以对图9中的延伸部分182进行如上面参照图2、3、4、5、6-2及/或7-2所描述的修改。

227.如上所述,本公开的实施例提供了一种封装结构。封装结构包括基板160,其包括直接位于开放角落120c1和120c4下方的沟槽170,且沟槽170填充有底部填充材料180。结果,可以减小或减轻集中在半导体晶粒120的角落处的拉伸应力。因此,可以降低底部填充材料138破裂的风险,从而提高封装结构的性能和可靠性。

228.可以提供封装结构的实施例。封装结构可以包括在基板上方的重分布结构以及在重分布结构上方并电耦接到基板的半导体晶粒。封装结构也可以包括在基板上方的底部填充材料,且底部填充材料包括延伸部分。延伸部分与半导体晶粒的角落重叠并延伸到基板中。结果,可以减小或减轻集中在半导体晶粒的角落处的拉伸应力。因此,可以降低底部填

充材料破裂的风险,从而提高封装结构的性能和可靠性。

229.根据本公开一些实施例,提供一种封装结构。所述封装结构包括:重分布结构,位于基板上方;半导体晶粒,位于重分布结构上方并电耦接到基板;以及底部填充材料,位于基板上方并密封重分布结构和半导体晶粒,其中底部填充材料包括与半导体晶粒的角落重叠并延伸到基板中的延伸部分。

230.在一些实施例中,在平面图中,延伸部分包括位于重分布结构的区域之外的部分。在一些实施例中,基板包括绝缘层以及位于绝缘层中的多个导电特征,其中延伸部分通过绝缘层与导电特征隔离。在一些实施例中,在平面图中,延伸部分包括位于半导体晶粒的区域内的第一侧壁以及该第一侧壁相对并位于半导体晶粒的区域之外的第二侧壁,且延伸部分的第一侧壁与半导体晶粒的角落之间的最小距离大于或等于延伸部分的第二侧壁与半导体晶粒的角落之间的最小距离。在一些实施例中,在平面图中,从重分布结构的几何中心到半导体晶粒的角落的方向被定义为第一方向,且第一方向与延伸部分的纵向的夹角小于约15度。在一些实施例中,延伸部分的侧壁包括弧形表面。在一些实施例中,所述封装结构还包括多个接合元件,介于基板与重分布结构之间并被底部填充材料围绕,其中接合元件中没有一个直接位于延伸部分上方。

231.根据本公开另一些实施例,提供一种封装结构。所述封装结构包括:多个接合元件,位于基板上方;重分布结构,位于所述接合元件上方;半导体晶粒,位于重分布结构上方;以及底部填充材料,包括:第一部分,围绕所述接合元件;以及第二部分,嵌入基板中,其中在平面图中,半导体晶粒的角落局限在第二部分的区域内。

232.在一些实施例中,在平面图中,第二部分完全局限在重分布结构的区域内。在一些实施例中,在平面图中,第二部分具有椭圆形轮廓。在一些实施例中,第二部分的底表面高于基板的底表面。在一些实施例中,在平面图中,从重分布结构的几何中心延伸到半导体晶粒的角落的第一方向基本上平行于第二部分的对称轴。在一些实施例中,在平面图中,第二部分沿第一方向的长度大于第二部分沿垂直于第一方向的第二方向的宽度。在一些实施例中,在平面图中,第二部分包括位于半导体晶粒的区域内的第一侧壁以及与第一侧壁相对并位于半导体晶粒的区域之外的第二侧壁,且沿第一方向测量时,第一侧壁与半导体晶粒的角落之间的第一距离大于或等于第二侧壁与半导体晶粒的角落之间的第二距离。在一些实施例中,沿第一方向测量时,重分布结构的角落与第二侧壁之间的第三距离小于第二距离。在一些实施例中,所述封装结构还包括封装,位于重分布结构上方,且底部填充材料还包括第三部分,嵌入基板中,其中在平面图中,封装的角落局限在第三部分的区域内。

233.根据本公开又另一些实施例,提供一种形成封装结构的方法。所述方法包括:将半导体晶粒接合到重分布结构的第一表面;将重分布结构的第二表面接合到基板,其中基板包括与半导体晶粒的角落重叠的第一沟槽;以及用底部填充材料密封半导体晶粒和重分布结构,其中基板的第一沟槽填充有底部填充材料。

234.在一些实施例中,重分布结构通过多个接合元件接合到基板,且底部填充材料围绕接合元件。在一些实施例中,在平面图中,第一沟槽的对称轴穿过半导体晶粒的角落。在一些实施例中,所述方法还包括将封装接合到重分布结构的第一表面,其中基板包括与封装的角落重叠的第二沟槽,且基板的第二沟槽填充有底部填充材料。

235.前述内文概述了许多实施例的特征,使本技术领域中技术人员可以从各个方面更

佳地了解本公开。本技术领域中技术人员应可理解,且可轻易地以本公开为基础来设计或修饰其他工艺及结构,并以此达到相同的目的及/或达到与在此介绍的实施例等相同的优点。本技术领域中技术人员也应了解这些相等的结构并未背离本公开的发明构思与范围。在不背离本公开的发明构思与范围的前提下,可对本公开进行各种改变、置换或修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1