一种双像元同时输出高响应率线阵CMOS图像传感器和方法与流程

一种双像元同时输出高响应率线阵cmos图像传感器和方法

技术领域

1.本发明属于图像传感器技术领域,具体属于一种双像元同时输出高响应率线阵cmos图像传感器和方法。

背景技术:

2.图像传感器是现代电子成像系统的核心,图像传感器主要基于两种工艺实现,cmos工艺和电荷耦合器件(ccd)工艺。cmos图像传感器技术由于其集成度高、体积小、功耗低等优点,在最近几年取得了飞速发展。

3.cmos图像传感器目前分为两种阵列模式,一是面阵二维成像,这也是目前应用量最广泛的阵列结构,还有一种是线阵结构。线阵结构又分为单线和多线,这两种像架阵列可共用一套读出电路架构设计,区别在于,面阵cis在使用全局曝光时,由于逐行读出时间较长,系统曝光时间可由几十微秒至几百毫秒级,这就使得面阵cis可满足多种环境应用需求。线阵扫描cis行频较高,一般从几khz到上百khz,所以其曝光时间只能从几微秒至几十微秒级,增加曝光时间会严重降低行频,所以响应率成为了限制线阵扫描cis的最大瓶颈,但其较小的体积和可拓展的分辨率在一些环境中得到了重点应用,为了满足其使用要求,必须提高其响应率,在像元工艺一定的前提下,用户通常通过补光提高入射能量增强响应率,这就限制了其应用环境。

4.传统线阵扫描cis为了实现较高的响应率,都采用多线阵累加方式(tdi),该方式的渡越时间很长,读出电路复杂且更多在ccd中使用。

技术实现要素:

5.为了解决现有技术中存在的问题,本发明提供一种双像元同时输出高响应率线阵cmos图像传感器和方法,可简单有效的提升线阵cis的响应率,同时该技术仍适用于tdi cis,且具有其它线阵cis不具备的双成像功能,对于线阵cis的复杂环境适用性具有很高的提升。

6.为实现上述目的,本发明提供如下技术方案:

7.一种双像元同时输出高响应率线阵cmos图像传感器,包括第一像元阵列、第二像元阵列、可编程增益放大器、列缓冲驱动电路、多级高速控制开关、模拟列逻辑控制电路、单斜式列级并行adc、芯片级pipeline adc、数字列逻辑和多通道高速lvds接口模块;

8.所述第一像元阵列的像元面积大于第二像元阵列的像元面积;

9.所述第一像元阵列和第二像元阵列连接可编程增益放大器,可编程增益放大器连接列缓冲驱动电路的一端,列缓冲驱动电路的另一端连接多级高速控制开关的一端,多级高速控制开关的另一端连接模拟列逻辑控制电路的一端,模拟列逻辑控制电路的另一端分别连接单斜式列级并行adc和芯片级pipeline adc;单斜式列级并行adc连接数字列逻辑;芯片级pipeline adc和数字列逻辑均连接多通道高速lvds接口模块。

10.优选的,当第一像元阵列和第二像元阵列的满阱电荷相同时,第一像元阵列的像

元面积为第二像元阵列的4倍,第一像元阵列的感光面积为第二像元阵列的8倍。

11.优选的,所述第一像元阵列和第二像元阵列为单线阵列或多线阵列。

12.优选的,所述第一像元阵列和第二像元阵列同时曝光并量化输出,反映第一像元阵列和第二像元阵列对同一目标的不同成像属性。

13.优选的,所述第一像元阵列或第二像元阵列单独扫描成像。

14.优选的,还包括斜坡发生器,所述斜坡发生器用于提供比较参考电平。

15.优选的,所述多通道高速lvds接口模块的数据吞吐量为芯片级pipeline adc和数字列逻辑的输出数据量之和。

16.一种双像元同时输出高响应率线阵cmos图像传感器的成像方法,其特征在于,基于上述任意一项所述的一种双像元同时输出高响应率线阵cmos图像传感器,包括以下过程,

17.双像元成像工作时,由控制信号开启第一像元阵列和第二像元阵列的曝光,首先将第二像元阵列输出模拟信号传至可编程增益放大器的输入端,可编程增益放大器进行采样并放大输送给单斜式列级并行adc,斜坡发生器提供比较参考电平,单斜式列级并行adc进入量化阶段;

18.然后将第一像元阵列输出模拟信号传至可编程增益放大器的输入端,可编程增益放大器进行采样并放大输送给列缓冲驱动电路,列缓冲驱动电路输出接多级高速控制开关,模拟列逻辑控制级联开关从s1~s4096逐个导通,将列缓冲输出差分信号输送至pipeline adc进行数字量化,输出码d0~d13传送至多通道高速lvds接口模块,完成输出;待pipeline adc量化完成后,单斜式列级并行adc十进制比较值由计数器编码输出至多通道高速lvds接口模块,完成输出;

19.单像元成像工作时,由控制信号选择开启第一像元阵列或第二像元阵列的曝光,首先将像元输出模拟信号传至可编程增益放大器的输入端,可编程增益放大器进行采样并放大输送给单斜式列级并行adc,斜坡发生器提供比较参考电平,单斜式列级并行adc量化完成后输送给编码器;编码完成后由多通道高速lvds接口模块驱动输出;或,

20.由控制信号选择开启第一像元阵列或第二像元阵列的曝光,然后将像元输出模拟信号传至可编程增益放大器的输入端,可编程增益放大器进行采样并放大输送给列缓冲驱动电路,列缓冲驱动电路输出接多级高速控制开关,模拟列逻辑控制级联开关从s1~s4096逐个导通,将列缓冲输出差分信号输送至pipeline adc进行数字量化,输出码d0~d13传送至多通道高速lvds接口模块,完成输出。

21.与现有技术相比,本发明具有以下有益的技术效果:

22.本发明提供一种双像元同时输出高响应率线阵cmos图像传感器,在保持满阱电荷数一定的前提下,可将响应率以提升8倍左右,同时可以实现不同的满阱数,达到更高的响应率;本发明支持曝光时间内双像元图像同时输出,既可用于高动态亮光环境,也可用于高响应率暗场环境,在同一线扫周期内,对目标图像支持两种像元成像输出对比。本发明采用单一图像传感器实现两种像素同时成像,兼容了高动态与高响应率这一矛盾指标,可使得线阵扫描cmos图像传感器得以更为广泛的应用。

23.本发明通过集成两种像元,可兼顾亮场下的高动态范围和暗场下的高响应率应用需求,在暗场下,像元响应率可提升至常态下的8倍以上(不改变c

fd

的前提下,否则可以更

高),降低了补光设备的需求;此外,线阵扫描具有时域特性,无法对已经变化的动态目标实施二次初始成像,本设计双像元可同时曝光并成像,生成高动态和高响应率两幅图像,具有很高的对比性。通过双像元同时成像高响应率线阵cmos图像传感器架构设计,可极大的扩展高速线阵扫描cis的应用环境。

附图说明

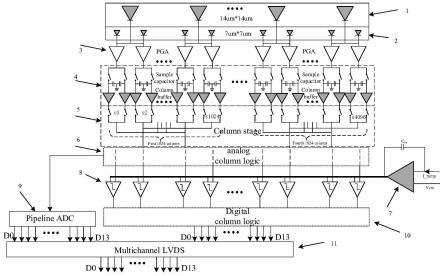

24.图1为双像元同时输出列级工作电路;

25.图2为双像元时序控制示意图;

26.图3为高速列缓冲电路示意图;

27.图4为高速级联控制开关;

28.图5为列级adc工作原理图;

29.图6为芯片级pipeline adc结构示意图;

30.图7为本发明线阵图像传感器结构示意图;

31.图8为本发明双像元同时输出高响应率线阵cmos图像传感器结构示意图;

32.图中:1为第一像元阵列、2为第二像元阵列、3为可编程增益放大器、4为列缓冲驱动电路、5为多级高速控制开关、6为模拟列逻辑控制电路、7为斜坡积分器、8为单斜式列级并行adc、9为芯片级pipeline adc、10为数字列逻辑、11为多通道高速lvds接口模块、12为积分型斜坡发生器、13为比较器、14为第一列缓冲器、15为第二列缓冲器。

具体实施方式

33.下面结合具体的实施例对本发明做进一步的详细说明,所述是对本发明的解释而不是限定。

34.如图1所示为双像元同时输出列级工作电路,图2为时序控制示意图,包括可编程增益放大器,多级流水采样开关阵列,积分型斜坡发生器12,比较器13,计数器,编码器,第一列缓冲器14、第二列缓冲器15和pipeline adc,通用型lvds此处不再表述,图中省略了cmos有源像素pixel1和pixel2,只描述其输出连接关系。两种像元同时工作需要一个列级adc和一个芯片级adc,图1中列级adc使用的积分型斜坡发生器,其中i—sample为积分电流,cint为积分电容,斜坡发生器精度(12位/14位/16位)可调,斜坡发生器使用的时钟为adc模块中计数器的时钟周期(ns),其工作过程如图3所示。图6为芯片级pipeline adc结构示意图,可以在百mhz采样率下工作,在14bit输出时,其量化周期小于列级adc的一半,这就保证了其lvds输出不存在时域上的竞争关系,只需要保证lvds大于两种adc的输出频率。

35.本发明中的列缓冲电路如图4所示,不同于传统的单缓冲结构,为了将pga输出的vr和vs作为芯片级pipeline adc的差分输入,控制缓冲器到adc输入的开关必须同时闭合。为了减小rc时间常数,实现高速输出的目的,本文采用了如图4所示的两级选通开关结构。从图4可以看出,将1024列开关分为16组,每组64个开关,每组开关共用一个二级选通开关,共16个二级选通开关。在依次读出某一组数据时,该组的一级开关依次导通,二级开关导通,其他各组的二级开关关断。因此,第一级开关输出端的等效电容为64个开关管漏极电容之和,第二级开关输出端的等效电容为16个开关管漏极电容之和,因此大大减小了开关管引入的寄生电容,有效减小了rc时间常数,提高了列缓冲电路的速度。

36.在进行双像素同时成像拍摄时,在相同曝光时长曝光结束后,第二像元阵列2首先输出复位信号,而后再输出曝光信号,二者经可编程增益放大器相关双采样和放大后,分别被采样并存储于电容cr1和cs1上,列级adc对采样信号进行量化,详细过程如图2中时序控制所示:首先en1和ss闭合,sd断开,pga模块使能开启,s1、s2、s3闭合,cr1采样缓冲器输出vcm(此时pga工作在缓冲器状态);采样完成后断开s2、s3和s1,闭合s4,列级adc开始对第一次复位电压做量化,待列线信号稳定后,s1、s5闭合,电容cs1采样光电信号,采样完成后s5断开,s6闭合,列级adc开始对光电信号量化,量化过程较长,为保证低功耗应用,en2可选择断开;在列级adc量化同时,en2闭合,ss断开,s0、s2、s7闭合,cr2采样缓冲器输出vcm(此时pga工作在缓冲器状态),采样完成后断开s7,闭合s8、sd,将信号送入列缓冲器;待列线信号稳定后,s2、s9闭合,电容cs2采样光电信号,采样完成后s9断开,s10、sd闭合,cs2采样光电信号由列缓冲器驱动输出,此时,所有4096列均已完成信号采样,由高速差分采样开关s11和s11'(差分对开关)送至芯片级pipeline adc输入端进行量化,量化完成后由lvds驱动输出,同时开启下一行的曝光并重复以上操作。此处列缓冲配合pipeline adc可以有多种工作实现方式,比如不做pga输出vs和vr的差分信号量化,只对vs进行量化,或者在列缓冲后面添加全局缓冲器等,不管设计如何改变,可同时双像元成像功能均属于本发明的约束范围。

37.在进行单像素成像拍摄时,可选择使能列级adc(积分型)或者芯片级adc,这里不再对此进行描述,单像素成像读出架构不属于本发明约束范围,但片上双adc架构属于本发明的约束范围。

38.本发明所描述的一种双像元同时成像高响应率线阵cmos图像传感器架构设计,通常用于线阵扫描/基于时间延迟积分(tdi)的cmos图像传感器。

39.如图8所示,本发明的一种双像元同时成像高响应率线阵cmos图像传感器架构设计,包括两种不同尺寸的第一像元阵列1、第二像元阵列2,带相关双采样设计的可编程增益放大器3,列缓冲驱动电路4,多级高速控制开关5,模拟列逻辑控制电路6,斜坡积分器7,单斜式列级并行adc 8,芯片级pipeline adc 9,数字列逻辑10和多通道高速lvds接口模块11组成。

40.本发明与传统线阵cmos图像传感器最大的差异包括两种不同尺寸的第一像元阵列1、第二像元阵列2、片上两种adc量化单斜式列级并行adc8和芯片级pipeline adc9。当第一像元阵列1和第二像元阵列2的c

fd

(满阱电荷)相同时,第一像元阵列1的像元面积为第二像元阵列2的4倍,第一像元阵列1的感光面积可以达到第二像元阵列2的8倍左右,在相同的曝光条件下,第一像元阵列1像元具有更高的响应率。模拟信号数字量化使用单斜式列级并行adc8和侧面芯片级pipeline adc9,第一像元阵列1和第二像元阵列2读出间隔时间很短,第一像元阵列1的数据量只有第二像元阵列2的一半,第一像元阵列1输出的模拟信号由芯片级pipeline adc9进行高速量化并在单斜式列级并行adc8量化完成之前输出,第二像元阵列2输出的模拟信号由单斜式列级并行adc8进行量化,待量化完成后再进行第二像元阵列2下一次曝光信号的量化,流水线工作。lvds驱动器11的数据吞吐量为芯片级pipeline adc 9和数字列逻辑10输出数据量之和。

41.第一像元阵列1和第二像元阵列2可以为任意尺寸比例,既可以包含单线阵列也可以包含多线阵列(tdi cis),图中尺寸和线阵规模只是一种示例;片上同时存在两种adc,这

两种adc一种是单斜式积分型,另外一种可以是pipeline adc或者sar adc等。

42.线阵扫描cis目前市场的主流像素尺寸为7μm*7μm,垂直分辨率可达到4k,较大的像素面积是为了尽可能提升光响应率,4k的垂直分辨率主要受限于制造工艺(掩膜板)。对于单线阵扫描cis而言,滚筒曝光具有更好的信噪比,且不影响行频。本发明中第一像元阵列1和第二像元阵列2可选多种尺寸,其比例可选择1:1、1:4、1:9等,对应的输出也会等比变化,片上两种adc也是为了双像素同时成像,且占用芯片面积最小。

43.第一像元阵列1和第二像元阵列2既可以同时曝光并量化输出,反映两种像元对同一目标的不同成像属性,也可以只选择第一像元阵列1或者第二像元阵列2单独扫描成像,特别是在第一像元阵列1单独扫描成像时因为数据量减半和高速芯片级pipeline adc 9,可以极大提升行频。

44.单斜式列级并行adc8需要分别对像元输出的复位信号和光电信号进行两次量化,待量化结束后再输出量化值,量化周期较长;芯片级pipeline adc 9为像元输出的复位信号和光电信号作为差分输入,可在一个时钟周期内完成1列模拟信号量化并输出,需保证在其量化结束前8还未完成最终量化,否则会影响行频速度。

45.缓冲器4、高速级联开关5、模拟列逻辑控制6均是为芯片级adc 9提供工作环境的,单斜式列级并行adc8可直接选择可编程增益放大器3、列缓冲4、高速级联开关5并对模拟信号进行量化。

46.典型双像元同时成像工作过程:由控制信号开启第一像元阵列1和第二像元阵列2的曝光,首先将第二像元阵列2输出模拟信号传至pga输入端,pga进行采样并放大输送给单斜式列级并行adc8,斜坡发生器7提供比较参考电平,单斜式列级并行adc8进入量化阶段;然后将第一像元阵列1输出模拟信号传至pga输入端,pga进行采样并放大输送给列缓冲器4,缓冲器输出接高速级联开关,模拟列逻辑控制级联开关从s1~s4096逐个导通,将列缓冲输出差分信号输送至芯片级pipeline adc 9进行数字量化,输出码d0~d13传送至多路高速lvds接口11,完成输出;待芯片级pipeline adc 9量化完成后,单斜式列级并行adc8十进制比较值由计数器编码输出至多路高速lvds接口11,完成输出。在pipeline adc和单斜式adc量化过程同时,像元开始下一曝光控制,重复以上操作,形成高速流水曝光输出,由于第一像元阵列1的光电二极管面积远大于第二像元阵列2,相同入射光下,第一像元阵列1图像亮度更高,这对于暗场应用至关重要。

47.单像元成像工作过程1:由控制信号选择开启第一像元阵列1或第二像元阵列2的曝光,首先将像元输出模拟信号传至pga输入端,pga进行采样并放大输送给单斜式列级并行adc8,斜坡发生器7提供比较参考电平,单斜式列级并行adc8量化完成后输送给编码器。编码完成后由多路lvds驱动输出,这种工作状态下的行频与上面提到的双像元同时成像一致;

48.单像元成像工作过程2:由控制信号选择开启第一像元阵列1或第二像元阵列2的曝光,然后将像元输出模拟信号传至pga输入端,pga进行采样并放大输送给列缓冲器4,缓冲器输出接高速级联开关,模拟列逻辑控制级联开关从s1~s4096逐个导通,将列缓冲输出差分信号输送至芯片级pipeline adc 9进行数字量化,输出码d0~d13传送至多路高速lvds接口11,完成输出,这种工作状态下的行频可以达到工作过程1的2倍以上,且具有更高的列一致性。

49.以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施方式仅限于此,对于本发明所属技术领域的技术人员来说,在不脱离本发明思路的前提下,还可以设计若干简单的替换,都应当视为属于本发明所提交的权利要求书确定的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1