形成氮化硅的方法、相关半导体结构及硅前体与流程

w

sinx

yazrw

,其中n为1到10,y为1或大于1,z为0或大于0,w为0或大于0,x为碘或溴,且a为除x之外的卤素,且r为有机配位体。另外,氢被并入到sin中,氢会降低sin的期望性质。此外,在peald工艺的等离子体部分期间所产生的经激发物质对于ic上的所暴露材料并非具选择性,且因此,在经激发物质与所暴露材料之间会发生不期望反应。

9.还研究了使用基于胺的前体(例如,双(二乙基氨基)硅烷(bdeas)及双(叔丁基氨基)硅烷(btbas))作为ald前体来形成sin。然而,使用这些基于胺的前体的反应具有高活化能,且因此,sin的ald无法在低温下进行。

10.还曾使用sii4作为前体来通过ald形成sin。虽然形成sin,但所得的sin并不具有足以在具有复杂形貌的ic中使用的质量。

11.随着ic的大小持续减小且形貌变得越来越具挑战性,sin的形成变得越来越复杂。由于用于形成sin的要求变得越来越严格,因此上文所提及的技术已无法以所要程度的保形性及在低温下形成sin。

技术实现要素:

12.在一个方面中,本发明涉及一种形成氮化硅的方法。所述方法包括:在低于或等于约275℃的温度下通过原子层沉积在衬底上形成氮化硅;及将所述已形成的氮化硅暴露于等离子体。

13.在另一方面中,本发明涉及一种半导体结构。所述半导体结构包括:衬底上的至少一个特征,所述至少一个特征具有大于约10:1的纵横比;及所述至少一个特征上的氮化硅,所述氮化硅展现大于约85%的阶梯覆盖率。

14.在又一方面中,本发明涉及一种硅前体,所述硅前体包括硅烯化合物,所述硅烯化合物包括n,n

’‑

二-叔丁基-1,3-二氮杂-2-硅杂环戊-4-烯-2-亚基。

附图说明

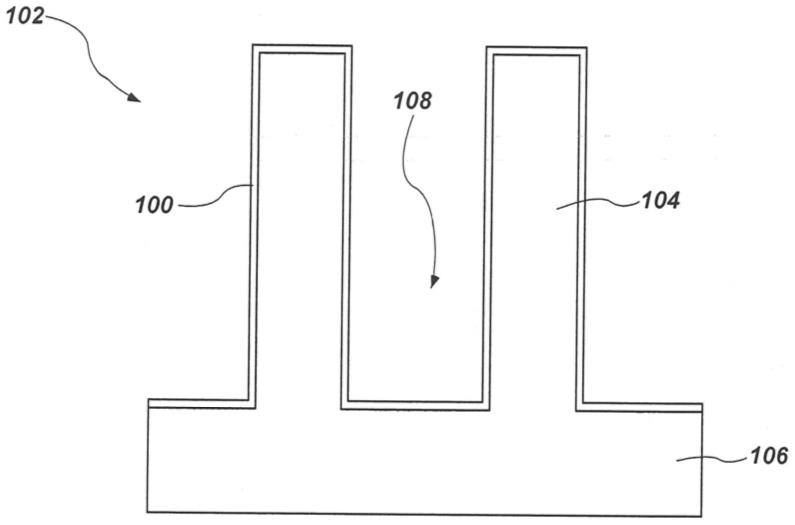

15.图1是根据本发明的实施例而形成的包含氮化硅材料的半导体结构的简化横截面图;

16.图2是根据本发明的实施例在12:1高纵横比结构上形成的氮化硅的隧穿电子显微图(tem);

17.图3是在暴露于蒸汽之后随时间发生的sin的损失百分比的曲线图;且

18.图4是在暴露于h2等离子体之后随时间发生的sin的损失百分比的曲线图。

具体实施方式

19.本发明揭示在低温下在衬底上形成高质量氮化硅(sin)的方法、包含sin的半导体结构及形成半导体结构的方法。sin在低于或等于约275℃的温度下通过原子层沉积(ald)而形成。sin的ald形成在本文中称为sin形成行为。在sin形成行为期间未使用等离子体。在形成之后,sin被暴露于等离子体处理,此在本文中称为等离子体处理行为。与通过常规pvd、常规cvd或常规ald工艺制备的sin相比,通过本发明的实施例而形成的sin展现增大的对下伏材料的粘合性、增大的阶梯覆盖率、增大的湿法蚀刻速率阻力、增大的对蒸汽的阻力及增大的对氢(h2)等离子体的阻力。所得sin还展现均匀组成及高度保形性,且经形成处于

被控制在几埃内的厚度。

20.如本文中所使用,术语“氮化硅”意指且包含包括硅原子及氮原子的化合物。氮化硅可包含化学计量量的硅及氮(例如si3n4),或可包含非化学计量量的硅及氮(例如si

x

ny),其中x及y中的每一个独立地为从约0.5到约2.0的有理数。氮化硅还可包含si(ch)

x

ny,其中x及y中的每一个独立地为从约0.5到约2.0的有理数。sin中可存在少量的氢(例如从约4原子%到约12原子%)。sin中可存在少量的碘或溴,例如低于约1原子%。

21.如本文中所使用,术语“衬底”意指且包含在其上形成额外材料的基底材料或构造。衬底可为半导体衬底、支撑结构上的基底半导体层、金属电极或其上形成有一或多个(种)材料、层、结构或区域的半导体衬底。半导体结构上的材料可包含但不限于半导电材料、绝缘材料、导电材料等。所述材料中的一或多个可为热敏性的。衬底可为常规硅衬底或包括半导电材料层的其它块状衬底。如本文中所使用,术语“块状衬底”不仅意指且包含硅晶片,而且意指且包含绝缘体上覆硅(“soi”)衬底(例如,蓝宝石上覆硅(“sos”)衬底及玻璃上覆硅(“sog”)衬底)、在基底半导体底座上之外延硅层及其它半导体或光电材料(例如,硅锗、锗、砷化镓、氮化镓及磷化铟)。衬底可为经掺杂的或未经掺杂的。

22.如本文中所使用,术语“纵横比”意指且包含特征的高度与特征的宽度的比率。

23.通过本发明的实施例而形成的sin可具有高度保形性,例如大于约80%的阶梯覆盖率、大于约85%的阶梯覆盖率、大于约90%的阶梯覆盖率或大于约95%的阶梯覆盖率。高度保形性使得能够在高密度高纵横比(har)半导体结构上形成sin。由于sin在低温下且在不使用等离子体的情况下形成,因此通过本发明的实施例做出的sin的形成与衬底上在sin的形成期间可能暴露的敏感性材料兼容。

24.以下说明提供具体细节(例如,材料类型、材料厚度及处理条件),以便提供对本文中所描述的实施例的透彻说明。然而,所属领域的技术人员将理解,可在不采用这些具体细节的情况下实践本发明的实施例。实际上,本发明之实施例可结合半导体工业中所采用的常规制作技术来实践。另外,本文中所提供的说明不形成对半导体结构或用于制造半导体结构的完整工艺流程的完整说明,且下文所描述的结构不形成完整半导体结构。下文仅详细地描述理解本文中所描述的实施例所必需的那些过程行为及结构。用以形成包含本文中所描述的结构的完整半导体结构的额外行为可通过常规技术而执行。

25.通过两个或多于两个sin形成行为以及两个或多于两个等离子体处理行为,通过ald在衬底上形成sin。sin的一部分最初在低于或等于约275℃的温度下通过ald形成于衬底上。初始sin部分在形成sin的另一部分或另外若干部分之前会经受等离子体处理。sin的另一部分或其它部分在低于或等于约275℃的温度下通过ald形成于所述sin部分上,接着为对每一部分进行等离子体处理。可重复sin形成及等离子体处理行为,直到实现sin的所要厚度为止。sin形成行为中的每一个均在无等离子体环境中进行。即,在sin部分的形成期间在反应器中不产生等离子体。反应器可为常规反应室或常规沉积室,例如常规ald反应器,此处不再进行详细描述。然而,在sin形成行为之后的等离子体处理行为期间使用等离子体。另一选择为,可形成sin的两个或多于两个部分且接着使所有sin部分经受单个等离子体处理。

26.在形成sin之前,衬底任选地可暴露于氨(nh3)气体以制备衬底表面。nh3可被引入到含有衬底的反应器中,且衬底被暴露于nh3达足以使衬底与nh3发生反应的时间量。衬底与

nh3之间的接触时间可介于从约10秒到约180秒的范围内。衬底可在从约150℃到约250℃的温度下且在从约1托到约10托的压力下暴露于nh3。在不受限于任何理论的情况下,认为,nh3会与用于sin形成的衬底发生反应并制备所述衬底的表面。仅以实例方式,nh3可在于衬底上形成sin部分之前为衬底表面提供所要表面终止。

27.为通过ald形成sin部分,可使用硅前体及氮前体来分别在衬底的表面上形成硅单层及氮单层。硅前体用作sin的硅源,且氮前体用作sin的氮源。硅前体及氮前体的反应性可足以使得不需要等离子体来形成硅单层及氮单层。因此,sin的硅单层及氮单层可在反应器中存在硅前体及氮前体时在不产生等离子体的情况下形成。硅前体及氮前体可被依序引入到含有衬底以及与衬底表面接触的硅前体及氮前体的反应器中以形成硅单层及氮单层。硅前体可经调配以展现充分稳定性,使得硅前体在处理温度下不发生分解或不参与次级反应,同时所述硅前体的反应性还足以与衬底的表面发生反应(例如,化学吸附到衬底的表面)。硅前体在加热时可为稳定的且在不发生分解的情况下产生足以提供饱和剂量的硅前体的蒸汽压力。硅前体及氮前体中的每一者可经调配以形成于衬底的表面上的若干位点上(例如,化学吸附到所述位点)或者以自限制方式形成于下伏硅或氮单层上,从而分别产生硅单层及氮单层。可重复依序形成硅单层及氮单层,直到实现sin的所要厚度为止。

28.虽然sin形成行为在本文中描述为先将硅前体引入到反应器中且接着引入氮前体,但引入硅前体及氮前体的次序可被颠倒,使得氮前体被引入到反应器中、与衬底的表面接触,且过量的未反应氮前体被从反应器排出以在衬底上形成氮单层。接着,硅前体可被引入到反应器中、与氮单层接触,且过量的未反应硅前体被从反应器排出以在氮单层上形成硅单层。

29.sin形成行为可在低于或等于约275℃(例如,低于或等于约250℃)的温度下进行。所述温度可介于从约90℃到约275℃的范围内,例如从约100℃到约275℃、从约200℃到约275℃或从约200℃到约250℃。反应器内及衬底的温度在sin形成行为期间可低于或等于约275℃。相对于形成sin的常规高温热cvd、pecvd或pvd工艺的热预算,在其下形成sin的低温可减小热预算。尽管衬底上存在敏感性材料,但低温还可使得能够保形地形成sin。不加限制地,敏感性材料可包含但不限于硫属化物材料、有机(例如,碳)材料、碳的同素异形体(例如,石墨)、反应性金属(例如,钨、铝或钽)或其它敏感性材料。因此,sin可邻近于此些敏感性材料而形成而不发生降级、分解或以其它方式不利地影响材料。

30.为形成初始sin部分的硅单层,硅前体可作为固体或液体被引入到反应器中、经加热变为反应物蒸汽且与衬底表面或与氮单层接触。硅单层或少量硅可形成于衬底上或形成于氮单层上。反应器可维持处于从约1托到约40托的压力,例如在sin形成行为期间处于约20托。硅前体可以从约1标准立方厘米(sccm)到约2000sccm(例如,从约1sccm到约1000sccm)的流动速率被引入到反应器中。硅前体可借助载体气体被引入到反应器中,所述载体气体例如氦、氮、氩、氙、一氧化碳或其组合。载体气体可以从约1sccm到约500sccm的流动速率(例如,以约300sccm的流动速率)被引入到反应器中。硅前体可保持处于反应器中达足以使硅接触且化学吸附到衬底表面或氮单层并形成硅单层的时间量。仅以实例方式,硅前体可保持处于反应器中达从约0.01秒到约100秒,例如从约10秒到约25秒。在一个实施例中,硅前体保持处于反应器中达约10秒。硅前体任选地可保持处于反应器中达更长时间量以确保基本上完成成核作用。

31.硅前体可包含硅原子以及氢原子、碳原子、氮原子或其组合中的一或多个。硅前体可为溴化硅烷或碘化硅烷或者硅烯化合物。溴化硅烷或碘化硅烷可包含但不限于四碘化硅(sii4)、四溴化硅(sibr4)或其组合。在一些实施例中,硅前体为sii4。在其它实施例中,硅前体为sibr4。硅烯化合物可为具有二价硅原子且总体不具有电荷的含硅化合物。硅烯化合物可为饱和的或不饱和的(即,包含碳-碳双键)。在又其它实施例中,硅烯前体为n,n

’‑

二-叔丁基-1,3-二氮杂-2-硅杂环戊-4-烯-2-亚基,其具有以下化学结构:

[0032][0033]

虽然个别前体称为四碘硅烷、四溴硅烷或硅烯化合物,但为简单方便起见,前体在本文中统称为“硅前体”。硅前体可为商业上可从众多来源获得的,所述来源例如阿法埃莎公司(alfa aesar)(马萨诸塞州沃德希尔市)、盖勒斯特公司(gelest,inc.)(宾夕法尼亚州莫里斯维尔市)、西格玛奥德里奇有限责任公司(sigma-aldrich co.llc)(密苏里州圣路易斯市)或施特雷姆化学公司(strem chemicals,inc.)(马萨诸塞州纽伯里波特市)。

[0034]

接着,可从反应器移除(例如,排出)过量的未反应硅前体。可通过将惰性气体(例如,氦、氩、氙或其组合)引入到反应器中而移除未反应硅前体。惰性气体可以从约1sccm到约100sccm的流动速率(例如,以约25sccm)流动到反应器中。可在从约1托到约10托的压力下(例如,在约2托下)对反应器进行排出操作达从约5秒到约30秒。在一些实施例中,硅前体被从反应器排出达约30秒。

[0035]

为形成初始sin部分的氮单层,氮前体可作为固体或液体被引入到反应器中、经加热变为反应物蒸汽且与硅单层接触。氮单层或少量氮可形成于硅单层上。反应器可维持处于从约1托到约40托的压力,例如处于约20托。氮前体可以从约1sccm到约2000sccm(例如,从约1sccm到约1000sccm)的流动速率被引入到反应器中。氮前体可借助载体气体被引入到反应器中,所述载体气体以从约1sccm到约2000sccm的流动速率(例如,以约1000sccm的流动速率)流动。氮前体可保持处于反应器中达足以使氮形成氮单层的时间量。仅以实例方式,氮前体可保持处于反应器中达从约10秒到约25秒。在一些实施例中,氮前体保持处于反应器中达约5秒。

[0036]

氮前体可为nh3、肼(n2h4)、叔丁基肼、单烷基肼、二烷基肼或其组合。在一些实施例中,氮前体为nh3。

[0037]

接着,可通过将惰性气体(例如氦、氩、氙或其组合)引入到反应器中而从反应器移除(例如,排出)过量的未反应氮前体。惰性气体可以从约1sccm到约100sccm的流动速率(例如,以约25sccm)流动到反应器中。可在从约1托到约10托的压力下(例如,在约2托下)对反应器进行排出操作达从约5秒到约30秒。在一些实施例中,过量的氮前体被从反应器排出达约30秒。

[0038]

上文所描述的压力、流动速率及时间可取决于以下各项中的一或多个而增大或减小:反应器的体积、引入硅前体及氮前体的效率、泵浦效率、间歇式炉构造、下伏在sin下的衬底的材料及此项技术内已知的其它因素。

[0039]

硅单层及氮单层可如上文所描述依序形成,直到实现sin的初始部分的所要厚度

为止。sin的初始部分可经形成处于最小厚度,例如处于sin的总厚度的至少约50%的厚度。初始sin部分的厚度可足以基本上完全覆盖下伏在sin下的材料,此防止或减少在后续处理期间对下伏材料的损坏。初始sin部分的厚度可占sin的总厚度的约80%到约90%。在一些实施例中,sin的初始部分经形成为约的厚度。

[0040]

在不受限于任何理论的情况下,和氯硅烷(例如四氯硅烷(sicl4))与nh3的反应相比,上文所提及硅前体中的一个与氮前体(例如nh3)的反应展现高放热性及较低能量势垒。由于所述反应具有较低能量势垒,因此上述硅前体适合用作低温(即,低于或等于约275℃)ald前体。

[0041]

在形成之后,sin的初始部分可被暴露于等离子体处理。等离子体可产生于反应器中(例如,直接等离子体),或等离子体可产生于反应器外且被供应到反应器(例如,远程等离子体)。等离子体可具有惰性物质(例如氦、氩、氙或其组合)、反应性物质(例如氮(n2)、氢(h2)或其组合)或者惰性物质与反应性物质的组合。等离子体可通过常规技术而产生,本文中不再详细描述所述常规技术。等离子体产生与sin的初始部分发生反应且使sin的初始部分改性的自由基及其它物质。等离子体物质可基于下伏在sin下的材料而选择。在一些实施例中,等离子体包含n2及氦。等离子体可为电感耦合等离子体(icp)、电容耦合等离子体(ccp)或其组合。等离子体可以从约400khz到约30mhz的频率操作。在一些实施例中,频率为约13.56mhz。等离子体具有从约150w到约600w的功率。频率及功率可取决于反应器设计及等离子体操作模式以及下伏在sin下的衬底的材料而选择。上文所描述的压力、流动速率及时间可取决于以下各项中的一或多个而增大或减小:反应器的体积、引入硅前体及氮前体的效率、泵浦效率、间歇式炉构造及此项技术内已知的其它因素。

[0042]

在对sin的初始部分进行等离子体处理之后,可在低于或等于约275℃的温度下通过ald在所述初始sin部分上形成sin的另一部分或其它部分,接着对所述另一部分或其它部分进行等离子体处理。sin的另一部分或其它部分可如上文针对初始sin部分所描述而形成,只不过所述另一部分或其它部分的厚度可能小于初始sin部分的厚度。对sin的每一部分的等离子体处理可如上文所描述而进行。所形成的额外sin部分的数目及所进行的等离子体处理的次数可取决于sin的预期使用而选择,如下文更详细描述。可重复sin形成行为及等离子体处理行为,直到实现sin的所要总厚度为止。

[0043]

初始sin部分及后续形成的sin部分可经受等离子体处理以使sin改性。在不受限于任何理论的情况下,认为,将已形成的sin部分暴露于等离子体处理会增大sin的密度,此提供改善的粘合性、增大的阶梯覆盖率、增大的湿法蚀刻速率阻力、增大的对蒸汽的阻力及增大的sin对h2等离子体的阻力。等离子体处理还可减少sin中的杂质,例如氢、碘或溴杂质。因此,与通过常规技术而形成的sin相比,通过本发明的实施例而形成的sin的质量更高。

[0044]

等离子体处理提高sin的质量的能力是意料之外的,因为据预期,等离子体会使下伏在sin下的材料降级(例如,分解)且还会使例如反应器等装备降级(例如,腐蚀所述装备)。然而,由于在不存在硅前体及氮前体(即,硅前体及氮前体在sin形成行为之后被从反应器移除)时进行等离子体处理行为,因此不存在使下伏敏感性材料或装备降级、分解或以其它方式不利地影响下伏敏感性材料或装备的反应性卤化物物质。因此,在sin形成期间未观察到卤化物副产物污染。

[0045]

因此,揭示一种形成sin的方法。所述方法包括:在低于或等于约275℃的温度下通过原子层沉积在衬底上形成氮化硅。将已形成的氮化硅暴露于等离子体。

[0046]

因此,揭示形成sin的另一方法。所述方法包括通过原子层沉积在衬底上形成氮化硅的一部分。氮化硅的所述部分通过使硅前体及氮前体与衬底接触而形成,所述硅前体包括溴化硅烷、碘化硅烷、硅烯化合物或其组合,所述氮前体包括氨。氮化硅的所述部分被暴露于等离子体处理。通过原子层沉积在氮化硅的所述部分上形成氮化硅的至少一个其它部分。氮化硅的所述至少一个其它部分通过使硅前体及氮前体与氮化硅的所述部分接触而形成,所述硅前体包括溴化硅烷、碘化硅烷、硅烯化合物或其组合,所述氮前体包括氨。氮化硅的所述至少一个其它部分被暴露于等离子体处理。

[0047]

因此,揭示一种包括硅烯化合物的硅前体。所述硅烯化合物包括n,n

’‑

二-叔丁基-1,3-二氮杂-2-硅杂环戊-4-烯-2-亚基。

[0048]

此处所包含的图解并不意指任何特定半导体结构的实际视图,而是仅为用于描述本文中的实施例的理想化表示。因此,图解可能未按比例绘制。

[0049]

通过本发明的实施例而形成的sin可用于具有拥有高纵横比的至少一个特征的半导体结构中。如图1中所展示,半导体结构102包含sin 100、具有高纵横比的至少一个特征104及其中具有界定特征104的开口108的衬底106。sin 100可保形地形成于特征104上。取决于sin 100的预期应用,衬底106可为半导电材料、绝缘材料或导电材料。仅以实例方式,半导电材料可为硅、氢掺杂的硅、氧化硅、氢掺杂的氧化硅、镓等。绝缘材料可包含但不限于二氧化硅、氧化铪或氧化铝。导电材料可包含但不限于金属、导电掺杂的硅、导电掺杂的锗、金属硅化物、金属碳化物、相变材料等。衬底106的材料可通过常规技术而形成,例如物理气相沉积(pvd)、化学气相沉积(cvd)或ald。此些技术是此项技术内已知的,且因此本文中不再详细描述。如图1中所展示,特征104由衬底106的材料形成。然而,衬底106上可包含构成特征104的一或多个(种)材料、层、结构或区域,例如堆叠结构。堆叠结构的材料可通过常规技术而形成,本文中不再详细描述所述常规技术。特征104可具有高纵横比,例如至少约10:1(例如至少约12:1、至少约13:1或至少约15:1)的纵横比。根据本发明的实施例,sin 100可形成于特征104上。sin可经形成处于从约3nm到约100nm(例如,从约4nm到约20nm或从约4nm到约9nm)的范围内的总厚度。然而,取决于其中将使用sin的半导体装置结构,sin还可经形成处于更大厚度。保形地形成于特征104上的sin 100可展现大于约80%的阶梯覆盖率、大于约85%的阶梯覆盖率、大于约90%的阶梯覆盖率或大于约95%的阶梯覆盖率。另一选择为,sin 100可作为平面层(未展示)形成于半导体结构102上。

[0050]

半导体结构102的sin 100可用于具有至少一个高纵横比特征的半导体装置结构中,例如用于晶体管、存储器、逻辑装置、存储器阵列等中。sin可用于包含但不限于以下各项的半导体装置结构中:动态随机存取存储器(dram)装置、“或非”(nor)快闪存储器装置或三维(3d)交叉点存储器装置。sin 100可作为绝缘材料、掩模材料、蚀刻停止材料、势垒材料或间隔件材料用于半导体装置结构中。用于sin形成行为的工艺条件及ald前体以及用于等离子体处理行为的工艺条件可取决于将要形成的半导体装置结构以及所要粘合性、阶梯覆盖率、湿法蚀刻速率阻力、对蒸汽的阻力及sin 100对h2等离子体性质的阻力而选择。包含sin 100的半导体装置结构可通过修整sin形成行为及等离子体处理行为的条件而形成。仅以实例方式,如果sin 100将用于dram装置中,那么sin 100可在约250℃的温度下形成,而

如果sin 100将用于3d交叉点存储器装置中,那么sin 100可在约200℃的温度下形成。仅以实例方式,在dram装置的制作中将使用的等离子体处理行为可为icp模式等离子体,而在3d交叉点存储器装置的制作中将使用的等离子体处理行为可为ccp模式等离子体。

[0051]

可进行额外工艺行为以形成完整半导体装置结构。额外工艺行为可通过常规技术而形成,本文中不再详细描述所述常规技术。

[0052]

因此,揭示一种形成半导体结构的方法。所述方法包括在低于或等于约275℃的温度下通过原子层沉积在衬底上的至少一个特征上形成氮化硅。所述至少一个特征具有大于约10:1的纵横比。已形成的氮化硅被暴露于等离子体。

[0053]

因此,揭示一种半导体结构。所述半导体结构包括衬底上的至少一个特征及所述至少一个特征上的氮化硅。所述至少一个特征具有大于约10:1的纵横比且所述氮化硅展现大于约85%的阶梯覆盖率。

[0054]

以下实例用于更详细地阐释本发明的实施例。对于本发明的范围来说,不将这些实例解释为穷尽性或排他性。

[0055]

实例

[0056]

实例1

[0057]

sin形成

[0058]

sin形成于衬底上,所述衬底包含具有12:1的纵横比的har堆叠。所述堆叠中的材料中的至少一些材料包含热敏性材料。sin是使用配备有ald漏斗盖室的applied materials框架而沉积到har堆叠上。在开始sin ald沉积之前,衬底被暴露于nh3达30秒。卡盘在ald沉积期间维持处于200℃的温度。sin的初始部分通过进行90次如下循环而形成于har堆叠的侧壁上:将sii4引入到室中达10秒、接着为30秒的排出操作,将nh3引入到室中达5秒、接着为30秒的排出操作。初始sin部分被暴露于包含n2及he等离子体的第一次等离子体处理达60秒,其中等离子体在300w下于icp模式中产生。第二sin部分通过进行30次如下循环而形成:将sii4引入到室中达10秒、接着为30秒的排出操作,将nh3引入到室中达5秒、接着为30秒的排出操作。衬底经受包含n2及he等离子体的第二次等离子体处理达60秒,其中等离子体在300w下于icp模式中产生。第三sin部分通过进行30次如下循环而形成:将sii4引入到室中达10秒、接着为30秒的排出操作,将nh3引入到室中达5秒、接着为30秒的排出操作。衬底经受包含n2及he等离子体的第三次等离子体处理达60秒,其中等离子体在300w下于icp模式中产生。

[0059]

实例2

[0060]

sin形成

[0061]

ald沉积及等离子体处理行为如实例1中所描述而进行,只不过衬底在开始sin的ald沉积之前不被暴露于nh3。

[0062]

实例3

[0063]

粘合性、阶梯覆盖率、湿法蚀刻速率及蒸汽阻力性质

[0064]

图2中展示如实例1中所描述而沉积的sin的隧穿电子显微图(tem)。尽管har堆叠包含至少五种不同材料,但仍观察到sin与har堆叠的材料的良好粘合性。如图2中展示,sin沿har堆叠的侧壁的整个长度粘附到har堆叠的侧壁。

[0065]

如实例1中所描述而沉积的sin的阶梯覆盖率经测量为至少约85%。在许多位置

中,阶梯覆盖率大于约90%。

[0066]

如实例1中所描述而沉积的sin在2000:1的水溶液:hf中具有介于约与约之间的湿法蚀刻速率。以比较方式,通过常规技术而形成的sin展现约之间的湿法蚀刻速率。以比较方式,通过常规技术而形成的sin展现约的湿法蚀刻速率。因此,所述sin与通过常规技术而形成的sin相比具有相当的湿法蚀刻速率阻力。

[0067]

如实例1中所描述而沉积的sin(样本a)与不暴露于等离子体处理的对照样本(样本b及c)相比展现增大的对蒸汽的阻力,如图3中所展示。对照样本的sin是在250℃下沉积。如实例1中所描述而沉积的sin与对照样本的sin在300℃下被暴露于蒸汽退火,且在蒸汽退火之后的不同时间测量sin的损失百分比。图3展示在蒸汽退火之后随时间发生的sin的损失百分比的曲线图。如实例1中所描述而沉积的sin(样本a)与两个对照样本(样本b及c)相比展示较低损失,且因此展现增大的对蒸汽的阻力。

[0068]

实例4

[0069]

h2等离子体阻力

[0070]

sin如实例1中所描述而沉积,只不过等离子体处理包含暴露于ar-he等离子体达20秒(样本c)或达40秒(样本d)。所得的sin(样本c及d)暴露于h2等离子体,且在h2等离子体暴露之后的不同时间测量sin的损失百分比。样本a及b包含如上文针对样本c及d所描述而沉积的sin,但暴露于不同等离子体及/或具有不同暴露时间。图4展示针对sin且针对对照样本(样本e)的在h2等离子体暴露之后随时间发生的sin的损失百分比的曲线图。与通过常规技术而形成的sin的对照样本(样本e)相比,样本c及d的sin展现增大的对h2等离子体的阻力。

[0071]

虽然已结合各图描述特定说明性实施例,但所属领域的技术人员将认识到并了解:本发明所涵盖的实施例不限于本文中明确展示及描述的那些实施例。而是,可在不背离本发明所涵盖的实施例的范围的情况下做出对本文中所描述的实施例的许多添加、删除及修改,例如后文中所主张的那些内容,包含合法等效内容。另外,来自一个所揭示实施例的特征可与另一所揭示实施例的特征组合,同时仍涵盖于本发明的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1