一种异质结电池及其制备方法与流程

本发明属于太阳能电池,具体涉及一种异质结电池及其制备方法。

背景技术:

1、太阳能电池装置被大规模地普及并且在世界上广泛地用作能够通过光伏效应将光能直接转换成电能的电子器件。异质结太阳能电池,又称hjt电池(hetero-junctionwithintrinsic thin-layer)或shj电池,是一种利用晶体硅基板和非晶硅薄膜制成的混合型太阳能电池,具有制备过程简单、工艺温度低、开路电压高、光电转换效率高、温度系数低等诸多优点,是目前应用最广的高效晶硅太阳能技术之一。异质结电池包括单晶硅基底、分别设置在单晶硅基底的相对两端面上的本征非晶硅层、分别设置在两面的本征非晶硅层上的p型非晶硅层和n型非晶硅层、分别设置在p型非晶硅层和n型非晶硅层上的透明导电层(tco层)以及分别设置在两面的透明导电层上的栅电极。tco层由于兼具透明性和导电性两大特性,发展尤为迅速,在太阳能电池的发展过程中,其由于具有禁带宽度大、可见光谱区光透射率高和电阻率低等光电特性,已广泛应用于异质结太阳能电池中。随着异质结电池的广泛使用,其制备方法也引起了人们的广泛关注。

2、cn111081826a公开了一种异质结电池及其制备方法和应用。所述异质结电池包括依次顺序设置的栅电极、透明导电层、n型非晶硅层、本征非晶硅层、单晶硅基底、本征非晶硅层、p型非晶硅层、透明导电层及栅电极。其制备方法包括:在进行所述透明导电层的镀膜工艺之前,对所述异质结电池的半成品所处环境先进行除湿处理,使所述异质结电池的半成品所处环境中水汽含量控制在3.5e-9mbar以下,之后对所述异质结电池的半成品所处环境进行加湿处理,使所述异质结电池的半成品所处环境中的水汽含量控制在4e-9mbar~6e-9mbar范围内。该技术方案中通过在进行透明导电层的镀膜工艺之前进行水汽管控,使得形成的透明导电层的方阻降低,稳定性提升,波动减少;并使得最终形成的异质结电池的转换效率提高,填充因子增加,同时降低了串联电阻值。

3、cn114613882a公开了一种异质结电池的处理方法。所述的异质结电池的处理方法包括:提供异质结电池,所述异质结电池包括单晶半导体层和非晶半导体层;将所述异质结电池置于暗态环境中,在暗态环境中对所述异质结电池进行静置处理,直至所述异质结电池的效率稳定至第一效率;进行所述静置处理之后,对所述异质结电池进行光照处理,使所述异质结电池的效率上升至第二效率,所述第二效率大于所述第一效率。该技术方案中通过异质结电池的处理方法实现了对非晶半导体层内的缺陷以及潜在缺陷的钝化修复,避免了异质结电池因非晶半导体层内的缺陷和潜在缺陷的存在发生效率衰减。

4、由上述内容可知,现有技术中通过不同的制备方法或处理方法,用以提高异质结电池的性能。硅基异质结电池的核心是硅片表面的非晶硅钝化层。非晶硅层对硅片表面进行有效钝化,可极大的降低表面复合速率,同时较大的带隙宽度同晶硅形成pn结后可得到较大的内建电场,使得异质结电池具有更高的开路电压。但是非晶硅本身导电能力较差,同外层tco接触时依靠隧穿效应进行传输载流子,为了降低载流子传输的隧穿电阻,需要非晶硅的掺杂层(p型和n型)都需要有尽可能高的掺杂浓度,而非晶硅的掺杂层的制备工艺属于低温制程,其制备得到的非晶硅层的掺杂度较低。因此,如何提供一种性能优异的异质结电池,已成为目前亟待解决的技术问题。

技术实现思路

1、针对现有技术的不足,本发明的目的在于提供一种异质结电池及其制备方法。本发明中通过对异质结电池的制备方法进行设计,进一步通过使用包括氢气和掺杂气体的组合对掺杂非晶硅层(n型掺杂非晶硅层和/或p型掺杂非晶硅层)进行等离子体处理,进而制备得到性能优异的异质结电池。

2、为达此目的,本发明采用以下技术方案:

3、第一方面,本发明提供一种异质结电池的制备方法,所述制备方法包括:

4、在硅基体的一侧表面制备本征非晶硅层;

5、在本征非晶硅层远离硅基体的一侧制备n型掺杂非晶硅层;

6、在硅基体的另一侧表面制备本征非晶硅层;

7、在本征非晶硅层远离硅基体的一侧制备p型掺杂非晶硅层;

8、在n型掺杂非晶硅层和p型掺杂非晶硅层远离硅基体的一侧分别制备tco层;

9、其中,所述制备n型掺杂非晶硅层后和/或所述制备p型掺杂非晶硅层后还包括后处理的步骤;

10、所述后处理的步骤为进行等离子体处理;

11、所述等离子体处理使用的气体包括氢气和掺杂气体的组合;

12、所述掺杂气体选自包括ph3和h2的混合气体或包括b2h6和h2的混合气体。

13、本发明中通过对异质结电池的制备方法进行设计,进一步通过使用包括氢气和掺杂气体的组合对掺杂非晶硅层(n型掺杂非晶硅层和/或p型掺杂非晶硅层)进行等离子体处理,使得掺杂非晶硅层表面形成部分微晶结构,同时使掺杂非晶硅层中的部分掺杂元素由填隙掺杂变成替位掺杂,可有效提高掺杂非晶硅层的有效掺杂浓度,降低掺杂非晶硅层与tco层之间的隧穿接触电阻,提升异质结电池的填充因子。

14、需要说明的是,本发明中,所述掺杂气体为包括ph3和h2的混合气体,以混合气体的体积百分含量为100%计,ph3的体积百分含量为1%;所述掺杂气体为包括b2h6和h2的混合气体,以混合气体的体积百分含量为100%计,b2h6的体积百分含量为2%。

15、同时需要说明的是,若制备n型掺杂非晶硅层后包括等离子体处理的步骤,则等离子体处理使用的掺杂气体为包括ph3和h2的混合气体;若制备p型掺杂非晶硅层后包括等离子体处理的步骤,则等离子体处理使用的掺杂气体为包括b2h6和h2的混合气体。

16、以下作为本发明的优选技术方案,但不作为对本发明提供的技术方案的限制,通过以下优选的技术方案,可以更好的达到和实现本发明的目的和有益效果。

17、作为本发明的优选技术方案,所述等离子体处理的功率为600~2000w(例如可以是600w、800w、1000w、1200w、1500w、1600w、1700w、1800w或2000w等),优选为700~900w。

18、优选地,所述等离子体处理的时间为5~120s(例如可以是5s、10s、20s、30s、40s、50s、60s、70s、80s、90s、100s、110s或120s等),进一步优选为20~60s。

19、优选地,所述等离子体处理中氢气的流量为2~15slm(例如可以是2slm、3slm、4slm、5slm、6slm、7slm、8slm、9slm、10slm、11slm、12slm、13slm、14slm或15slm等),进一步优选为3~5slm。

20、优选地,所述等离子体处理中掺杂气体的流量为600~1500sccm(例如可以是600sccm、700sccm、800sccm、900sccm、1000sccm、1100sccm、1200sccm、1300sccm、1400sccm或1500sccm等),进一步优选为700~1200sccm。

21、优选地,所述等离子体处理使用的气体中掺杂气体为包括ph3和h2的混合气体,所述掺杂气体的流量优选为700~900sccm(例如可以是700sccm、750sccm、800sccm、850sccm或900sccm等);所述等离子体处理使用的气体中掺杂气体为包括b2h6和h2的混合气体,所述掺杂气体的流量优选为800~1200sccm(例如可以是800sccm、900sccm、1000sccm、1100sccm或1200sccm等)。

22、作为本发明的优选技术方案,所述等离子体处理使用的气体还包括sih4。

23、优选地,所述sih4的流量为0~400sccm(例如可以是1sccm、2sccm、5sccm、10sccm、20sccm、50sccm、100sccm、150sccm、200sccm、250sccm、300sccm、350sccm或400sccm等),且不为0。

24、由于氢气在pecvd(等离子体增强化学的气相沉积法)反应中较难启辉,形成等离子体,因此,本发明通过使用sih4作为等离子体处理气体,辅助氢气形成等离子体,提高等离子体处理效率。

25、作为本发明的优选技术方案,所述本征非晶硅层包括本征非晶硅内层和本征非晶硅外层,所述本征非晶硅内层位于硅基体和本征非晶硅外层之间。

26、优选地,所述本征非晶硅层的制备方法包括如下步骤:

27、(a)通入sih4,在硅基体的一侧进行沉积,得到本征非晶硅内层;

28、(b)通入sih4和h2的混合气体,在本征非晶硅内层远离硅基体的一侧进行沉积,形成本征非晶硅外层,在硅基体的一侧得到本征非晶硅层。

29、优选地,步骤(a)所述沉积的速率为0.4~1.2nm/s,例如可以是0.4nm/s、0.5nm/s、0.6nm/s、0.7nm/s、0.8nm/s、0.9nm/s、1.0nm/s、1.1nm/s或1.2nm/s等。

30、优选地,步骤(b)所述沉积的速率为0.03~0.3nm/s,例如可以是0.03nm/s、0.05nm/s、0.1nm/s、0.15nm/s、0.2nm/s、0.25nm/s或0.3nm/s等。

31、本发明中,通过选用较高的沉积速率制备本征非晶硅内层,可有效抑制非晶硅在硅片表面的外延生长;同时通过选用较低的沉积速率制备本征非晶硅外层,可提升其钝化效果。

32、优选地,步骤(a)所述sih4的流量为500~2000sccm,例如可以是500sccm、600sccm、800sccm、1000sccm、1200sccm、1400sccm、1600sccm、1800sccm或2000sccm等。

33、优选地,步骤(a)所述沉积的射频电源功率为400~1000w,例如可以是400w、500w、600w、700w、800w、900w或1000w等。

34、优选地,步骤(a)所述沉积的压强为0.5~0.7torr,例如可以是0.5torr、0.52torr、0.55torr、0.57torr、0.6torr、0.63torr、0.65torr、0.68torr或0.7torr等。

35、优选地,步骤(b)所述sih4和h2的体积比为(0.05~5):1,例如可以是0.05:1、0.1:1、0.5:1、1:1、1.5:1、2:1、2.5:1、3:1、3.5:1、4:1、4.5:1或5:1等。

36、优选地,步骤(b)所述sih4的流量为100~800sccm,例如可以是100sccm、200sccm、300sccm、400sccm、500sccm、600sccm、700sccm或800sccm等。

37、优选地,步骤(b)所述沉积的射频电源功率为150~400w,例如可以是150w、170w、200w、220w、250w、270w、300w、330w、350w、380w或400w等。

38、优选地,步骤(b)所述沉积的压强为0.4~0.5torr,例如可以是0.4torr、0.42torr、0.44torr、0.46torr、0.48torr或0.5torr等。

39、需要说明的是,本发明中本征非晶硅层可以为双层结构(即本征非晶硅内层和本征非晶硅外层),也可以为多层结构(包括依次叠加设置的本征非晶硅内层、本征非晶硅外层、……、本征非晶硅最外层),若本征非晶硅层为多层结构,则越远离硅基体一侧的本征非晶硅外层的制备过程中,sih4和h2的体积比越小。

40、同时需要说明的是,若本征非晶硅层为多层结构,则本征非晶硅层的制备方法在步骤(b)后还包括步骤(c):

41、(c)重复步骤(b)n次,在本征非晶硅外层远离硅基体的一侧进行沉积,得到本征非晶硅层;

42、其中,n为≥1的整数。

43、作为本发明的优选技术方案,所述制备本征非晶硅层还包括后处理的步骤。

44、优选地,所述后处理的步骤为进行氢气等离子体处理。

45、优选地,所述氢气等离子体处理中氢气的流量为1000~3000sccm,例如可以是1000sccm、1200sccm、1400sccm、1600sccm、1800sccm、2000sccm、2200sccm、2400sccm、2600sccm、2800sccm或3000sccm等。

46、优选地,所述氢气等离子体处理的射频电源功率为1500~3000w,例如可以是1500w、1700w、2000w、2200w、2500w、2700w或3000w等。

47、优选地,所述氢气等离子体处理的时间为20~120s,例如可以是20s、40s、60s、80s、100s或120s等。

48、本发明中,通过对本征非晶硅层进行氢气等离子体处理,可以增加本征非晶硅层的h含量,同时氢气等离子体处理本征非晶硅层会使膜层发生部分刻蚀,一些结构疏松的膜会被优先刻蚀,刻蚀膜层表面会较为致密,在后续沉积掺杂非晶硅层时,对掺杂元素入侵本征非晶硅层有一定阻挡作用。

49、作为本发明的优选技术方案,所述n型掺杂非晶硅层包括第一n型掺杂非晶硅层和第二n型掺杂非晶硅层,所述第一n型掺杂非晶硅层位于硅基体和第二n型掺杂非晶硅层之间。

50、优选地,所述第一n型掺杂非晶硅层和第二n型掺杂非晶硅层的制备原料包括sih4、掺杂气体和h2,所述掺杂气体为ph3和h2的混合气体。

51、优选地,所述第一n型掺杂非晶硅层中,sih4、掺杂气体和h2的体积比为1:1:5。

52、优选地,所述第二n型掺杂非晶硅层中,sih4、掺杂气体和h2的体积比1:5:3。

53、本发明中,通过控制sih4、掺杂气体和h2(混合气体)的体积比在特定的范围内,具体通过控制混合气体中掺杂气体的含量较低,用以制备第一n型掺杂非晶硅层,通过控制混合气体中掺杂气体的含量较高,用以制备第二n型掺杂非晶硅层。低掺杂气体浓度可以减少因为掺杂导致的非晶硅结构畸变,在同本征非晶硅层接触时,没有太明显的结构差异,充当本征非晶硅层和高浓度掺杂非晶硅层(第二n型掺杂非晶硅层)之间的缓冲层,有利于提升太阳能电池的钝化效果,提升开路电压;高掺杂气体浓度可以提高第二n型掺杂非晶硅层中p的掺杂浓度,降低第二n型掺杂非晶硅层和tco之间的隧穿电阻。

54、优选地,所述n型掺杂非晶硅层的制备方法包括如下步骤:

55、(s1)通入sih4、掺杂气体(ph3和h2)和h2的混合气体,在本征非晶硅层远离硅基体的一侧进行沉积,得到第一n型掺杂非晶硅层;

56、(s2)通入sih4、掺杂气体(ph3和h2)和h2的混合气体,在第一n型掺杂非晶硅层远离硅基体一侧进行沉积,得到第二n型掺杂非晶硅层。

57、优选地,步骤(s1)和步骤(s2)所述沉积的速率各自独立地选自0.05~0.3nm/s,例如可以是0.05nm/s、0.05nm/s、0.1nm/s、0.15nm/s、0.2nm/s、0.25nm/s或0.3nm/s等。

58、优选地,步骤(s1)和步骤(s2)所述沉积的射频电源功率各自独立地选自150~700w,例如可以是150w、200w、300w、400w、500w、600w或700w等。

59、优选地,步骤(s1)和步骤(s2)所述沉积的压强各自独立地选自0.4~0.5torr,例如可以是0.4torr、0.42torr、0.44torr、0.46torr、0.48torr或0.5torr等。

60、作为本发明的优选技术方案,所述p型掺杂非晶硅层包括第一p型掺杂非晶硅层和第二p型掺杂非晶硅层,所述第一p型掺杂非晶硅层位于硅基体和第二p型掺杂非晶硅层之间。

61、优选地,所述第一p型掺杂非晶硅层和第二p型掺杂非晶硅层的制备原料包括sih4、掺杂气体和h2,所述掺杂气体为b2h6和h2的混合气体。

62、优选地,所述第一p型掺杂非晶硅层中,sih4、掺杂气体和h2的体积比为3:1:5。

63、优选地,所述第二p型掺杂非晶硅层中,sih4、掺杂气体和h2的体积比为1:5:3。

64、本发明中,通过控制sih4、掺杂气体和h2(混合气体)的体积比在特定的范围内,具体通过控制混合气体中掺杂气体的含量较低,用以制备第一p型掺杂非晶硅层,通过控制混合气体中掺杂气体的含量较高,用以制备第二p型掺杂非晶硅层。低掺杂气体浓度可以减少因为掺杂导致的非晶硅结构畸变,充当本征非晶硅层和高浓度掺杂非晶硅层(第二p型掺杂非晶硅层)之间的缓冲层,有利于提升太阳能电池的钝化效果,提升开路电压;高掺杂气体浓度可以提高第二p型掺杂非晶硅层中b的掺杂浓度,降低第二p型掺杂非晶硅层和tco之间的隧穿电阻。

65、优选地,所述p型掺杂非晶硅层的制备方法包括如下步骤:

66、(a)通入sih4、掺杂气体(b2h6和h2)和h2的混合气体,在步骤(3)得到的本征非晶硅层远离硅基体的一侧进行沉积,得到第一p型掺杂非晶硅层;

67、(b)通入sih4、掺杂气体(b2h6和h2)和h2的混合气体,在第一p型掺杂非晶硅层远离硅基体一侧进行沉积,得到第二p型掺杂非晶硅层。

68、优选地,步骤(a)和步骤(b)所述沉积的速率各自独立地选自0.05~0.3nm/s,例如可以是0.05nm/s、0.05nm/s、0.1nm/s、0.15nm/s、0.2nm/s、0.25nm/s或0.3nm/s等。

69、优选地,步骤(a)和步骤(b)所述沉积的射频电源功率各自独立地选自150~700w,例如可以是150w、200w、300w、400w、500w、600w或700w等。

70、优选地,步骤(a)和步骤(b)所述沉积的压强各自独立地选自0.4~0.5torr,例如可以是0.4torr、0.42torr、0.44torr、0.46torr、0.48torr或0.5torr等。

71、需要说明的是,本发明中,制备本征非晶硅层前还包括预处理的步骤,所述预处理的方法包括将硅基体进行制绒清洗。

72、同时需要说明的是,本发明中,制备tco层后还包括制备电极的步骤,具体为:在tco层远离硅基体的一侧分别制备正面电极和背面电极。

73、本发明中,对tco层和正面电极以及背面电极的制备方法不做任何特殊的限定,本领域常用的制备方法均适用,示例性地包括但不限于:通过沉积制备tco层,经丝网印刷制备正面电极和背面电极。

74、同时需要说明的是,正面电极为靠近n型掺杂非晶硅层一侧的电极,背面电极为靠近p型掺杂非晶硅层一侧的电极。

75、作为本发明的优选技术方案,所述本征非晶硅层的厚度为3~12nm,例如可以是3nm、4nm、5nm、6nm、7nm、8nm、9nm、10nm、11nm或12nm等。

76、优选地,所述本征非晶硅内层的厚度为1~3nm,例如可以是1nm、1.2nm、1.5nm、1.8nm、2nm、2.3nm、2.5nm、2.7nm或3nm等。

77、优选地,所述本征非晶硅外层的厚度为2~9nm,例如可以是2nm、3nm、4nm、5nm、6nm、7nm、8nm或9nm等。

78、优选地,所述本征非晶硅层的厚度大于本征非晶硅层的厚度。

79、作为本发明的优选技术方案,所述n型掺杂非晶硅层的厚度为3~15nm,例如可以是3nm、4nm、5nm、7nm、10nm、12nm或15nm等。

80、优选地,所述第一n型掺杂非晶硅层的厚度为1~3nm,例如可以是1nm、1.2nm、1.5nm、1.8nm、2nm、2.3nm、2.5nm、2.7nm或3nm等。

81、优选地,所述第二n型掺杂非晶硅层的厚度为2~12nm,例如可以是2nm、3nm、4nm、5nm、6nm、7nm、8nm、9nm、10nm、11nm或12nm等。

82、优选地,所述第二n型掺杂非晶硅层厚度大于第一n型掺杂非晶硅层的厚度。

83、优选地,所述p型掺杂非晶硅层的厚度为5~20nm,例如可以是5nm、7nm、10nm、12nm、15nm、18nm或20nm等。

84、优选地,所述第一p型掺杂非晶硅层的厚度为选自1~3nm,例如可以是1nm、1.2nm、1.5nm、1.8nm、2nm、2.3nm、2.5nm、2.7nm或3nm等。

85、优选地,所述第二p型掺杂非晶硅层的厚度为4~17nm,例如可以是4nm、5nm、7nm、10nm、12nm、15nm或17nm等。

86、优选地,所述第二p型掺杂非晶硅层厚度大于第一p型掺杂非晶硅层的厚度。

87、作为本发明的优选技术方案,所述异质结电池的制备方法具体包括如下步骤:

88、(1)将硅基体制绒清洗后,在速率为0.4~1.2nm/s、射频电源功率为400~1000w、压强为0.5~0.7torr的条件下,通入sih4,在硅基体的一侧进行沉积,得到厚度为1~3nm的本征非晶硅内层,其中sih4的流量为500~2000sccm;

89、通入体积比为(0.05~5):1的sih4和h2的混合气体,在速率为0.03~0.3nm/s、射频电源功率为150~400w、压强为0.4~0.5torr的条件下,在本征非晶硅内层远离硅基体的一侧进行沉积,然后在流量为1000~3000sccm、射频电源功率为1500~3000w的条件下,进行氢气等离子体处理20~120s,形成厚度为2~9nm的本征非晶硅外层,得到本征非晶硅层,其中sih4的流量为100~800sccm;

90、(2)通入体积比为1:1:5的sih4、掺杂气体(包括ph3和h2的组合)和h2的混合气体,在速率为0.05~0.3nm/s、射频电源功率为150~700w、压强为0.4~0.5torr的条件下,在本征非晶硅层远离硅基体的一侧进行沉积,得到厚度为1~3nm的第一n型掺杂非晶硅层,其中sih4的流量为100~800sccm;

91、调整sih4、掺杂气体(ph3和h2的组合)和h2的体积比为1:5:3,在第一n型掺杂非晶硅层远离硅基体的一侧进行沉积,形成厚度为2~12nm第二n型掺杂非晶硅层,得到n型掺杂非晶硅层;

92、任选的,在600~2000w下,使用氢气和掺杂气体(包括ph3和h2的组合)以及任选的sih4,对n型掺杂非晶硅层进行等离子体处理5~120s,得到经后处理的n型掺杂非晶硅层,其中氢气的流量为2~15slm,掺杂气体的流量为600~1500sccm,sih4的流量为0~400sccm;

93、(3)在速率为0.4~1.2nm/s、射频电源功率为400~1000w、压强为0.5~0.7torr的条件下,通入sih4,在硅基体的另一侧进行沉积,得到厚度为1~3nm的本征非晶硅内层,其中sih4的流量为500~2000sccm;

94、通入体积比为(0.05~5):1的sih4和h2的混合气体,在速率为0.03~0.3nm/s、射频电源功率为150~400w、压强为0.4~0.5torr的条件下,在本征非晶硅内层远离硅基体的一侧进行沉积,然后在流量为1000~3000sccm、射频电源功率为1500~3000w的条件下,进行氢气等离子体处理20~120s,形成厚度为2~9nm的本征非晶硅外层,得到本征非晶硅层,其中sih4的流量为100~800sccm;

95、(4)通入体积比为3:1:5的sih4、掺杂气体(包括b2h6和h2的组合)和h2的混合气体,在速率为0.05~0.3nm/s、射频电源功率为150~700w、压强为0.4~0.5torr的条件下,在本征非晶硅层远离硅基体的一侧进行沉积,得到厚度为1~3nm的第一p型掺杂非晶硅层,其中sih4的流量为100~800sccm;

96、调整sih4、掺杂气体(b2h6和h2)和h2的体积比为1:5:3,在第一p型掺杂非晶硅层远离硅基体的一侧进行沉积,形成厚度为4~17nm第二p型掺杂非晶硅层,得到p型掺杂非晶硅层;

97、任选的,在600~2000w下,使用氢气和掺杂气体(b2h6和h2)以及任选的sih4,对p型掺杂非晶硅层进行等离子体处理5~120s,得到经后处理的p型掺杂非晶硅层,其中氢气的流量为2~15slm,掺杂气体的流量为600~1500sccm,sih4的流量为0~400sccm;

98、(5)在n型掺杂非晶硅层和p型掺杂非晶硅层远离硅基体的一侧分别沉积,制备tco层;

99、(6)在tco层远离硅基体的一侧分别制备正面电极和背面电极,得到所述异质结电池。

100、需要说明的是,本发明中对于n型掺杂非晶硅层和p型掺杂非晶硅层的制备顺序不做任何特殊限定,可以在硅基体一侧制备本征非晶硅层和n型掺杂非晶硅层,再在硅基体另一侧制备本征非晶硅层和p型掺杂非晶硅层,也可以是在硅基体一侧制备本征非晶硅层和p型掺杂非晶硅层,再在硅基体另一侧制备本征非晶硅层和n型掺杂非晶硅层。

101、第二方面,本发明提供一种如第一方面所述的制备方法制备得到的异质结电池,所述异质结电池包括依次叠加设置的tco层、n型掺杂非晶硅层、本征非晶硅层、硅基体、本征非晶硅层、p型掺杂非晶硅层和tco层。

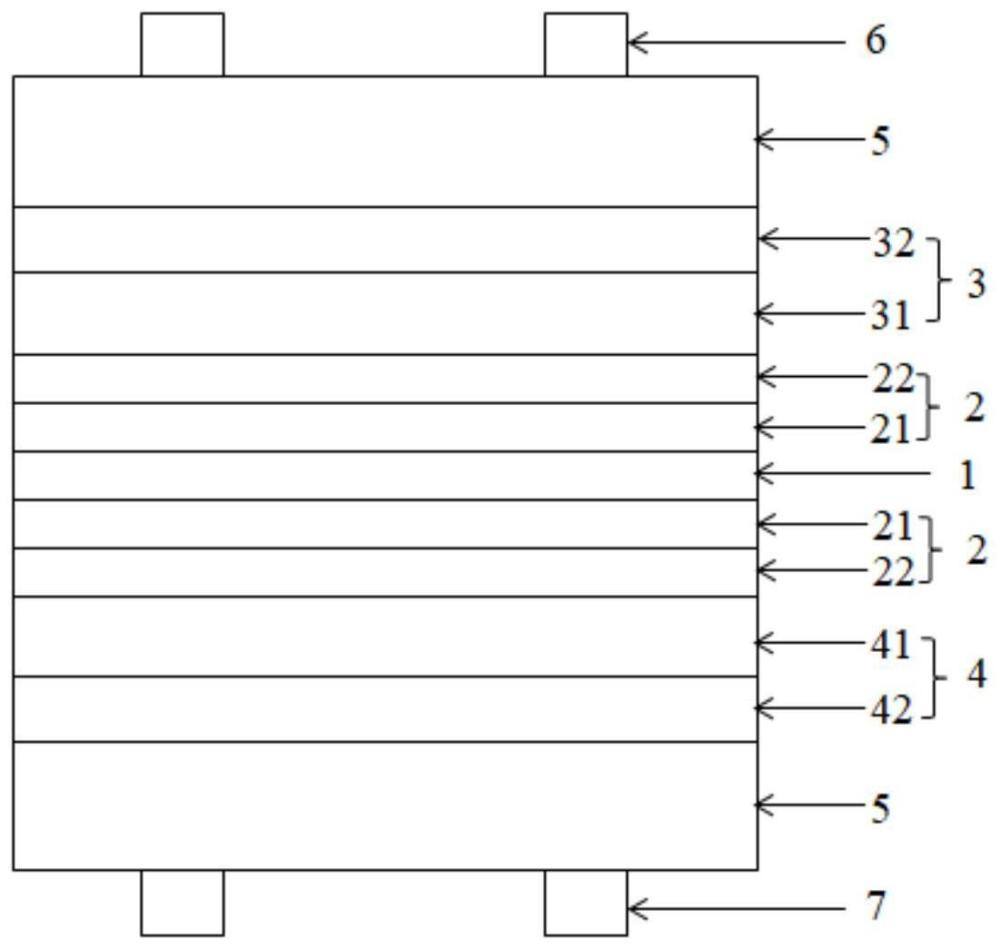

102、优选地,所述异质结电池包括依次叠加设置的正面电极、tco层、第二n型掺杂非晶硅层、第一n型掺杂非晶硅层、本征非晶硅外层、本征非晶硅内层、硅基体、本征非晶硅内层、本征非晶硅外层、第一p型掺杂非晶硅层、第二p型掺杂非晶硅层、tco层和背面电极。

103、与现有技术相比,本发明具有以下有益效果:

104、本发明中,通过对异质结电池制备方法的设计,进一步通过使用包括氢气和掺杂气体的组合对掺杂非晶硅层进行等离子体处理,提高了异质结电池的开路电压、填充因子和光电转换效率,降低了异质结电池的接触电阻,其开路电压提高了0.3~1.2mv,填充因子提高了0.07%~0.35%,接触电阻降低了0.09~0.3mω,光电转换效率提升了0.07~0.16%。

- 还没有人留言评论。精彩留言会获得点赞!