半导体结构及其形成方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、传统cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)器件由于受玻尔兹曼限制,亚阈摆幅室温下存在最小值,所以随着cmos器件尺寸的进一步微缩,静态功耗随工作电压降低而指数上升。因此,cmos一般用于高性能技算,动态功耗占主导。

2、与常规cmos不同的是,tfet(tunneling field-effect transistor,隧穿场效应晶体管)的源区与漏区的掺杂类型不同,tfet将源区-沟道-漏区结构换成p-i-n结构,利用带带隧穿作为导通机制,可以突破亚阈摆幅限制,能够实现极低静态泄漏电流以及更低的工作电压,从而降低静态功耗。

3、因此,具有优秀亚阈值特性的tfet器件可以与传统cmos器件混合集成来降低电路的整体功耗,电路中高频部分由常规cmos器件完成,低频部分由tfet器件完成,这种混合集成方式在物联网中有广泛的应用。

4、但是,目前tfet器件的性能仍有待提高。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构及其形成方法,优化了半导体器件的性能。

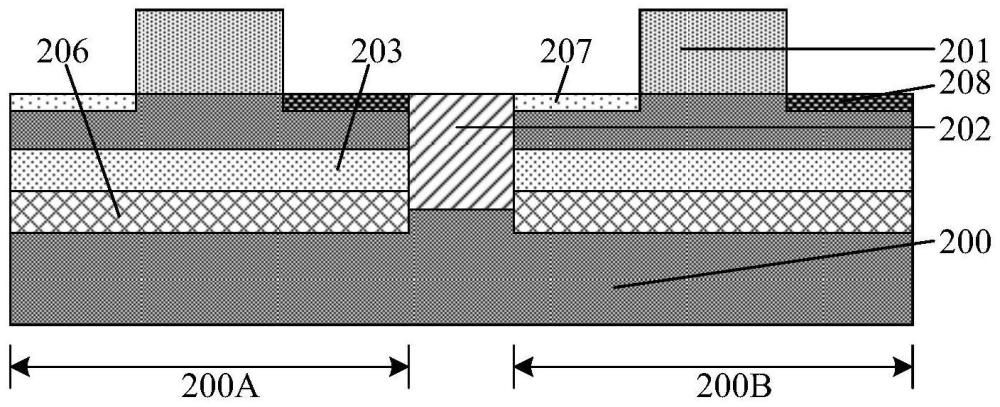

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:基底,基底包括第一器件区和第二器件区;第一晶体管,位于第一器件区的基底上,第一晶体管包括栅极结构以及分别位于栅极结构两侧的源区和漏区,同一第一晶体管对应的源区和漏区的掺杂类型不同;第二晶体管,位于第二器件区的基底上,第二晶体管包括栅极结构以及分别位于栅极结构两侧的源区和漏区,第二晶体管对应的源区和漏区的掺杂类型不同,第一晶体管与第二晶体管类型不同;器件隔离结构,位于相邻第一器件区和第二器件区交界处的基底中;第一型掺杂层,位于第一器件区和第二器件区的基底中;第二型掺杂层,位于第一型掺杂层顶部的基底中,且与第一型掺杂层的顶部相接触,第二型掺杂层的底部高于器件隔离结构的底部或者与器件隔离结构的底部相齐平,且器件隔离结构覆盖第二型掺杂层的侧壁,第一型掺杂层和第二型掺杂层的掺杂类型不同。

3、相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供基底,基底包括用于形成第一晶体管的第一器件区和用于形成第二晶体管第二器件区,在第一器件区和第二器件区的基底上形成有栅极结构,相邻第一器件区和第二器件区交界处的基底中形成有器件隔离结构;在第一器件区和第二器件区的基底中形成第一型掺杂层以及位于第一型掺杂层顶部的第二型掺杂层,第二型掺杂层与第一型掺杂层相接触,第二型掺杂层的底部高于器件隔离结构的底部或者与器件隔离结构的底部相齐平,且器件隔离结构覆盖第二型掺杂层的侧壁,第一型掺杂层和第二型掺杂层的掺杂类型不同;形成第一型掺杂层和第二型掺杂层之后,在第一器件区中,在栅极结构两侧的基底中分别形成源区和漏区,栅极结构以及位于其两侧的源区和漏区构成第一晶体管,第一晶体管对应的漏区和源区的掺杂类型不同,在第二器件区中,在栅极结构两侧的基底中分别形成源区和漏区,栅极结构以及位于其两侧的源区和漏区构成第二晶体管,第二晶体管对应的漏区和源区的掺杂类型不同,第一晶体管与第二晶体管类型不同。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供的半导体结构的形成方法中,在第一器件区和第二器件区的基底中形成第一型掺杂层以及位于第一型掺杂层顶部的第二型掺杂层,第二型掺杂层与第一型掺杂层相接触,第二型掺杂层的底部高于器件隔离结构的底部或者与器件隔离结构的底部相齐平,且器件隔离结构覆盖第二型掺杂层的侧壁,第一型掺杂层和第二型掺杂层的掺杂类型不同,相应的,在后续形成漏区与源区之后,由于器件隔离结构覆盖第二型掺杂层的侧壁,且第二型掺杂层的底部高于器件隔离结构的底部或者与器件隔离结构的底部相齐平,第二型掺杂层将相邻第一晶体管和第二晶体管中与第二型掺杂层的掺杂类型相反的源区或漏区隔离开,减少了相邻第一晶体管和第二晶体管中与第二型掺杂层的掺杂类型相反的源区或漏区之间通过第一晶体管和第二晶体管下方位置以及器件隔离结构拐角处发生漏电的概率,由于第一型掺杂层位于第二型掺杂层的底部,且与第二型掺杂层的底部相接触,第一型掺杂层将相邻第一晶体管和第二晶体管中与第一型掺杂层的掺杂类型相反的源区或漏区隔离开,减少了相邻第一晶体管和第二晶体管中与第一型掺杂层的掺杂类型相反的源区或漏区之间发生漏电的概率,同时,由于第一型掺杂层与第二型掺杂层相接触,第一型掺杂层与第二型掺杂层的界面处能够形成耗尽层,耗尽层的形成减少了相邻第一晶体管和第二晶体管中的源区或漏区在第一型掺杂层与第二型掺杂层之间通过第一晶体管下方位置和第二晶体管下方位置以及器件隔离结构拐角处产生漏电通道的概率,即降低了相邻第一晶体管和第二晶体管中的源区或漏区之间发生漏电的概率,从而提高了半导体结构的性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述第一型掺杂层位于所述器件隔离结构侧部的基底中,且所述第一型掺杂层的侧壁与所述器件隔离结构的侧壁相齐平,且所述第一型掺杂层的顶部高于所述器件隔离结构的底部或者与所述器件隔离结构的底部相齐平;

3.如权利要求1所述的半导体结构,其特征在于,所述第一型掺杂层中掺杂离子的浓度为1e12atom/cm3至1e14atom/cm3;

4.如权利要求1所述的半导体结构,其特征在于,沿所述基底的法线方向,所述第二型掺杂层的顶部至所述源区或漏区底部的距离为150纳米至800纳米。

5.如权利要求1所述的半导体结构,其特征在于,沿所述基底表面的法线方向,所述第一型掺杂层的厚度为40纳米至300纳米;

6.如权利要求1所述的半导体结构,其特征在于,所述第一型掺杂层中掺杂的离子类型为p型离子;所述第二型掺杂层中掺杂的离子类型为n型离子;

7.如权利要求1所述的半导体结构,其特征在于,所述第一晶体管为n型晶体管,所述第二晶体管为p型晶体管;其中,所述n型晶体管的漏区的掺杂离子为n型离子,所述n型晶体管的源区的掺杂离子为p型离子,所述p型晶体管的漏区的掺杂离子为p型离子,所述p型晶体管的源区的掺杂离子为n型离子。

8.如权利要求1所述的半导体结构,其特征在于,所述第一晶体管和第二晶体管包括隧穿场效应晶体管。

9.如权利要求1或8所述的半导体结构,其特征在于,所述基底还包括第三器件区;

10.一种半导体结构的形成方法,其特征在于,包括:

11.如权利要求10所述的半导体结构的形成方法,其特征在于,形成所述第一型掺杂层和第二型掺杂层的步骤包括:在所述器件隔离结构侧部的基底中形成所述第一型掺杂层,所述第一型掺杂层的侧壁与所述器件隔离结构的侧壁相齐平,且所述第一型掺杂层的顶部高于所述器件隔离结构的底部或者与所述器件隔离结构的底部相齐平;形成所述第一型掺杂层之后,在所述第一型掺杂层的顶部形成第二型掺杂层,所述器件隔离结构覆盖所述第二型掺杂层的侧壁;

12.如权利要求10所述的半导体结构的形成方法,其特征在于,采用同一光罩,形成所述第一型掺杂层和第二型掺杂层。

13.如权利要求10所述的半导体结构的形成方法,其特征在于,形成所述第一型掺杂层和第二型掺杂层的工艺包括离子注入工艺。

14.如权利要求13所述的半导体结构的形成方法,其特征在于,形成所述第一型掺杂层的过程中,所述离子注入工艺的参数包括:掺杂剂量范围为1e12atom/cm3至1e14atom/cm3;注入能量范围为50kev至500kev;

15.如权利要求10所述的半导体结构的形成方法,其特征在于,沿所述基底表面的法线方向,所述第二型掺杂层的顶部至所述基底顶面的距离为150纳米至800纳米。

16.如权利要求10所述的半导体结构的形成方法,其特征在于,沿所述基底的法线方向,所述第一型掺杂层的厚度为40纳米至300纳米;

17.如权利要求10所述的半导体结构的形成方法,其特征在于,所述第一型掺杂层中掺杂的离子类型为p型离子;所述第二型掺杂层中掺杂的离子类型为n型离子;

18.如权利要求10所述的半导体结构的形成方法,其特征在于,所述第一晶体管为n型晶体管,所述第二晶体管为p型晶体管;

19.如权利要求10所述的半导体结构的形成方法,其特征在于,所述第一晶体管和第二晶体管包括隧穿场效应晶体管。

20.如权利要求10或19所述的半导体结构的形成方法,其特征在于,所述提供基底的步骤中,所述基底还包括用于形成第三晶体管的第三器件区,所述第三晶体管包括金属氧化物半导体场效应晶体管;

技术总结

一种半导体结构及其形成方法,方法包括:在第一器件区和第二器件区的基底中形成第一型掺杂层以及位于第一型掺杂层顶部的第二型掺杂层,第二型掺杂层与第一型掺杂层相接触,第二型掺杂层的底部高于器件隔离结构的底部或者与器件隔离结构的底部相齐平,且器件隔离结构覆盖第二型掺杂层的侧壁,第一型掺杂层和第二型掺杂层的掺杂类型不同;在第一器件区和第二器件区中,在栅极结构两侧的基底中分别形成源区和漏区,栅极结构以及位于其两侧的源区和漏区构成第一晶体管,同一第一晶体管对应的漏区和源区的掺杂类型不同。第一型掺杂层和第二型掺杂层降低了相邻第一晶体管和第二晶体管中的源区或漏区之间发生漏电的概率,从而提高了半导体结构的性能。

技术研发人员:武咏琴,卜伟海,任烨

受保护的技术使用者:北方集成电路技术创新中心(北京)有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!