一种具有低导通电阻和低开关损耗的SIC半导体功率器件的制作方法

一种具有低导通电阻和低开关损耗的sic半导体功率器件

技术领域

1.本发明主要涉及半导体功率器件,更具体地,本发明涉及一种碳化硅(sic)沟槽式mosfet(金属氧化物半导体场效应晶体管),其具有第一和第二类型栅沟槽结构,用于形成栅极和用作栅氧化层电场降低区(goer)的接地p屏蔽区(ps)。该器件还进一步包括位于体区下方、围绕第一类型栅沟槽的电流扩散层,以获得更低的栅氧化层电场强度,更低的导通电阻,更小的栅-漏电荷(qgd)和更低的开关损耗。

背景技术:

2.由于sic的物理特性,相比si-mosfets,sic-mosfets具有更高的击穿电压,更低的导通电阻和更快的开关速度。然而,sic-mosfets因sic和栅氧化层间的界面态较差,需要较高的vgs才能完全打开器件通道,因此相比si-mosfets,sic-mosfets具有更高的栅氧化层电场强度。例如,对于si器件,vgs=10v能完全打开器件通道,但对于sic器件而言,vgs=18v才能完全打开器件通道。vgs越高,则栅氧化层电场强度会越高,从而导致可靠性问题。

3.另一个问题是,如图1所示,sic器件沟槽底部生长的栅氧化层的厚度比沟槽侧壁薄的多(薄了约3~5倍),这不仅会导致更大的qgd,还会大大提高沟槽底部栅氧化层的电场强度。图1所示的器件结构与传统的si沟槽式mosfet类似,除了n+sic衬底101和sic外延层102,具有n+源区111和p体区110。填充栅电极105的栅沟槽103形成于外延层102中,且栅沟槽103的沟槽侧壁和沟槽底部分别热氧化生长栅氧化层109和106。由于sic晶面中si面沟槽底部的氧化速率最低,使得栅氧化层106的厚度薄于109。

4.因此,在半导体器件的设计和制造领域,特别是sic沟槽式mosfet的设计和制造领域,仍需要提供一种新型的单元结构、器件结构和制造方法可以解决以上所涉及的困难和限制,使得sic沟槽式mosfet具有更低的栅氧化层电场强度,获得更低的导通电阻,更小的qgd和更低的开关损耗。

技术实现要素:

5.本发明公开了一种新型的sic沟槽式mosfet,其具有第一和第二类型栅沟槽,用于形成栅极和用作栅氧化层电场降低区的接地p屏蔽区(ps),其中栅极位于第一类型栅沟槽内,且第一类型栅沟槽的沟槽底部具有厚氧化层,接地ps区围绕在完全被厚氧化层填充的第二类型栅沟槽周围,且至少通过一个接地p区(gp)连接体区并连接至源金属。由于第二类型栅沟槽的沟槽宽度窄于第一类型栅沟槽,可将ps区的宽度设计的比第一类型栅沟槽窄。因此,两个相邻ps区之间的夹断效应被减弱,从而降低了导通电阻。该器件还进一步包括位于体区下方、围绕第一类型栅沟槽的电流扩散层(csl),以进一步避免两个相邻ps区之间的夹断效应,从而进一步降低导通电阻,其中,csl的掺杂浓度(ncs)高于外延层(nepi)。由于器件的厚底部氧化层的存在,相比传统sic mosfet,本发明的sic mosfet具有更小的qgd,并可进一步降低开关损耗。

6.本发明的一个方面,是公开了一种包含多个单元的sic功率器件,其中每个单元均

位于有源区内,进一步包括:一个外延层,其具有第一导电类型,且位于衬底之上;至少一个条形栅沟槽,其被具有第一导电类型的源区所包围,源区位于具有第二导电类型的体区中,并接近外延层的上表面;每个条形栅沟槽都包括一个第一类型栅沟槽和一个第二类型栅沟槽;第一类型栅沟槽位于第二类型栅沟槽之上,且其沟槽宽度大于第二类型栅沟槽;一个栅极,位于第一类型栅沟槽内,并被位于第一类型栅沟槽底部的第一绝缘层和第一类型栅沟槽侧壁的第二绝缘层所包围;第一绝缘层的厚度大于第二绝缘层。一个p屏蔽区(ps),用作栅氧化层电场降低区,其具有第二导电类型并围绕第二类型栅沟槽,其中第二类型栅沟槽完全被第一绝缘层所填充;至少一个接地p区(gp),其具有第二导电类型,围绕第一类型栅沟槽的侧壁和底部,并连接体区和ps区;体区和源区,通过多个源接触区连接至源金属。因此,ps区与源金属通过接地gp区接地。

7.根据本发明的另一个方面,在一些优选实施例中,衬底具有第一导电类型。在另一些优选实施例中,衬底具有第一导电类型,还进一步包括:一个具有第二导电类型的ps区,用作栅氧化层电场降低区,其毗邻体区的下表面、并临近条形栅沟槽。在另一些优选实施例中,器件还进一步包括一个超级结结构,所述超级结结构包括位于衬底之上的、具有第二导电类型的p柱区。

8.根据本发明的另一个方面,在一些优选实施例中,衬底具有所述的第一导电类型,外延层为具有均匀掺杂浓度的单一外延层。在另一些优选实施例中,衬底具有第一导电类型,外延层为具有均匀掺杂浓度、且电阻率为r的单一外延层,所述沟槽式半导体功率器件还进一步包括一个具有第一导电类型、且电阻率为rn的缓冲层,所述缓冲层位于衬底和外延层之间,其中r》rn。在另一些优选实施例中,衬底具有第二导电类型,外延层为具有均匀掺杂浓度、且电阻率为r的单一外延层,所述沟槽式半导体功率器件还进一步包括一个具有第一导电类型、且电阻率为rn的缓冲层,所述缓冲层位于衬底和外延层之间,其中r》rn。

9.根据本发明的另一个方面,在一些优选实施例中,衬底具有第二导电类型,还进一步包括:一个缓冲层,其为第一导电类型,且位于衬底和外延层之间;以及多个位于衬底的、具有第一导电类型的重掺杂区域,形成多个交替的p+区和n+区。

10.根据本发明的另一个方面,还公开了一种sic功率器件,还进一步包括,一个具有第一导电类型的电流扩散层(csl),其至少包围位于有源区内的第一类型栅沟槽的沟槽侧壁,其中csl的掺杂浓度高于外延层。

11.根据本发明的另一个方面,在一些优选实施例中,超级结结构的p柱区可通过多外延法形成。在另一些优选实施例中,超级结结构的p柱区可通过在深沟槽中填充具有第二导电类型的外延层形成。

12.发明还公开了一种用于制造sic功率器件的方法,其包括以下步骤:生长具有第一导电类型的外延层于具有第一导电类型的衬底之上,其中,外延层的掺杂浓度低于衬底;通过实施以下步骤形成第一类型和第二类型栅沟槽:

13.(a)在外延层的上表面形成沟槽掩膜版,用于定义多个第一类型栅沟槽;

14.(b)通过刻蚀沟槽掩膜版中的开放区域,在外延层中形成第一类型栅沟槽;

15.(c)在第一类型栅沟槽的侧壁和底部形成一层介电层;

16.(d)通过各向异性刻蚀去除第一类型栅沟槽的底部;

17.(e)实施各向异性硅刻蚀,形成多个第二类型栅沟槽。

18.根据本发明的另一个方面,在一些优选实施例中,用于制造沟槽式半导体功率器件的方法,其进一步包括以下步骤:实施角度离子注入,将第二导电类型掺杂物注入到第二类型栅沟槽的侧壁和底部,以形成围绕在第二类型栅沟槽周围的第二导电类型掺杂区。

19.根据本发明的另一个方面,在一些优选实施例中,用于制造沟槽式半导体功率器件的方法,其进一步包括以下步骤:实施第二导电类型掺杂物的零度离子注入。

20.根据本发明的另一个方面,在一些优选实施例中,用于制造沟槽式半导体功率器件的方法,其进一步包括以下步骤:在步骤(e)之后沉积bsg层至沟槽中,以形成围绕沟槽较低部分的第二导电类型掺杂区。

21.根据本发明的另一个方面,在一些优选实施例中,用于制造沟槽式半导体功率器件的方法,其进一步包括以下步骤:形成一个接地p区(gp)掩膜版,采用湿法介电层刻蚀法和第二导电类型掺杂物的角度离子注入,将第二导电类型掺杂物注入到第一类型栅沟槽的侧壁和底部,形成围绕在第一类型栅沟槽周围的第二导电类型掺杂区。

22.根据本发明的另一个方面,在一些优选实施例中,用于制造沟槽式半导体功率器件的方法,其进一步包括以下步骤:

23.(f)移除介电层;

24.(g)沿第一类型和第二类型栅沟槽的内表面,形成第一绝缘层,其中第二类型栅沟槽完全被第一绝缘层所填充;

25.(h)沿第一类型栅沟槽的上部,回刻蚀第一绝缘层;

26.(i)沿沟槽的侧壁形成第二绝缘层作为栅氧化层;

27.(j)沉积掺杂多晶硅层至第一类型栅沟槽中;

28.(k)回刻蚀第一掺杂多晶硅层,作为栅电极。

29.通过参考以下各个附图,阅读下文对优选实施例的详细描述,本发明的上述及其他的目的和优点对于本领域的普通技术人员来说无疑是显而易见的。

附图说明

30.图1是现有技术所揭示的一种具有沟槽栅垂直双扩散mosfet的传统sic半导体器件的横截面图。

31.图2是根据本发明的一个优选的具有条形单元的超级结沟槽式mosfets的顶视图。

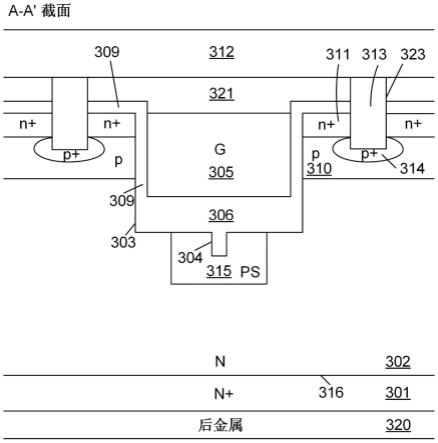

32.图3a是图2中a-a’截面的一个优选的横截面图。

33.图3b是图2中b-b’截面的一个优选的横截面图。

34.图4a是图2中a-a’截面的另一个优选的横截面图。

35.图4b是图2中b-b’截面的另一个优选的横截面图。

36.图5a是图2中a-a’截面的另一个优选的横截面图。

37.图5b是图2中b-b’截面的另一个优选的横截面图。

38.图6是图2中a-a’截面的另一个优选的横截面图。

39.图7是图2中b-b’截面的另一个优选的横截面图。

40.图8a是根据本发明的另一个优选实施例的横截面图。

41.图8b是根据本发明的另一个优选实施例的横截面图。

42.图9是根据本发明的一个优选的igbt实施例的横截面图。

43.图10是根据本发明的一个优选的具有集成的rc二极管的igbt实施例的横截面图。

44.图11a~11p是一系列的横截面图,显示图4a和图4b中sic超级结沟槽式mosfet的制造步骤。

具体实施方式

45.下面参照附图更详细地说明本发明,其中示出了本发明的优选实施例。本发明可以,但是以不同的方式体现,但是不应该局限于在此所述的实施例。例如,这里的说明更多地引用n沟道的半导体集成电路,但是很明显其他器件也是可能的。下文是通过参考各个附图来对实践本发明的优选实施例进行详细描述。一些方向术语,例如“顶部”、“底部”、“前”、“后”、“上方”、“下方”等,是参考各个附图的方向进行描述的。由于实施例中的元件可以被放置在许多不同的方向,因此,本发明中的方向术语只是用于描述而不能被视为对本发明的限制。应该理解的是,实施例中各种结构或者逻辑上的替代和修改都应该被涵盖在本发明的真正精神和范围内。因此,以下的详细描述不能被视为对本发明的限制,本发明的涵盖范围由附后的权利要求界定。应该理解的是,本发明中所描述的各个优选实施例的发明特征可以相互结合,有特别说明的除外。

46.图2所示的是根据本发明的一个优选的具有条形单元的沟槽式mosfets的顶视图。在每个单元中,栅沟槽201均围绕在p屏蔽区(ps)202的周围,其中栅沟槽201为条形,ps区202与接地p区(gp)相连。沟槽式源接触区203位于每两个相邻的栅沟槽201之间。

47.图3a所示的是图2所示优选实施例的a-a’截面的横截面图。所述sic功率器件包括一个在n型sic外延层302上形成的超级结沟槽式mosfet,该外延层302位于n+sic衬底301之上,其中,n+sic衬底301的背面涂有ti/ni/ag后金属层320用作漏金属。在n外延层302中,形成多个包括第一类型栅沟槽303和第二类型栅沟槽304的沟槽,所述沟槽从外延层302的上表面向下延伸入外延层302中,并未接触到n外延层302和n+衬底301的界面316,其中,第一类型栅沟槽303位于第二类型栅沟槽304之上,且第一类型栅沟槽303宽度大于第二类型栅沟槽304。栅极305,位于第一类型栅沟槽303的较高部分,并被位于栅沟槽303底部的、作为第一绝缘层306的厚底部氧化层以及位于栅沟槽303侧壁的第二绝缘层309所围绕,其中第二绝缘层309的厚度小于第一绝缘层306,第二类型栅沟槽304完全被第一绝缘层306所填充。在每两个相邻的第一类型栅沟槽303之间,形成一个具有n+源区311的p体区310,其从n外延层302的上表面附近延伸并围绕被衬以第二栅绝缘层309的栅电极305。介电隔层321形成于外延层302之上,源金属312形成于介电隔层321之上。p体区310和n+源区311进一步通过多个沟槽式接触区323连至源金属312,其中,沟槽式接触区323填充以接触插塞313,接触插塞313和源金属312均为ti/tin/al合金,且沟槽式接触区323的底部被位于n+源区311下方的p+体接触区314所围绕。根据本发明,引入毗邻第二类型栅沟槽304侧壁和底部的p屏蔽区(ps)315至n外延层202中,所述ps区315可通过对第二类型栅沟槽304的侧壁和底部实施角度硼离子注入,或角度和零度硼离子注入相结合的方式,或bsg层沉积步骤形成。由于第二类型栅沟槽304的沟槽宽度窄于第一类型栅沟槽303,可将ps区315的宽度设计地比第一类型栅沟槽303窄。

48.图3b所示的是图2所示优选实施例的b-b’截面的横截面图,所述的沟槽式功率器件与图3a所述的发明具有相似的结构,除了在本发明的结构中,还存在一个围绕第一类型

栅沟槽303’侧壁和底部的接地p区(gp)317’,所述gp区317’连接p体区310’和p屏蔽区(ps)315’并连接至源金属312’。由于第二类型栅沟槽304’的沟槽宽度窄于第一类型栅沟槽303’,可将ps区315’的宽度设计地比第一类型栅沟槽303’窄。因此,两个相邻ps区315’之间的夹断效应被减弱,从而降低了导通电阻。

49.图4a所示的是图2所示另一个优选实施例a-a’截面的横截面图。所述的沟槽式半导体功率器件与图3a所述的发明具有相似的结构,除了在本发明的结构中,还包括一个p型栅氧化层电场降低区418(pr,如图所示)作为第二屏蔽区,其毗邻p体区410的下表面、并临近栅沟槽。此发明结构中的沟槽式源接触区423所填充的接触插塞413为ti/tin/w,源金属412为al合金。

50.图4b所示的是图2所示另一个优选实施例b-b’截面的横截面图。所述的沟槽式半导体功率器件与图4a所述的发明具有相似的结构,除了在本发明的结构中,还存在一个围绕第一类型栅沟槽403’侧壁和底部的接地p区(gp)417’,所述gp区417’连接p体区410’和p屏蔽区(ps)415’并连接至源金属412’。

51.图5a所示的是图2所示另一个优选实施例a-a’截面的横截面图。所述的沟槽式半导体功率器件与图3a所述的发明具有相似的结构,除了在本发明的结构中,引入p柱区519至n外延层502中形成超级结区,所述超级结区包括多个位于衬底501之上、交替排列的p柱区519和n区502。其中,p柱区519位于p体区510的下方、n外延层502的底部表面516的上方,所述p柱区可通过多外延法形成,也可通过在深沟槽中填充具有第二导电类型的外延层形成。本发明结构中的沟槽式源接触区523所填充的接触插塞513为ti/tin/al,源金属512为ti/tin/al合金。

52.图5b所示的是图2所示另一个优选实施例b-b’截面的横截面图。所述的沟槽式功率器件与图5a所述的发明具有相似的结构,除了在本发明的结构中,还存在一个围绕第一类型栅沟槽503’侧壁和底部的接地p区(gp)517’,所述gp区517’连接p体区510’和p屏蔽区(ps)515’并连接至源金属512’。

53.图6所示的是图2所示另一个优选实施例a-a’截面的横截面图。所述的沟槽式功率器件与图3a所述的发明具有相似的结构,除了在本发明的结构中,还包括一个位于p体区610下方、n外延层602较高部分、具有第一导电类型的电流扩散层(csl)627,以进一步避免两个相邻p屏蔽区(ps)615之间的ps区夹断电流通路的形成,从而进一步降低导通电阻,其中,电流扩散层627的掺杂浓度(ncs)高于n外延层602的掺杂浓度(nepi)。本发明结构中的沟槽式源接触区623所填充的接触插塞613为ti/tin/al,源金属612为ti/tin/al合金。

54.图7所示的是图2所示另一个优选实施例a-a’截面的横截面图。所述的沟槽式功率器件与图4a所述的发明具有相似的结构,除了在本发明的结构中,还包括一个位于p体区710下方、n外延层702较高部分、具有第一导电类型的电流扩散层(csl)727,以进一步避免两个相邻p屏蔽区(ps)715之间的ps区夹断电流通路的形成,从而进一步降低导通电阻,其中,电流扩散层727的掺杂浓度(ncs)高于n外延层702的掺杂浓度(nepi)。本发明结构中的沟槽式源接触区723所填充的接触插塞713为ti/tin/w,源金属712为al合金。

55.图8a所示的是根据本发明的另一个优选实施例。所述的沟槽式功率器件与图5a所述的发明具有相似的结构,除了在本发明的结构中,还包括一个位于p体区810下方、n外延层802较高部分、具有第一导电类型的电流扩散层(csl)827,以进一步避免两个p屏蔽区

(ps)815之间的ps区夹断电流通路的形成,从而进一步降低导通电阻,其中,电流扩散层827的掺杂浓度(ncs)高于n外延层802的掺杂浓度(nepi)。本发明结构中的沟槽式源接触区823所填充的接触插塞813为ti/tin/w,源金属812为al合金。

56.图8b所示的是根据本发明的另一个优选实施例。所述的沟槽式功率器件与图8a所述的发明具有相似的结构,除了在本发明的结构中,还进一步包括一个电阻率为rn的n缓冲层822’,所述缓冲层822’位于n+衬底801’和n外延层802’之间,所述n外延层802’为具有均匀掺杂浓度、且电阻率为r的单一外延层,其中r》rn。此外,p柱区819’位于p体区810’的下方、并接触至n外延层802’的底部表面816’,所述p柱区819’可通过多外延法形成,也可通过在深沟槽中填充具有第二导电类型的外延层形成。

57.图9所示的是根据本发明的另一个优选实施例,所述的沟槽式半导体功率器件为igbt(绝缘栅双极晶体管)器件,本发明与图8b所述的发明具有相似的结构,除了在本发明中,所述igbt器件形成在p+衬底901之上,还进一步包括一个位于p+衬底901和n外延层902之间的、电阻率为rn的n缓冲层922,所述n外延层902为具有均匀掺杂浓度、且电阻率为r的单一外延层,其中r》rn。

58.图10所示的是根据本发明的另一个优选实施例,所述的沟槽式半导体功率器件为另一个igbt器件,本发明与图9所述的发明具有相似的结构,除了在本发明中,还进一步包括位于p+衬底1001的多个重掺杂n+区1031,用于形成多个交替排列的p+和n+区,作为集成的rc二极管。

59.图11a~11p是一系列典型的制造步骤,用于形成本发明图4a和图4b中的优选实施例。如图11a所示,首先在n+sic衬底1101上生长一层n外延层1102,其中n外延层1102的掺杂浓度低于n+衬底1101。随后,在位于有源区的n外延层1102内形成p体区1110和n+源区1111。在n外延层1102的上表面形成一层如氧化层的硬掩膜版1113,用于定义多个第一类型栅沟槽1103。随后,采用干法氧化层刻蚀法以及干法硅刻蚀法,形成多个第一类型栅沟槽1103,所述栅沟槽穿过硬掩膜版中的开放区域延伸入n外延层1102中,且其底部并未接触到n外延层1102的底部表面1116。生长一层牺牲氧化层(图中未显示)并去除,以消除形成栅沟槽1103的过程中引入的等离子体损伤。

60.如图11b所示,通过氧化层沉积法或热氧化生长法,在第一类型栅沟槽1103的侧壁和底部形成一层介电层1117。

61.如图11c所示,采用干法氧化层刻蚀法,去除位于第一类型栅沟槽1103底部的介电层1117。

62.如图11d所示,采用各向异性硅刻蚀法,形成多个第二类型栅沟槽1104。

63.如图11e所示,在第二类型栅沟槽1104的侧壁和底部,依次实施角度硼离子注入和扩散步骤,形成围绕第二类型栅沟槽1104的p*区1125。此外,如果栅沟槽1104的底部过窄,则采用零度注入和角度注入相结合的方式实现硼离子的注入。

64.如图11f所示,沉积bsg层于所述的两种类型的沟槽内,为形成围绕第二类型栅沟槽1104的p*区1125提供了另一种方法。

65.如图11g和图11h所示,在n外延层1102的上表面形成一层如氧化层的接地p区(gp)掩膜版,采用湿法介电层刻蚀法和具有第二导电类型掺杂物的角度离子注入,将第二导电类型掺杂物注入到第一类型栅沟槽1103的侧壁和底部,形成围绕在第一类型栅沟槽1103周

围的第二导电类型掺杂区,分别形成a-a’截面和b-b’截面的横截面结构。

66.如图11i所示,形成具有p屏蔽区(ps)1115的a-a’截面的横截面结构,随后移除接地p区(gp)掩膜版和介电层1117。通过热氧化层生长法或厚氧化层沉积法,沿两种类型栅沟槽1103和1104的内壁以及n外延层1102的上表面生长一层厚氧化层作为第一绝缘层1106,其中第二类型栅沟槽1104完全被第一绝缘层1106所填充。

67.如图11j所示,形成具有p屏蔽区(ps)1115和接地p区(gp)1117的b-b’截面的横截面结构,随后移除接地p区(gp)掩膜版和介电层1117。通过热氧化层生长法或厚氧化层沉积法,沿两种类型栅沟槽1103和1104的内壁以及n外延层1102的上表面生长一层厚氧化层作为第一绝缘层1106,其中第二类型栅沟槽1104完全被第一绝缘层1106所填充。

68.如图11k所示为a-a’截面的横截面结构,从n外延层1102的上表面以及第一类型栅沟槽1103的上部回刻蚀第一绝缘层1106。

69.如图11l所示为b-b’截面的横截面结构,从n外延层1102的上表面以及第一类型栅沟槽1103的上部回刻蚀第一绝缘层1106。

70.如图11m所示为a-a’截面的横截面结构,采用热生长法或沉积法,沿第一类型栅沟槽1103的侧壁和n外延层1102的上表面形成第二绝缘层1109作为栅氧化层,所述第二绝缘层1109的厚度薄于第一绝缘层1106。随后,沉积第一掺杂多晶硅层于第一栅绝缘层1106之上,填充第一类型栅沟槽1103的较高部分,然后采用cmp法(化学机械抛光法)或等离子体刻蚀法将其回刻蚀,作为单栅电极1105。

71.如图11n所示为b-b’截面的横截面结构,采用热生长法或沉积法,沿第一类型栅沟槽1103的侧壁和n外延层1102的上表面形成第二绝缘层1109作为栅氧化层,所述第二绝缘层1109的厚度薄于第一绝缘层1106。随后,沉积第一掺杂多晶硅层于第一栅绝缘层1106之上,填充第一类型栅沟槽1103的较高部分,然后采用cmp法(化学机械抛光法)或等离子体刻蚀法将其回刻蚀,作为单栅电极1105。

72.如图11o所示为a-a’截面的横截面结构,采用传统技术,在整个结构的上表面形成第二介电层,所述第二介电层为无掺杂的氧化层以及bpsg层。在第二介电层的上表面覆盖一层掩膜版(图中未显示),将其回刻蚀以形成介电隔层1121。在介电隔层1121上覆盖一个接触区掩膜版(图中未显示),通过相继的干法氧化层刻蚀和干法硅刻蚀形成多个沟槽式接触区1123。所述沟槽式接触区1123穿过介电隔层1121、n+源区1111,延伸入p体区1110中,形成沟槽式源-体接触区。通过实施硼离子注入,形成p型栅氧化层电场降低区1118(pr,如图所示),其毗邻p体区1110的下表面、并临近沟槽1103。随后,实施bf2离子注入,在p体区1110内形成p+体接触掺杂区1114,其至少包围沟槽式源-体接触区1123的底部。随后,沉积ti/tin势垒金属层于沟槽式接触区1123的侧壁和底部,随后实施rta操作用于形成硅化物。沉积w金属层于势垒金属层之上,回刻蚀w金属层和势垒金属层,以在沟槽式源-体接触区1123形成ti/tin/w接触金属插塞1113。沉积一层al合金金属层于介电隔层1121的上表面,所述al合金金属层的下方衬以ti或ti/tin减阻层。随后,覆盖一个金属掩膜版(图中未显示),刻蚀金属层形成源金属1112。

73.如图11p所示为b-b’截面的横截面结构,采用传统技术,在整个结构的上表面形成第二介电层,所述第二介电层为无掺杂的氧化层以及bpsg层。在第二介电层的上表面覆盖一层掩膜版(图中未显示),将其回刻蚀以形成介电隔层1121。在介电隔层1121上覆盖一个

接触区掩膜版(图中未显示),通过相继的干法氧化层刻蚀和干法硅刻蚀形成多个沟槽式接触区1123。所述沟槽式接触区1123穿过介电隔层1121、n+源区1111,延伸入p体区1110中,形成沟槽式源-体接触区。通过实施硼离子注入,形成p型栅氧化层电场降低区1118(pr,如图所示),其毗邻p体区1110的下表面、并临近沟槽1103。随后,实施bf2离子注入,在p体区1110内形成p+体接触掺杂区1114,其至少包围沟槽式源-体接触区1123的底部。随后,沉积ti/tin势垒金属层于沟槽式接触区1123的侧壁和底部,随后实施rta操作用于形成硅化物。沉积w金属层于势垒金属层之上,回刻蚀w金属层和势垒金属层,以在沟槽式源-体接触区1123形成ti/tin/w接触金属插塞1113。沉积一层al合金金属层于介电隔层1121的上表面,所述al合金金属层的下方衬以ti或ti/tin减阻层。随后,覆盖一个金属掩膜版(图中未显示),刻蚀金属层形成源金属1112。

74.虽然依照优选实施例对本发明进行了描述,但应该理解的是上述公开不能被视为是对本发明的限制。在阅读了上述公开的内容之后,各种替代和修改对于本技术领域的技术人员无疑是显而易见的。因此,附后的权利要求应被解释为涵盖落入本发明的真正精神和范围内的所有替代和修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1