半导体结构的形成方法与流程

本发明涉及半导体制造,尤其涉及一种半导体结构的形成方法。

背景技术:

1、随着半导体器件集成度的提高,晶体管的关键尺寸不断缩小。然而,随着晶体管尺寸的急剧减小,栅介质层厚度与工作电压不能相应改变使抑制短沟道效应的难度加大,使晶体管的沟道漏电流增大。

2、鳍式场效应晶体管(fin field-effect transistor,finfet)的栅极成类似鱼鳍的叉状3d架构。finfet的沟道凸出衬底表面形成鳍部,栅极覆盖鳍部的顶面和侧壁,从而使反型层形成在沟道各侧上,可于鳍部的两侧控制电路的接通与断开。这种设计能够增加栅极对沟道区的控制,从而能够很好地抑制晶体管的短沟道效应。然而,鳍式场效应晶体管仍然存在短沟道效应。

3、此外,为了进一步减小短沟道效应对半导体器件的影响,降低沟道漏电流。半导体技术领域引入了应变硅技术,应变硅技术的方法包括:在栅极结构两侧的鳍部中形成凹槽;通过外延生长工艺在所述凹槽中形成源漏掺杂区。

4、为了防止不同晶体管的源漏掺杂区相互连接,需要在鳍部中形成隔离层,同时为了减小隔离层的面积,提高所形成半导体结构的集成度。现有技术引入了sdb(singlediffusion break)技术。

5、然而,现有方法在形成半导体结构的过程中仍存在诸多问题。

技术实现思路

1、本发明解决的技术问题是提供一种半导体结构的形成方法,以提升最终形成的半导体结构的性能。

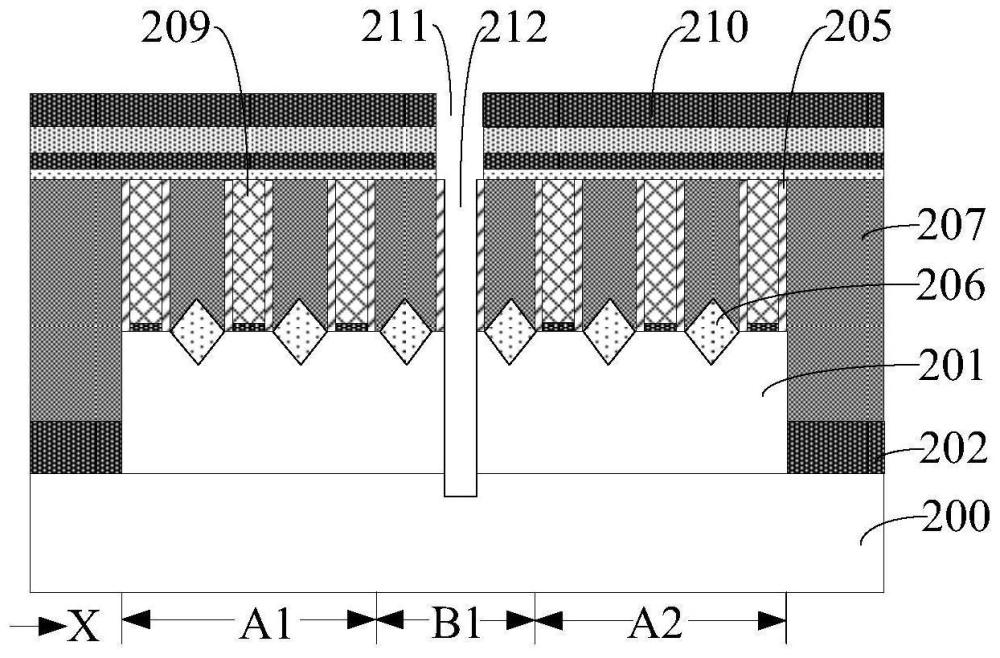

2、为解决上述问题,本发明提供一种半导体结构的形成方法,包括:提供衬底,所述衬底上具有鳍部,所述鳍部包括沿第一方向排布的若干器件区以及至少一个隔离区,所述隔离区位于相邻所述器件区之间;在所述衬底上形成介质层和第一栅极结构,所述第一栅极结构横跨所述鳍部,所述第一栅极结构位于所述隔离区上,所述介质层覆盖所述第一栅极结构的侧壁;在所述介质层上形成掩膜结构,所述掩膜结构内具有暴露出所述第一栅极结构顶部表面的掩膜开口;以所述掩膜结构为掩膜,采用各向异性干法刻蚀工艺去除所述第一栅极结构、以及部分被所述第一栅极结构覆盖的鳍部,在所述介质层和所述鳍部内形成隔离开口;在所述隔离开口内形成隔离结构。

3、可选的,所述各向异性干法刻蚀工艺包括:原子层干法刻蚀工艺。

4、可选的,所述原子层干法刻蚀工艺的刻蚀气体为ch2f2、o2和ar的混合气体。

5、可选的,所述原子层干法刻蚀工艺的刻蚀温度为25℃~50℃。

6、可选的,所述第一栅极结构的材料包括:金属;所述金属包括:钨。

7、可选的,所述掩膜结构为多层结构;所述掩膜结构包括自底部向顶部依次堆叠的第一掩膜层以及若干层第二掩膜层。

8、可选的,所述第一掩膜层的材料包括:氮化钽。

9、可选的,在形成所述介质层和所述第一栅极结构的过程中,还包括:在所述衬底上形成若干第二栅极结构,所述第二栅极结构横跨所述鳍部,所述第二栅极结构位于所述器件区上,所述介质层覆盖所述第二栅极结构的侧壁。

10、可选的,在形成所述第一栅极结构和所述第二栅极结构之前,还包括:在所述鳍部内形成若干源漏掺杂层,所述源漏掺杂层位于相邻的所述第一栅极结构和所述第二栅极结构之间、或相邻的所述第二栅极结构之间。

11、可选的,在形成所述源漏掺杂层之前,还包括:在所述衬底上形成第一伪栅结构,所述第一伪栅结构横跨所述鳍部,所述第一伪栅结构位于所述隔离区上;在所述衬底上形成若干第二伪栅结构,所述第二伪栅结构横跨所述鳍部,所述第二伪栅结构位于所述器件区上。

12、可选的,所述源漏掺杂层的形成方法包括:以所述第一伪栅结构和所述第二伪栅结构为掩膜刻蚀所述鳍部,在所述鳍部内形成若干源漏开口;在所述源漏开口内形成所述源漏掺杂层。

13、可选的,所述第一栅极结构和若干所述第二栅极结构的形成方法包括:去除所述第一伪栅结构,在所述介质层内形成第一栅极开口;在所述第一栅极开口内形成所述第一栅极结构;去除所述第二伪栅结构,在所述介质层内形成第二栅极开口;在所述第二栅极开口内形成所述第二栅极结构。

14、可选的,所述隔离结构的形成方法包括:在所述隔离开口内、以及所述介质层上形成初始隔离结构;对所述初始隔离结构进行平坦化处理,直至暴露出所述介质层的顶部表面为止,形成所述隔离结构。

15、可选的,所述隔离结构的材料包括氮化硅。

16、与现有技术相比,本发明的技术方案具有以下优点:

17、本发明的技术方案的形成方法中,以所述掩膜结构为掩膜,采用各向异性干法刻蚀工艺去除所述第一栅极结构、以及所述第一栅极结构覆盖的部分所述鳍部,在所述介质层和所述鳍部内形成隔离开口。通过各向异性干法刻蚀工艺去除所述第一栅极结构,能够减少对所述第一栅极结构相邻的器件结构造成损伤,进而提升最终形成的半导体结构的性能。

18、进一步,所述第一栅极结构的材料包括:金属;所述金属包括:钨;所述掩膜结构为多层结构;所述掩膜结构包括自底部向顶部依次堆叠的第一掩膜层以及若干层第二掩膜层;所述第一掩膜层的材料包括:氮化钽;所述各向异性干法刻蚀工艺包括:原子层干法刻蚀工艺;所述原子层干法刻蚀工艺的工艺参数包括:刻蚀气体ch2f2、o2、ar;刻蚀时间为80s~120s;刻蚀温度为25℃~50℃。由于在25℃~50℃的刻蚀温度,能够使得所述原子层干法刻蚀工艺对钨和氮化钛的刻蚀选择比达到最大化,因此能够进一步减少对所述第一掩膜层的刻蚀损伤,进而减小对所述第一栅极结构相邻的器件结构造成损伤,进一步提升最终形成的半导体结构的性能。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,所述各向异性干法刻蚀工艺包括:原子层干法刻蚀工艺。

3.如权利要求2所述的半导体结构的形成方法,其特征在于,所述原子层干法刻蚀工艺的刻蚀气体为ch2f2、o2和ar的混合气体。

4.如权利要求2所述的半导体结构的形成方法,其特征在于,所述原子层干法刻蚀工艺的刻蚀时间为80s~120s。

5.如权利要求2所述的半导体结构的形成方法,其特征在于,所述原子层干法刻蚀工艺的刻蚀温度为25℃~50℃。

6.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一栅极结构的材料包括:金属;所述金属包括钨。

7.如权利要求1所述的半导体结构的形成方法,其特征在于,所述掩膜结构为多层结构;所述掩膜结构包括自底部向顶部依次堆叠的第一掩膜层以及若干层第二掩膜层,所述第一掩膜层的材料包括氮化钽。

8.如权利要求1所述的半导体结构的形成方法,其特征在于,在形成所述介质层和所述第一栅极结构的过程中,还包括:在所述衬底上形成若干第二栅极结构,所述第二栅极结构横跨所述鳍部,所述第二栅极结构位于所述器件区上,所述介质层覆盖所述第二栅极结构的侧壁。

9.如权利要求8所述的半导体结构的形成方法,其特征在于,在形成所述第一栅极结构和所述第二栅极结构之前,还包括:在所述鳍部内形成若干源漏掺杂层,所述源漏掺杂层位于相邻的所述第一栅极结构和所述第二栅极结构之间、或相邻的所述第二栅极结构之间。

10.如权利要求9所述的半导体结构的形成方法,其特征在于,在形成所述源漏掺杂层之前,还包括:在所述衬底上形成第一伪栅结构,所述第一伪栅结构横跨所述鳍部,所述第一伪栅结构位于所述隔离区上;在所述衬底上形成若干第二伪栅结构,所述第二伪栅结构横跨所述鳍部,所述第二伪栅结构位于所述器件区上。

11.如权利要求10所述的半导体结构的形成方法,其特征在于,所述源漏掺杂层的形成方法包括:以所述第一伪栅结构和所述第二伪栅结构为掩膜刻蚀所述鳍部,在所述鳍部内形成若干源漏开口;在所述源漏开口内形成所述源漏掺杂层。

12.如权利要求10所述的半导体结构的形成方法,其特征在于,所述第一栅极结构和若干所述第二栅极结构的形成方法包括:去除所述第一伪栅结构,在所述介质层内形成第一栅极开口;在所述第一栅极开口内形成所述第一栅极结构;去除所述第二伪栅结构,在所述介质层内形成第二栅极开口;在所述第二栅极开口内形成所述第二栅极结构。

13.如权利要求1所述的半导体结构的形成方法,其特征在于,所述隔离结构的形成方法包括:在所述隔离开口内、以及所述介质层上形成初始隔离结构;对所述初始隔离结构进行平坦化处理,直至暴露出所述介质层的顶部表面为止,形成所述隔离结构。

14.如权利要求1所述的半导体结构的形成方法,其特征在于,所述隔离结构的材料包括氮化硅。

技术总结

一种半导体结构的形成方法,包括:提供衬底,衬底上具有鳍部,鳍部包括沿第一方向排布的若干器件区以及至少一个隔离区,隔离区位于相邻器件区之间;在衬底上形成介质层和第一栅极结构,第一栅极结构横跨鳍部,第一栅极结构位于隔离区上,介质层覆盖第一栅极结构的侧壁;在介质层上形成掩膜结构,掩膜结构内具有暴露出第一栅极结构顶部表面的掩膜开口;以掩膜结构为掩膜,采用各向异性干法刻蚀工艺去除第一栅极结构、以及部分被第一栅极结构覆盖的鳍部,在介质层和鳍部内形成隔离开口;在隔离开口内形成隔离结构。通过各向异性干法刻蚀工艺去除第一栅极结构,能减少对第一栅极结构相邻的器件结构造成损伤,进而提升最终形成的半导体结构的性能。

技术研发人员:殷立强,司进,邱晶,张海洋

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!