半导体结构、形成方法及版图设计方法、电路及工作方法与流程

本发明涉及半导体制造领域,尤其涉及一种半导体结构、形成方法及版图设计方法、电路及工作方法。

背景技术:

1、随着半导体工艺节点尺寸的缩小,金属、通孔等结构的尺寸和间距也随之减小,许多新的工艺制程被引入以制备这些结构,如自对准多重曝光技术(self-align double/quadruple pattern,简称sadp/saqp),这些制程非常复杂,在线端(line-end)缺陷较多,对应于在芯片的边缘处,因而在芯片的边缘处需要留空白余量区域,以保证内部非边缘区域的正常工作。

2、这些缺陷对电路的影响有两种,一种是设计中断开的结构短路了,其原因可能有原本不相连的金属因为缺陷联结起来等。另一种是设计中是连接的结构断开了,其原因可能有金属在加工中缺失,或者过孔与金属没有接触等。

3、在芯片的边缘处留空白余量会导致芯片在面积上的增加,对于一些复杂的存储量多的芯片,这些空白余量造成的额外面积增加相当可观。

4、因此,对芯片边缘的工艺监控相当重要。

技术实现思路

1、本发明解决的技术问题是提供一种半导体结构、形成方法及版图设计方法、电路及工作方法,以对芯片边缘的工艺进行监控。

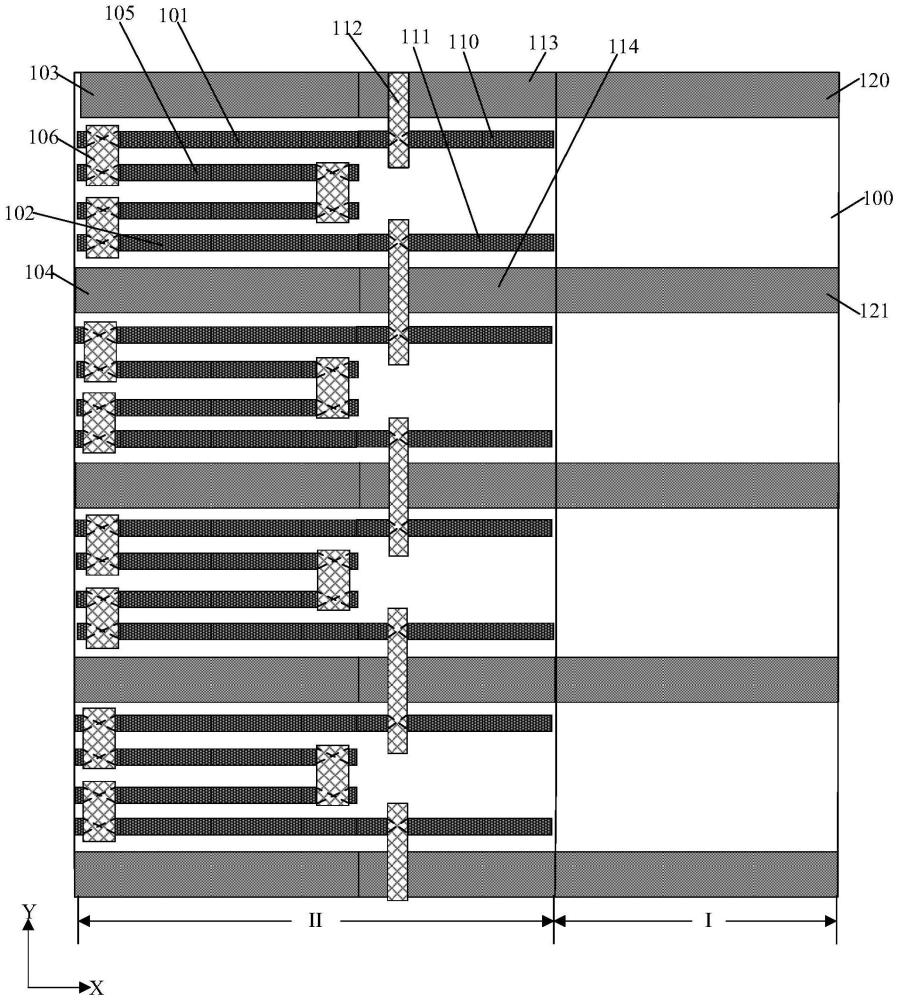

2、为解决上述技术问题,本发明技术方案提供一种半导体结构,包括:衬底,所述衬底包括中间区和位于中间区周围的边缘区;位于中间区上的若干层垂直堆叠的第一金属层和第二金属层,所述第一金属层平行于第一方向,所述第二金属层平行于第二方向,所述第一方向和第二方向平行于衬底表面,且所述第一方向和第二方向相互垂直;位于边缘区的若干相连接的边缘电路单元,所述边缘电路单元包括短路单元或开路单元,所述边缘电路单元包括至少一层金属结构,所述金属结构与所述第一金属层平行,且所述金属结构与第一金属层的顶部表面齐平。

3、可选的,若干所述边缘电路单元位于所述中间区沿第一方向两侧的边缘区上,若干所述边缘电路单元在边缘区上沿第二方向排列。

4、可选的,所述边缘电路单元包括短路单元;所述金属结构包括:第一输入端、第一输出端、第一电源端、第一接地端和若干第三金属层;所述短路单元还包括:位于第三金属层上、第一输入端上或第一输出端上的第一插塞,位于第一插塞上的第一连接层,所述第一连接层与第三金属层垂直;所述第一连接层电连接第一输入端、第一输出端和若干第三金属层,所述第一输入端和第一输出端之间的电路为短路电路。

5、可选的,若干短路单元相连接的方式为:串联方式,前一短路单元的第一输入端与后一短路单元的第一输出端相连接。

6、可选的,前一短路单元的第一输入端与后一短路单元的第一输出端通过第一布线单元相连接,所述第一布线单元包括:与第一输入端相连接的第一布线层,与第一输出端相连接的第二布线层,电连接所述第一布线层和第二布线层的第三布线层,所述第一布线层和第二布线层与第一金属层平行,所述第三布线层与第一连接层平行。

7、可选的,所述第一布线单元还包括:与第一电源端相连接的第四电源端,以及与第一接地端相连接的第四接地端,所述第四电源端和第四接地端与第一金属层平行。

8、可选的,还包括:位于中间区上的第五电源端和第五接地端,所述第五电源端和第五接地端平行于第一方向;所述第一电源端通过第一布线单元与中间区的第五电源端相连接,所述第一接地端通过第一布线单元与中间区的第五接地端相连接。

9、可选的,所述边缘电路单元包括开路单元;所述金属结构包括:第二电源端、第二接地端和若干交替排列的第四金属层和第五金属层;所述开路单元还包括:位于第四金属层上和第二电源端上的第二插塞,位于第五金属层上和第二接地端上的第三插塞,位于第二插塞上的第二连接层,位于第三插塞上的第三连接层,所述第四金属层和第二连接层垂直,所述第五金属层和第三连接层垂直;所述第二连接层电连接第四金属层和第二电源端,所述第三连接层电连接第五金属层和第二接地端,所述第二接地端和第二电源端之间的电路为开路电路。

10、可选的,若干开路单元相连接的方式为:并联方式,若干开路单元的第二电源端相连接,若干开路单元的第二接地端相连接。

11、可选的,若干开路单元通过第二布线单元相连接,所述第二布线单元包括:与第二电源端相连接的第四布线层,与第二接地端相连接的第五布线层,电连接若干第四布线层的第六布线层,电连接若干第五布线层的第七布线层,所述第四布线层和第五布线层与第一金属层平行,所述第六布线层和第七布线层与第二连接层平行。

12、可选的,还包括:位于中间区上的第五电源端和第五接地端,所述第五电源端和第五接地端平行于第一方向;所述第二电源端通过第二布线单元与中间区的第五电源端相连接,所述第二接地端通过第二布线单元与中间区的第五接地端相连接。

13、可选的,还包括:若干填充单元,所述填充单元用于填充边缘区的空隙,所述填充单元包括:第三电源端和第三接地端,所述第三电源端和第三接地端与第一金属层平行,且所述第三电源端与第一电源端相连接,所述第三接地端与第一接地端相连接。

14、相应地,本发明技术方案还提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括中间区和位于中间区周围的边缘区;在中间区上形成若干层垂直堆叠的第一金属层和第二金属层,所述第一金属层平行于第一方向,所述第二金属层平行于第二方向,所述第一方向和第二方向平行于衬底表面,且所述第一方向和第二方向相互垂直;在边缘区上形成若干相连接的边缘电路单元,所述边缘电路单元包括短路单元或开路单元,所述边缘电路单元包括至少一层金属结构,所述金属结构与所述第一金属层平行,且所述金属结构的顶部表面与第一金属层的顶部表面齐平。

15、可选的,所述金属结构与第一金属层同时形成;若干所述边缘电路单元位于所述中间区沿第一方向两侧的边缘区上,若干所述边缘电路单元在边缘区上沿第二方向排列。

16、可选的,所述边缘电路单元包括短路单元;所述金属结构包括:第一输入端、第一输出端、第一电源端、第一接地端和若干第三金属层;所述短路单元还包括:位于第三金属层上、第一输入端上或第一输出端上的第一插塞,位于第一插塞上的第一连接层,所述第一连接层与第三金属层垂直;所述第一连接层电连接第一输入端、第一输出端和若干第三金属层,所述第一输入端和第一输出端之间的电路为短路电路。

17、可选的,若干短路单元相连接的方式为:串联方式,前一短路单元的第一输入端与后一短路单元的第一输出端相连接。

18、可选的,前一短路单元的第一输入端与后一短路单元的第一输出端通过第一布线单元相连接,所述第一布线单元包括:与第一输入端相连接的第一布线层,与第一输出端相连接的第二布线层,电连接所述第一布线层和第二布线层的第三布线层,所述第一布线层和第二布线层与第一金属层平行,所述第三布线层与第一连接层平行。

19、可选的,所述第一连接层与第二金属层同时形成。

20、可选的,所述边缘电路单元包括开路单元;所述金属结构包括:第二电源端、第二接地端和若干交替排列的第四金属层和第五金属层;所述开路单元还包括:位于第四金属层上和第二电源端上的第二插塞,位于第五金属层上和第二接地端上的第三插塞,位于第二插塞上的第二连接层,位于第三插塞上的第三连接层,所述第四金属层和第二连接层垂直,所述第五金属层和第三连接层垂直;所述第二连接层电连接第四金属层和第二电源端,所述第三连接层电连接第五金属层和第二接地端,所述第二接地端和第二电源端之间的电路为开路电路。

21、可选的,若干开路单元相连接的方式为:并联方式,若干开路单元的第二电源端相连接,若干开路单元的第二接地端相连接。

22、可选的,若干开路单元通过第二布线单元相连接,所述第二布线单元包括:与第二电源端相连接的第四布线层,与第二接地端相连接的第五布线层,电连接若干第四布线层的第六布线层,电连接若干第五布线层的第七布线层,所述第四布线层和第五布线层与第一金属层平行,所述第六布线层和第七布线层与第二连接层平行。

23、可选的,所述第二连接层和第三连接层与第二金属层同时形成。

24、可选的,还包括:形成若干填充单元,所述填充单元用于填充边缘区的空隙,所述填充单元包括:第三电源端和第三接地端,所述第三电源端和第三接地端与第一金属层平行。

25、相应地,本发明技术方案还提供一种边缘监测电路,包括:若干相连接的边缘电路单元。

26、可选的,所述边缘电路单元包括短路单元;若干短路单元相连接的方式为串联方式。

27、可选的,所述短路单元包括第一输入端和第一输出端,所述第一输入端和第一输出端之间的电路为短路电路;前一短路单元的第一输入端与后一短路单元的第一输出端连接。

28、可选的,所述边缘电路单元包括开路单元;若干开路单元相连接的方式为并联方式。

29、可选的,所述开路单元包括:第二电源端和第二接地端,所述第二接地端和第二电源端之间的电路为开路电路;若干开路单元的第二电源端连接,若干开路单元的第二接地端连接。

30、相应地,本发明技术方案还提供一种边缘监测电路的工作方法,包括:提供边缘监测电路,所述边缘监测电路包括:若干相连接的边缘电路单元;对边缘监测电路通电后,判断边缘监测电路是否处于短路或开路的状态;根据边缘监测电路的状态,判断所述边缘监测电路是否正常,若边缘监测电路非正常,则对边缘监测电路进行检修。

31、可选的,所述边缘电路单元包括短路单元;根据边缘监测电路的状态,判断所述边缘监测电路是否正常的方法包括:若所述边缘监测电路处于短路状态,则所述边缘监测电路正常;若所述边缘监测电路处于开路状态,则所述边缘监测电路非正常,需要对边缘监测电路进行检修。

32、可选的,所述边缘电路单元包括开路单元;根据边缘监测电路的状态,判断所述边缘监测电路是否正常的方法包括:若所述边缘监测电路处于开路状态,则所述边缘监测电路正常;若所述边缘监测电路处于短路状态,则所述边缘监测电路非正常,需要对边缘监测电路进行检修。

33、相应地,本发明技术方案还提供一种半导体版图设计方法,包括:版图,所述版图包括中间区和位于中间区周围的边缘区;提供边缘电路单元;在边缘区设置若干相连接的边缘电路单元。

34、可选的,所述边缘电路单元包括短路单元;若干短路单元相连接的方式为串联方式。

35、可选的,所述边缘电路单元包括开路单元;包括开路单元相连接的方式为并联方式。

36、与现有技术相比,本发明的技术方案具有以下有益效果:

37、本发明的技术方案的半导体结构,在边缘区上设置若干相连接的边缘电路单元。由于边缘电路单元的结构是已知的,可以很好的实现芯片边缘处的环境,利于研究边缘的缺陷,同时,芯片边缘的电路也可以利用起来,提升芯片面积利用率;此外,边缘电路单元的结构是重复的,因此在芯片边缘的布局布线方便,能够用较少的设计规则进行约束,即能实现对边缘结构可扫描可测试的电路;边缘电路单元的结构简单,因此适用性强,只要符合标准数字单元架构的都可以采用这种电路测量后端工艺,适用成熟工艺和先进工艺各个节点。

38、进一步,若干所述边缘电路单元通过第一布线单元或第二布线单元相连接。布线单元与边缘电路单元分开,芯片边缘结构的环境可以较好的再现,不会受到测试线路的干扰和影响。

39、进一步,第一电源端通过第一布线单元与中间区的第五电源端相连接,第一接地端通过第一布线单元与中间区的第五接地端相连接;第二电源端通过第二布线单元与中间区的第五电源端相连接,第二接地端通过第二布线单元与中间区的第五接地端相连接。从而芯片中间区等非边缘区域也可以进行扫描研究,从而不浪费芯片面积。

40、本发明的技术方案的边缘监测电路的工作方法,判断所述边缘监测电路是否正常,若边缘监测电路非正常,则对边缘监测电路进行检修。若边缘监测电路正常,则对边缘监测电路进行利用。

- 还没有人留言评论。精彩留言会获得点赞!