标准元件单元的制作方法

1.本发明是有关于一种建构于半导体单晶粒(monolithic semiconductor die)中的半导体元件,特别是有关于一种通过集成电路微缩和拉伸(scaling and stretching)平台,在半导体单晶粒中所构建的优化标准元件单元。其可以有效地微缩建构在半导体单晶粒中的逻辑电路的尺寸,而不会微缩最小特征尺寸。

背景技术:

2.集成电路的性能和成本的改进,主要是经由根据摩尔定律的制程微缩技术来实现的,但是随着晶体管的尺寸微缩到28奈米(或更小),其制程变异就变成一种挑战。特别是,经由微缩逻辑电路的尺寸来提高储存密度、经由降低操作电压(vdd)来降低待机功耗以及经由提高良率来得到更大容量的逻辑电路,都变得越来越难以实现。

3.标准元件是逻辑电路中常用的基本元件之一。标准元件单元通常包括多个如图1(a)至图1(f)所绘示的基本逻辑功能单元(例如,反相器单元(inverter cell)、nor单元(nor cell,或非单元)和nand单元(nand cell,与非单元)、反相器单元

×

2、nor单元

×

2和nand单元

×

2)。然而,由于接触结构的尺寸和金属线布局之间的干扰,即使将制程尺寸(所谓的「最小特征尺寸」、「λ」或「f」)微缩至22nm或更小,当最小特征尺寸微缩时,的标准元件单元的总面积,以λ2或f2表示,仍会显著增加。

4.当最小特征尺寸减小时,以λ2或f2所表示的标准元件单元的总面积会显著增加的原因可以描述如下。传统标准元件单元,以图1(a)所示的反相器为例,通过多层内连线连接。其中,第一内连线金属层m1连接至晶体管的(源极区和漏极区)的扩散层(diffusion level)。有需要增加第二内连线金属层m2和/或第三内连线金属层m3以促进信号传输(例如,输入input或输出output)。可以只使用第一内连线金属层m1,之后形成由某些类型的导电材料所组成的插塞结构via-1,来连接第二内连线金属层m2和第一内连线金属层m1,而不扩大晶粒尺寸。因此,就产生了由扩散区diffusion通过接触结构(con)连接到第一内连线金属层m1形成的垂直连接结构,即「diffusion-con-m1」结构。类似地,也形成另一种,经由接触结构(con)将栅极(gate)连接到第一内连线金属层m1的连接结构,即「gate-con-m1」结构。

5.另外,如果需要,亦可形成连接结构「m1-via1-m2」,经由插塞结构via1从第一内连线金属层m1连接到第二内连线金属层m2。从栅极层gate-level到第二内连线金属层m2之间更复杂的内连线结构可以描述为「gate-con-m1-via1-m2」。此外,堆迭的内连线系统还可以具有「m1-via1-m2-via2-m3」或「m1-via1-m2-via2-m3-via3-m4」等结构。由于两个存取晶体管(如图1(a)所绘示的两个nmos导通-闸晶体管pg-1和pg-2)中的栅极(gate)和扩散区(diffusion)必须连接到设置在第二内连线金属层m2中的输入端input。而在传统反相器中这种金属内连线结构必须先穿过第一内连线金属层m1。也就是说,反相器中最先进的内连线系统,可能不允许栅极(gate)或扩散区(diffusion)在不经过第一内连线金属层m1的情况下,直接连接到第二内连线金属层m2。结果,一个与第一内连线金属层m1连接的内连线结

构和另一个与第一内连线金属层m1连接的内连线结构之间必须保留空间,而这将会增加晶粒的尺寸,并且在某些情况下,而且这种内连线结构的布线方式,可能会阻碍直接形成有效通道,穿过第一内连线金属层m1连接至第二内连线金属层m2的意图。此外,也难以在插塞via1与接触结构contact之间形成自对准结构,其中插塞via1与接触结构contact彼此分别连接到各自的内连线系统。

6.此外,在传统标准元件单元(如图1(a)所绘示的反相器的)中,至少会有一个nmos晶体管11和一个pmos晶体管12分别位于p型基材(p-substrate)的一些邻接区域(例如,n型井区(n-well)或p型井区(p-well))之中。而这些区域已经形成在一个彼此相邻的紧密邻接区域内,进而形成n+/p/n/p+寄生双极元件的寄生接面结构(parasitic junction structure)。其轮廓从nmos晶体管11的n+掺杂区开始,到p型井区(p-well)到相邻的n型井区(n-well),再到pmos晶体管12的p+掺杂区,如图2所绘示。由于n+/p接面或p+/n接面都会产生现明显的噪声,当异常大的电流异常流过此n+/p/n/p+接面时,可能会关闭互补式金属-氧化物半导体(complementary metal-oxide-semiconductor,cmos)电路的某些操作,并导致整个芯片(chip)故障。这种被称为闩锁(latch-up)的异常现象对互补式金属-氧化物半导体电路的操作是有害的,必须避免。

7.增加对闩锁的抵抗力的其中一种方法,是增加从n+掺杂区到p+掺杂区的距离。但这对于互补式金属-氧化物半导体电路来说无疑是一个弱点。因为,增加从n+掺杂区到p+掺杂区的距离以避免闩锁问题,会实质上扩大标准元件单元的尺寸。

8.第3(a)图系绘示一家半导体公司(三星)的5nm(uhd)标准元件单元中pmos和nmos晶体管的布局连线棒状图(stick diagram)。此状棒图只绘示出包括主动区(水平的红色粗线)和栅极线(垂直的蓝色粗线)。在本文中,主动区可以被称为「鳍片(fin)」。当然,仍有许多接触结构,其一端直接耦合到pmos和nmos晶体管,另一端耦合到输入端、输出端、高压源vdd端和低压源vss(或接地gnd)等,未被绘示出来。特别是,每个晶体管包括两个主动区或鳍片(用深红色粗线标记)以形成晶体管的通道,使得w/l比(w/l ratio)可以保持在可接受的范围内。反相器单元的面积大小等于x

×

y,其中x=2

×

cpp,y=cell_height,cpp为接触结构到栅极之间的间隔(contact to poly pitch)距离。需要注意的是,标准元件单元的pmos/nmos晶体管中含有一些未被使用的主动区或鳍片(用浅红色标记,称为「虚拟鳍片(dummy fins)」),其存在的原因与解决pmos晶体管和nmos晶体管之间的闩锁问题有关。第3(a)图中pmos晶体管和nmos晶体管之间的闩锁距离为3

×

fp-λ(例如,=14λ),其中fp是鳍片的间距(例如,=5λ)。

9.根据三星5nm(uhd)标准元件单元中的可用数据:cpp(为54nm)和cell_height(为216nm),可以通过x

×

y计算标准元件单元的面积等于23328nm2(或933.12λ2,其中λ(lambda)为最小特征尺寸为5nm)。图3(b)说明三星5nm(uhd)标准元件单元及其尺寸。如图3(b)所绘示,pmos晶体管和nmos晶体管之间的闩锁距离约为15λ,cpp为10.8λ,单元高度cell_height为43.2λ。

10.此外,根据目前已公开的相关信息,不同的制程技术节点(process technology node)(或最小特征尺寸)的cpp和cell_height标示如下表:

11.tsmc(台积电)571016cpp(nm)50576690

cell_height(nm)180240360576

[0012][0013][0014]

intel(英特尔)10142222cpp(nm)547090108cell_height(nm)272399840540

[0015]

使用上表,上述三个厂商关于面积尺寸(2

×

cpp

×

cell_height)与不同制程技术节点的微缩趋势,可以在图4中显示出来。随着制程技术节点的微缩(例如从22nm微缩到5nm),传统标准元件单元的面积(2

×

cpp

×

cell_height),以λ2为单位,会急剧增加。在传统标准元件单元中,制程技术节点越小,以λ2表示的单元面积则越大。传统标准元件单元的面积之所以显著增加的原因,可能是由于栅极接触结构/源极接触结构/栅极接触结构的尺寸,难以随着λ的微缩而按比例缩小、pmos晶体管和nmos晶体管之间的闩锁距离,难以随着λ的微缩而按比例缩小;以及金属层中的干扰,难以随着λ的微缩而按比例缩小。

[0016]

因此,有需要提供一种先进的标准元件单元,以解决该技术领域所面临的上述问题。

技术实现要素:

[0017]

本说明书的一实施例是提供一种标准元件单元(standard cell),此标准元件单元包括多个晶体管、一组接触结构、至少一条输入线、至少一条输出线、高压vdd接触线以及低压vss接触线。此组(多个)接触结构电性连接至多个晶体管。输入线电性连接至多个晶体管。输出线电性连接至多个晶体管。高压vdd接触线电性连接至多个晶体管。低压vss接触线电性连接至多个晶体管。其中,随着标准元件单元的最小特征尺寸(λ)在不同的制程技术节点逐步微缩(例如从22nm逐步微缩),由最小特征尺寸的平方表示之该标准元件单元的面积尺寸仍维持相同或基本相同。

[0018]

根据本说明书的一个面向,标准元件单元可以是(但不限定为)反相器单元、nand单元或nor单元。

[0019]

根据本说明书的一个面向,标准元件单元更包括金属接触线,电性连接至此组接触结构中的第一接触结构;其中第一接触结构未被金属接触线完全覆盖。

[0020]

根据本说明书的一个面向,金属接触线与第一接触结构具有相同或基本相同的宽度。

[0021]

根据本说明书的一个面向,标准元件单元,更包括重掺杂硅插塞,形成于第一接触结构未被金属接触线覆盖的一部分上,其中重掺杂硅插塞与金属接触线接触。

[0022]

根据本说明书的一个面向,标准元件单元更包括电性连接至多个晶体管的第一金属线和第二金属线。其中,第二金属线位于第一金属线上方;此组接触结构中的至少一者直

接连接至第二金属线,而不通过第一金属。

[0023]

根据本说明书的一个面向,此组接触结构中的至少一者是一种栅极接触结构。

[0024]

本说明书的一实施例是提供一种标准元件单元,此标准元件单元包括半导体基材、多个晶体管、一组接触结构、第一金属线以及第二金属线。半导体基材具有一个原始表面。此组(多个)接触结构、第一金属线和第二金属线都电性连接至多个晶体管。其中,多个晶体管形成于半导体基材上,多个晶体管中的至少一者,包括通道层和导电区。通道层或导电区独立于半导体基材之外,且不会被离子注入制程所掺杂。

[0025]

根据本说明书的一个面向,多个晶体管至少一者包括一个鳍片结构;通道层包括覆盖鳍片结构的第一侧壁和第二侧壁,并未覆盖鳍片结构的顶面。

[0026]

根据本说明书的一个面向,多个晶体管至少一者包括一个鳍片结构;通道层包括一个覆盖鳍片结构顶面的顶部和一个覆盖该鳍片结构的第一侧壁和第二侧壁的侧部,且顶部和侧部不是同时形成的。

[0027]

根据本说明书的一个面向,导电区是从半导体基材的侧边经由选择性生长制程所形成。

[0028]

根据本说明书的一个面向,标准元件单元,更包括一个沟槽及一个隔离区。沟槽形成于半导体基材的原始表面下方。隔离区位于沟槽之中。其中,导电区设置于沟槽之中,且导电区的底面经由隔离区与半导体基材隔离。

[0029]

根据本说明书的一个面向,导电区只有一边与该半导体基材接触。

[0030]

根据本说明书的一个面向,标准元件单元更包括一个金属区,与导电区接触,其中金属区位于沟槽之中,且金属区的底面经由隔离区与半导体基材隔离。

[0031]

本说明书的又再一实施例是提供一种标准元件单元,此标准元件单元包括具有井区的基材、多个晶体管、多个接触结构、至少一条输入线、一条输出线、高压vdd接触线以及低压vss接触线。多个晶体管包括第一类型晶体管和第二类型晶体管,其中第一类型晶体管形成于井区之中,且第二类型晶体管形成在井区之外。多个接触结构电性连接至多个晶体管。至少一条输入线电电性连接至多个晶体管。输出线电性连接至多个晶体管。高压vdd接触线电性连接至多个晶体管。低压vss接触线电性连接至多个晶体管。第一类型晶体管包括彼此电性连接的第一组鳍片结构,第二类型晶体管包括彼此电性连接的第二组鳍片结构,且第一类型晶体管和第二类型晶体管之间的间隙(gap)等于或基本等于3

×

fp-fp,其中fp为第一类型晶体管中相邻两个鳍片结构之间的间距(pitch),fw为该鳍片结构的一鳍片宽度;第一类型晶体管中相邻的两个鳍片结构之间的间距介于3λ至5λ之间,例如3λ,λ为一最小特征尺寸。

[0032]

根据本说明书的一个面向,第一类型晶体管和第二类型晶体管之间的间隙介于8λ至12λ之间,例如实质上等于8λ。

[0033]

本说明书的再另一实施例是提供一种标准元件单元,此标准元件单元包括一组接触结构、第一金属线和第二金属线。第一金属线和第二金属线电性连接至多个晶体管。其中,第二金属线位于第一金属线上方;此组(多个)接触结构中的至少一者直接连接至第二金属线,而不通过第一金属。

[0034]

根据本说明书的一个面向,此组(多个)接触结构中的至少一者是一种栅极接触结构。

附图说明

[0035]

为了对本说明书之上述及其他方面有更佳的了解,下文特举实施例,并配合所附图式详细说明如下:

[0036]

图1(a)至图1(f)系分别绘示习知的基本逻辑功能单元,包括反相器单元、nor单元和nand单元的等效电路图。

[0037]

图2系绘示传统标准元件单元中的nmos晶体管和pmos晶体管的结构剖面图。

[0038]

第3(a)图系绘示一家半导体公司(三星)的5nm(uhd)标准元件单元中pmos晶体管和nmos晶体管的布局连线棒状图。

[0039]

图3(b)系绘示第3(a)图中三星5nm(uhd)标准元件单元各项尺寸的棒状图。

[0040]

图4系绘示三个厂商关于面积尺寸(2

×

cpp

×

cell_height)与不同制程技术节点的微缩趋势图。

[0041]

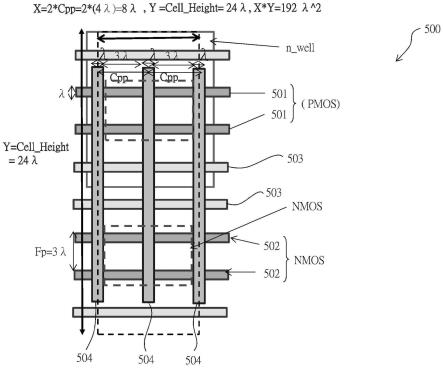

图5(a)系根据本发明的一实施例绘示一种新型反相器标准单元的布局样式的棒状图。

[0042]

图5(b)系绘示图5(a)中新型反相器标准单元各项尺寸的棒状图。

[0043]

图5(c)至图5(f)系绘示形成图5(a)和图5(b)之反相器标准单元的一系列制程布局图。

[0044]

图6(a)系根据本发明的一实施例绘示一种新型标准元件单元中所使用的微缩化金属-氧化物-半导体场效应晶体管(miniaturized metal-oxide-semiconductor field-effect transistor,mmosfet)的结构俯视图。

[0045]

图6(b)系绘示位于基材上方的垫氧化硅(pad-oxide)层和垫氮化硅(pad-nitride)层,以及形成在基材中的第一浅沟隔离-硅氧化物层的结构剖面图。

[0046]

图6(c)系绘示在主动区上方形成真实栅极(true gate,tg)和虚拟遮蔽栅极(dummy shield gate,dsg)之后的结构剖面图。

[0047]

图6(d)系绘示在形成旋涂电介电材料(spin-on dielectrics,sod)以及沉积并蚀刻栅极掩膜层之后的结构剖面图。

[0048]

图6(e)系绘示在移除位于虚拟遮蔽栅极上方的氮化硅层、虚拟遮蔽栅极、对应于虚拟遮蔽栅极的一部分介电绝缘材料以及对应于虚拟遮蔽栅极的p型基材之后的结构剖面图。

[0049]

图6(f)系绘示移除栅极掩膜层、蚀刻旋涂电介电材料以及沉积第二硅氧化物层以形成第二浅沟隔离-硅氧化物层之后的结构剖面图。

[0050]

图6(g)系绘示沉积并蚀刻第三硅氧化物层以形成第三硅氧化物间隙壁(spacer),在p型基材中形成轻掺杂漏极(lightly doped drains,ldd),沉积并回蚀氮化硅层以形成氮化硅间隙壁,并移除介电绝缘材料之后的结构剖面图。

[0051]

图6(h)系绘示经由选择性磊晶生长(selective epitaxy growth,seg)技术生长本征硅质电极(intrinsic silicon electrode)之后的结构剖面图。

[0052]

图6(i)系绘示沉积并回蚀cvd-第三浅沟隔离-硅氧化物层层、移除本征硅电极,并且形成微缩化-金属-氧化物半导体场效应晶体管的源极(n+源极)和漏极(n+漏极)之后的结构剖面图。

[0053]

图6(j)系绘示沉积并蚀刻硅氧化物间隙壁以形成接触开口之后的结构剖面图。

[0054]

图6(k)系绘示沉积一层旋涂电介电材料以填充基材上的空隙(vacancies),并使用化学机械研磨(cmp)进行平坦化之后的结构剖面图。

[0055]

图6(l)系根据图6(k)所绘示的结构上视图。

[0056]

图6(m)系绘示在图6(l)的结构上形成光阻层之后的结构上视图。

[0057]

图6(n)系绘示以非等向性蚀刻(anisotropic etching)技术移除位于暴露于外的栅极延伸区内的氮化硅覆盖层,以露出导电金属栅极层之后的结构上视图。

[0058]

图6(o)系绘示移除光阻层和旋涂电介电材料层,藉以在源极区和漏极区的顶部形成开口,以及形成间隙壁间之后的结构剖面图。

[0059]

图6(p)系根据图6(o)所绘示的结构上视图。

[0060]

图6(q)系绘示形成第一金属(metal-1,m1)内连线层之后的结构剖面图。

[0061]

图6(r)系根据图6(q)所绘示的结构上视图。其中栅极通过第一金属内连线层连接到源极区。

[0062]

图7(a)系根据说明书的另一实施例,绘示一种用于新型标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管的结构上视图。

[0063]

图7(b)和图7(c)系沿着图7(a)中的切线c7a1和c7a2所分别绘示的两个构成晶体管的结构剖面图。

[0064]

图7(d)系根据说明书的一实施例,绘示在第一导体柱部分和第三导体柱部分上方分别形成第二导体柱部分和第四导体柱部分之后的结构的俯视图。

[0065]

图7(e)系沿着图7(d)中的切线c7d1所绘示的结构剖面图。

[0066]

图7(f)系沿着图7(d)中的切线c7d2所绘示的结构剖面图。

[0067]

图7(g)系根据说明书的一实施例,绘示在第一介电层上方形成于第一导电层与第二介电子层之后的结构俯视图。

[0068]

图7(h)系沿着图7(g)中的切线c7g1所绘示的结构剖面图。

[0069]

图7(i)系沿着图7(g)中的切线c7g2所绘示的结构剖面图。

[0070]

图7(j)系根据说明书的一实施例,绘示在上方介电层(upper dielectric layer)上形成上方导电层之后的结构俯视图。

[0071]

图7(k)系沿着图7(j)中的切线c7j1所绘示的结构剖面图。

[0072]

图7(l)系沿着图7(j)中的切线c7j2所绘示的结构剖面图。

[0073]

图8(a)系根据说明书的又一实施例,绘示一种用于新型标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管的结构上视图。

[0074]

图8(b)系沿着图8(a)中的切线c8a1所绘示的结构剖面图。

[0075]

图8(c)系沿着图8(a)中的切线c8a2所绘示的结构剖面图。

[0076]

图8(d)系根据说明书的再一实施例,绘示一种用于新型标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管的结构上视图。

[0077]

图8(e)系沿着图8(d)中的切线c8d1所绘示的结构剖面图。

[0078]

图8(f)系沿着图8(d)中的切线c8d2所绘示的结构剖面图。

[0079]

图9系根据说明书的又再一实施例,绘示一种用于新型标准元件单元中的nmos晶体管的结构剖面图。

[0080]

图10(a)系根据说明书的更再一实施例,绘示一种用于新型标准元件单元中的

nmos晶体管和pmos晶体管的组合结构剖面图。

[0081]

图10(b)是沿图10(a)中的切线(x轴)所绘示的nmos晶体管和pmos晶体管的结构剖面图。

[0082]

图10(c)是沿图10(a)中的切线(y轴)所绘示的nmos晶体管和pmos晶体管的结构剖面图。

[0083]

图11系绘示本发明所提供的新型标准元件单元之面积尺寸与其他各公司所提供之现有产品的面积尺寸比较结果。

[0084]

图12(a)至图12(c)是根据本说明书的一些实施例,绘示一种具有单一nor单元、单一nand单元和反相器单元

×

2的标准元件单元的结构俯视图和对应的等效电路图。

[0085]

图12(d)至图12(e)是根据本说明书的一些实施例,绘示一种具有nor单元

×

2和nand单元

×

2的标准元件单元的结构俯视图和对应的等效电路图。

[0086]

附图标记说明

[0087]

active area:主动区

[0088]

m1:第一内连线金属层

[0089]

m2:第二内连线金属层

[0090]

via1:第一插塞

[0091]

poly:多晶硅线

[0092]

input:输入

[0093]

output:输出

[0094]

gnd:接地

[0095]

vdd:高压源

[0096]

vss:低压源

[0097]

fw:鳍片宽度

[0098]

fp:鳍片间距

[0099]

sti:浅沟隔离层

[0100]

p+:p+掺杂区

[0101]

n+:n+掺杂区

[0102]

n_well:n型井区

[0103]

p_well:p型井区

[0104]

ldd:轻掺杂漏极

[0105]

aa_ct:源极/漏极接触结构

[0106]

gate_ct:栅极接触结构

[0107]

cpp:接触结构到栅极之间的间隔

[0108]

cell_height:单元高度

[0109]

c-d(l):开口长度

[0110]

c-d(w):开口宽度

[0111]

c-s(l):开口长度

[0112]

c-s(w):开口宽度

[0113]

d(l):漏极长度

[0114]

d(w):漏极宽度

[0115]

g(l):栅极长度

[0116]

g(w):栅极宽度

[0117]

s(l):源极长度

[0118]

s(w):源极宽度

[0119]

groc(l):间距

[0120]

crmg(l):垂直长度

[0121]

hss:基材的原始水平表面

[0122]

tg:实栅极

[0123]

dsg:拟遮蔽栅极

[0124]

tec:凹陷厚度

[0125]

xp:保留边缘距离

[0126]

xn:保留边缘距离

[0127]

11:nmos晶体管

[0128]

12:pmos晶体管

[0129]

33:栅极结构

[0130]

34:复合物间隙壁

[0131]

48:局部隔离结构

[0132]

49:浅沟隔离结构

[0133]

51:nmos晶体管

[0134]

52:pmos晶体管

[0135]

55:源极区

[0136]

56:漏极区

[0137]

331:栅极介电层

[0138]

332:栅极导电层

[0139]

333:介电覆盖层

[0140]

341:氧化物层

[0141]

342:氮化硅层

[0142]

491:第一浅沟隔离层

[0143]

492:第二浅沟隔离层

[0144]

481:第三硅氧化物侧壁层

[0145]

482:第三硅氧化物底壁层

[0146]

483:第三氮化硅层

[0147]

491:第一浅沟隔离层

[0148]

492:第二浅沟隔离层

[0149]

500:反相器标准单元

[0150]

501:鳍片

[0151]

502:鳍片

[0152]

503:鳍片

[0153]

504:栅极线

[0154]

505:源极/漏极接触结构

[0155]

506:栅极接触结构

[0156]

507:第一内连线金属层

[0157]

508:第一插塞

[0158]

509:第二内连线金属层

[0159]

551:轻掺杂漏极

[0160]

552:p+重掺杂区

[0161]

553:插塞

[0162]

600:微缩化-金属-氧化物半导体场效应晶体管

[0163]

601:p型基材

[0164]

602:垫氧化硅层

[0165]

604:垫氮化硅层

[0166]

605:隔离区

[0167]

606:第一浅沟隔离-硅氧化物层

[0168]

607:漏极

[0169]

609:接触孔

[0170]

610:栅极层

[0171]

611:接触孔

[0172]

612:介电绝缘体

[0173]

614:氮化硅层

[0174]

700:微缩化-金属-氧化物半导体场效应晶体管

[0175]

701:半导体基材

[0176]

702:栅极端子

[0177]

702a:栅极介电层

[0178]

702b:栅极导电层

[0179]

702c:硅质区

[0180]

702d:覆盖层

[0181]

702sl:氮化硅间隙壁

[0182]

702s2:热氧化硅间隙壁

[0183]

703:晶体管通道区

[0184]

704:源极/漏极区

[0185]

705:浅沟隔离结构

[0186]

707a:开孔

[0187]

707b:开孔

[0188]

709:开口

[0189]

712:旋涂电介电材料

[0190]

720:第一介电层

[0191]

730a:第一导体柱

[0192]

730b:第二导体柱

[0193]

730t:第一导体柱和第二导体柱的顶面

[0194]

731a:第一导体柱部分

[0195]

731b:第三导体柱部分

[0196]

732a:第二导体柱部分

[0197]

732b:第四导体柱部分

[0198]

740:第一介电子层

[0199]

740s:第一介电子层的顶表面

[0200]

750:第一导电层

[0201]

760:第二介电子层

[0202]

770:上层介电层

[0203]

770s:上层介电层的顶面

[0204]

780:上方导电层

[0205]

802:栅极掩膜层

[0206]

810a:高掺杂的硅质柱状体

[0207]

810b:高掺杂的硅质柱状体

[0208]

820:侧柱

[0209]

830a:金属柱部分

[0210]

830b:金属柱部分

[0211]

830w:钨质柱状体

[0212]

830n:氮化钛层

[0213]

850:第一导电层

[0214]

850a:第一金属子层

[0215]

850b:第二金属子层

[0216]

840:第一介电子层

[0217]

1002:第二浅沟隔离-硅氧化物层

[0218]

1502:第三硅氧化物间隙壁

[0219]

1504:轻掺杂漏极

[0220]

1506:氮化硅间隙壁

[0221]

1602:本征硅质电极

[0222]

1704:源极区

[0223]

1706:漏极区

[0224]

1802:硅氧化物间隙壁

[0225]

1804:开口

[0226]

1901:旋涂电介电材料

[0227]

1902:光阻层

[0228]

1903:栅极延伸区

[0229]

1901:旋涂电介电材料

[0230]

1902:光阻层

[0231]

1904:硅氧化物

具体实施方式

[0232]

在传统的标准元件单元中,即使最小特征尺寸或制程技术节点微缩至28奈米或更小,晶体管的尺寸也没办法按比例缩小。本发明公开了一种在单芯片半导体晶粒(monolithic semiconductor die)中,具有紧凑布局样式的新型的标准元件单元。经由采用新布局样式,可以使标准元件单元的面积尺寸,相对于制程技术节点的微缩,仍保持一致或不太敏感,且不会扩大闩锁问题。

[0233]

图5(a)系根据本发明的一实施例绘示一种新型反相器标准单元500的布局样式的棒状图。图5(b)系绘示图5(a)中新型反相器标准单元500各项尺寸的棒状图。为了清楚简明地描述元件结构,仅描绘了反相器标准单元500的栅极层(gate-level)和扩散层(diffusion level)。

[0234]

其中,反相器标准单元500包括nmos晶体管和pmos晶体管,其中pmos晶体管具有第一鳍片结构和覆盖鳍片结构的栅极,第一鳍片结构系由形成在半导体基材(未绘示)的n型井区n_well的二个鳍片(它们二者之间的间距fp为3λ)所组成。nmos晶体管具有第二鳍片结构和覆盖鳍片结构的栅极,第二鳍片结构系由形成在半导体基材(未绘示)的p型井区p_well的二个鳍片(它们二者之间的间距fp为3λ)所组成。nmos晶体管与pmos晶体管nmos以大于鳍片间距(fin pitch)的间隙隔开,并且在nmos晶体管和pmos晶体管之间设置有两个虚拟鳍片(dummy fins)。

[0235]

反相器标准单元500的面积尺寸可实现紧凑设计。随着反相器标准单元500的最小特征尺寸(λ),针对不同的制程技术节点逐渐微缩(例如,从22nm微缩到16nm,或从22nm微缩到5nm),以λ2表示的反相器标准单元500的面积尺寸仍保持相同或基本相同。在本实施例中,主动区或鳍片的宽度为λ,栅极线(或多晶硅线poly)的宽度为λ,cpp为4λ,cell_height为24λ,反相器标准单元500的单元面积(2

×

cpp

×

cell_height,如图示中黑色虚线矩形所标示的面积)为192λ2。

[0236]

图5(c)至图5(f)系绘示形成图5(a)和图5(b)所绘示之反相器标准单元500的一系列制程布局图。如图5(a)所绘示,在半导体基材(未绘示)上形成有多组鳍片结构(例如多个水平鳍),其中形成在半导体基材之n型井区n_well中的两个相邻鳍片501用来作为pmos晶体管的主动区;形成在半导体基材中并与pmos晶体管相邻的两个相邻鳍片502用来作为nmos晶体管的主动区。形成在半导体基材中,且位于nmos晶体管和pmos晶体管之间的两个相邻鳍片503可以作为两个虚拟鳍片。如图5(c)所绘示,pmos晶体管与nmos晶体管之间的间隙等于或大致等于3

×

fp-fw,其中fp为图5(a)所绘示,相邻两个鳍结构之间的鳍片间距(例如,fp=3λ);fw为鳍片结构的鳍片宽度。在本实施例中,鳍片宽fw被设置为λ(最小特征尺寸)。因此,pmos晶体管和pmos晶体管之间的间隙等于或基本等于3

×

fp-λ(例如,间隙=8λ)。

[0237]

此外,多条栅极线504(或多晶硅栅极线(poly-lines))形成在半导体基材上,并且横跨在pmos晶体管和pmos晶体管的鳍片结构以及虚拟鳍上方。在本实施例中,两条栅极线或多晶硅栅极线之间的间隙(如图5(a)所绘示的cpp)可以微缩至4λ。在图5(c)中,有多个源极/漏极接触结构aa_ct 505(形成于掩膜层开口中,用于连接源/漏极主动区至第一内连线

金属层m1的插塞(via))和栅极接触结构gate_ct 506(用于连接多晶硅栅极线至第二内连线金属层m2的插塞(via)开口掩膜层)形成。在图5(d)中,形成多个第一内连线金属层507(宽度:λ或更大),用以连接多个源极/漏极接触结构aa_ct 505(aa_ct掩膜),但栅极接触结构(gate_c)506不与第一内连线金属层507连接。在图5(e)中,在第一内连线金属层507的顶部形成多个用于将第一内连线金属层507连接到第二内连线金属层m2的第一插塞(via1)508。在图5(f)中,形成多个第二内连线金属层509以将多个第一插塞(via1)508分别连接到高压源vdd、输出端和低压源vss;其中,形成一个额外的第二内连线金属层m2 510,用以将栅极接触结构(gate_c)506直接连接到输入端。

[0238]

传统标准元件单元可能不允许栅极或源极/漏极,在不经过第一内连线金属层m1的前提下,直接连接到第二内连线金属层m2。本发明公开了一种新的标准元件单元,其中栅极/源极/汲可以通过一个垂直的导电插塞,以自对准方式,直接连接到第二内连线金属层m2,而无需以第一内连线金属层m1作为过渡层,如下:

[0239]

图5(c)至图5(f)中,缩写符号的含义如下:

[0240][0241]

此外,通过精确控制新的反相器标准单元500中的pmos晶体管和nmos晶体管的源极、漏极和栅极的线性尺寸,可以轻易地实现反相器标准单元500的尺寸。且无论当前可用制程技术节点的尺寸(或最小特征尺寸)如何,线性维度都可以微缩到最小特征尺寸lambda(λ)。

[0242]

在传统的标准元件单元中,即使制程技术的微缩化已降至28nm(所谓的「最小特征尺寸」、「λ」或「f」)或更低,标准元件单元中所使用的微缩化金属-氧化物-半导体场效应晶体管(mmosfet)的尺寸无法按比例减少。然而,在本实施例中,当两个相邻的晶体管(例如,图5(a)中的pmos晶体管和nmos晶体管)通过漏极/源极连接在一起时,两相邻晶体管的栅极边缘之间的距离(即闩锁距离)可以微缩至8λ。另外,源极、漏极和栅极的接触孔的线性尺寸可以小于λ,例如0.6λ至0.8λ,可以在漏极区域内实现(同样也能在源极区域和栅极区域内实现)。

[0243]

如图5(b)所述,pmos晶体管和nmos晶体管中的每一者都包括多个主动区以保持合理的w/l比。可以在主动区中形成漏极/源极接触结构aa_ct(用于连接至第一内连线金属层m1)。本发明是利用形成在栅极层掩膜gate-level mask上的临时虚拟遮蔽栅极,经由避使用免微影错位容差(photolithographic misalignment tolerances,mtp)的方式,使从栅极至源极区和隔离区之间的边界边缘(gate edge to the boundary edge between the source region and the isolation region,gebesi)的距离更加明显。

[0244]

图6(a)系根据说明书的一实施例,绘示一种用于新型标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管600的结构上视图。如图6(a)所绘示。微缩化-金属-氧化物半导体场效应晶体管600包括:(1)栅极结构610,具有栅极长度g(l)和栅极宽度g(w),(2)位于栅极结构610左侧的源极603,具有从栅极结构610的边缘到隔离区605边缘的源极长度s(l)(其为线性尺寸)以及源极宽度s(w),(3)位于栅极结构610右侧的漏极607,具有从栅极结构610的边缘到隔离区605边缘的漏极长度d(l)(其为线性尺寸)以及漏极宽度d(w),(4)位于源极603的中心处,经由自对准技术所形成的接触孔609,其具有分别被标记为c-s(l)和c-s(w)的开口长度和开口宽度,以及(5)同样位于漏极607中心处,经由自对准技术所形成的接触孔611,其具有分别被标记为c-d(l)和c-d(w)的开口长度和开口宽度。其中栅极长度g(l)、漏极长度d(l)和源极长度s(l)可以精确控制到最小特征尺寸λ。此外,被标记为c-s(l)和c-s(w)的开口长度和开口宽度可以小于λ,例如介于0.6λ至0.8λ之间。

[0245]

下面简要描述用于制作本发明的标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管600的制造过程。微缩化-金属-氧化物半导体场效应晶体管600的结构及其制程的详细描述,可见于2020年12月31日提交的美国专利申请案,编号17/138,918,名称为:「miniaturized transistor structure with controlled dimensions of source/drain and contact-opening and related manufacture method」。且此编号为17/138,918的美国专利申请案,其全部内容通过引用并入的方式全文收载于本说明书之中。

[0246]

如图6(b)所绘示,形成垫氧化硅层602,并且在基材601上沉积垫氮化硅层604。微缩化-金属-氧化物半导体场效应晶体管600的主动区系经由移除主动区外部的一部分硅质材料来定义以产生沟槽结构来加以定义。第一硅氧化物层被沉积在沟槽结构中并被回蚀以在硅质基材的原始水平表面(horizontal surface of the silicon substrate,hss)下方形成第一浅沟隔离-硅氧化物层606。

[0247]

移除垫氧化硅层602和垫氮化硅层604,并在硅质基材的原始水平表面hss上方形成介电绝缘体612。然后,在硅质基材的原始水平表面hss上方沉积栅极层610和氮化硅层614,并蚀刻栅极层610和氮化硅层614以形成微缩化-金属-氧化物半导体场效应晶体管600的真实栅极tg和虚拟遮蔽栅极dsg,与真实栅极tg之间具有特定的直线距离,如图如图6(c)

所绘示,真实栅极tg的长度为λ,虚拟遮蔽栅极dsg的长度也为λ,真实栅极tg和虚拟遮蔽栅极dsg之间的距离也是λ。

[0248]

然后,沉积一层旋涂电介电材料712,再对旋涂电介电材料712进行回蚀。经由微影掩膜技术形成设计良好的栅极掩膜层802,如图6(d)所绘示。之后,利用非等向性蚀刻技术移除位于虚拟遮蔽栅极dsg上方的氮化硅层614,并移除虚拟遮蔽栅极dsg、对应于虚拟遮蔽栅极dsg的一部分介电绝缘体612以及对应于虚拟遮蔽栅极dsg的一部分p型基材601,如图6(e)所绘示。

[0249]

此外,还移除栅极掩膜层802,蚀刻旋涂电介电材料712,然后沉积并回蚀第二浅沟隔离-硅氧化物层1002,如图6(f)所绘示。接着,沉积并回蚀第三硅氧化物层以形成第三硅氧化物间隙壁1502,在p型基材601中形成轻掺杂漏极1504,沉积并回蚀氮化硅层以形成氮化硅间隙壁1506,并移除未被氮化硅间隙壁1506、第三硅氧化物间隙壁1502和真实栅极tg所覆盖的一部分介电绝缘体612,如图6(g)所绘示。

[0250]

再利用选择性磊晶生长技术来生长本征硅质电极1602,如图6(h)所绘示。然后沉积并回蚀第三浅沟隔离-硅氧化物层(cvd-sti-oxide3)1702,移除本征硅质电极1602,形成微缩化-金属-氧化物半导体场效应晶体管600的源极区(n+源极掺杂区)1704和漏极区(n+漏极掺杂区)1706,如图6(i)所绘示。由于源极区(n+源极掺杂区)1704和漏极区(n+漏极掺杂区)1706形成在真实栅极tg和第三浅沟隔离-硅氧化物层1702之间,其位置最初是被虚拟遮蔽栅极dsg所占据,因此源极区(n+源极掺杂区)1704和漏极区(n+漏极掺杂区)1706的长度和宽度与λ一样小。源极区(n+源极掺杂区)1704(或漏极区(n+漏极掺杂区)1706)的开口可以小于λ,例如0.8λ。如果进一步形成硅氧化物间隙壁1802,则开口可以再被缩小,如图6(j)所绘示。

[0251]

此外,新型标准元件单元可以使第一内连线金属层m1通过小型化的自对准触结构直接连至栅极、源极区和/或漏极区,而无需使用传统的接触开口掩膜和/或与第一内连线金属层m1连接的第零金属转换层(metal-0translation layer)。在图6(i)的步骤之后,沉积一层旋涂电介电材料1901以填充基材上的空隙,该空隙包括位于源极区(n+源极掺杂区)1704和漏极区(n+漏极掺杂区)1706中的开口1804。然后进行化学机械研磨制成使表面平整,如图6(k)所绘示。图6(l)系根据图6(k)所绘示的结构上视图,其系绘示水平方向上的多个指状结构。

[0252]

此外,使用预先设计好的掩膜(例如,光阻层1902)进行蚀刻,形成沿图6(l)中x轴方向延伸的一些条纹图案,其具有长度为groc(l)的间距,以暴露出栅极沿着y轴延伸的延伸区。其结果绘示于图6(m)的上视图中。如第7(m)所绘示,最激进的设计规则为groc(l)=λ。然后,使用非等向性蚀刻技术移除位于暴露于外的栅极延伸区1903内部的氮化硅覆盖层,从而将导电的金属栅极层暴露出来(如图6(n)所绘示)。

[0253]

此后,移除光阻层1902,然后移除旋涂电介电材料1901,使源极区1704和漏极区1706顶部的开口再次暴露于外。再沉积一层具有预设厚度的硅氧化物1904,并使用非等向性蚀刻技术在源极区1704和漏极区1706顶部的开口以及暴露于外的栅极延伸区1903的四个侧壁上形成间隙壁。因此,可以分别在暴露于外的栅极延伸区1903、源极区1704和漏极区1706中形成自然形成的接触开口。图6(o)系绘示这种晶体管的结构剖面图。图6(p)系根据图6(o)所绘示的结构上视图。其中,位于暴露于外之栅极延伸区1903中的开口,其垂直长度

crmg(l)小于长度为λ的groc(l)。

[0254]

最后,形成一层具有预设厚度的第一内连线金属层m11905,以填充所有接触开口,并根据芯片表面的形貌,形成光滑的表面。然后,使用微影掩膜蚀刻技术分别在这些接触开口之间形成所有连接结构,以实现第一内连线金属层m1必要的内连线网络,如图6(q)所绘示。图6(r)系根据图6(q)所绘示的微缩化-金属-氧化物半导体场效应晶体管600结构上视图。因此,第一内连线金属层m1可以实现接触填充(contact-filling),并作为插塞藉连接(plug-connection)至栅极和源极/漏极的功能,以及直接连接至所有晶体管的内连线功能。无需使用昂贵且非常严格控制的常规接触开口掩膜,也无需进行后续非常困难的接触开口钻孔制程。尤其是在进一步微缩数十亿个晶体管的水平几何尺寸时,这变成是最困难的挑战。此外,也免除了在接触开口中制作金属插塞,并进行化学机械研磨制程,以形成金属栓柱(metal stud)所需要的复杂集成电路加工步骤(例如,为形成第零层金属结构所需要的某些先进技术)。

[0255]

因此,无论制程技术节点(或最小特征尺寸)如何,源极/漏极接触结构(ct_a掩膜,绘示于图5(b)以红色圆圈标记的部分)的尺寸可以微缩到λ

×

λ。同理,可以在栅极线或多晶硅栅极线上方形成栅极接触结构(用于直接连接至第二内连线金属层m2的栅极接触结构(ct_a),如图5(b)所绘示),使栅极接触结构的尺寸也是λ

×

λ。也就是说,晶体管(如图5(a)所绘示的pmos晶体管和nmos晶体管)中的源极、漏极、栅极及其接触结构的线性尺寸可以得到精确控制,此线性尺寸可以小到最小特征尺寸λ(λ)。在本实施例中,源极/漏极接触尺寸会更大,例如λ(y方的向宽度)

×

2λ(x方向的长度),并且两条栅极线或多晶硅线poly栅极线之间的间隙会大于3λ,例如4λ或5λ。

[0256]

此外,如前所述,传统的标准元件单元可能不允许栅极或扩散区在不经过第一内连线金属层m1结构的情况下,直接连接到第二内连线金属层m2结构。本发明公开了一种新型标准元件单元,其中栅极或扩散区(源极区/漏极区)通过一个由contact-a和via1-a组成的垂直导电插塞,以自对准方式直接连接到第二内连线金属层m2,而没有通过第一内连线金属层m1进行转接。其中,垂直导电插塞contact-a和via1-a系分别在同一个晶粒上的不同位置构建其他导电插塞contact和via1的阶段时一起形成的。藉此,可以缩小一部分第一内连线金属层m1与另一部分第一内连线金属层m1之间的必要间隔,而且也会减少内连线结构之间的布线阻碍。

[0257]

下面根据本发明另一实施例,简要描一种用于新型标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管700。其中微缩化-金属-氧化物半导体场效应晶体管700的栅极或扩散区(源极区/漏极区)系经由自对准的方式,直接连接到第二内连线金属层m2,而没有通过第一内连线金属层m1进行转接。图7(a)系根据说明书的另一实施例,绘示一种用于标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管700的结构上视图。图7(b)和图7(c)系沿着图7(a)中的切线c7a1和c7a2所分别绘示的两个构成晶体管的结构剖面图。

[0258]

如图7(b)和图7(c)所绘示,微缩化-金属-氧化物半导体场效应晶体管700是由浅沟隔离结构705来加以定义。微缩化-金属-氧化物半导体场效应晶体管700具有栅极端子702、位于栅极端子702下方的晶体管通道区703和源极/漏极区704。栅极端子702包括栅极介电层702a、形成于栅极介电层702a上方的栅极导电层702b以及形成于栅极导电层702b上方的硅质区(或晶种区(seed region))702c。硅质区702c可以由多晶硅或非晶硅所构成。栅

极端子702还包括位于硅质区702c顶部上方的覆盖层702d(例如氮化硅层),并且进一步包括位于栅极介电层702a、栅极导电层702b、硅质区702c和覆盖层702d的侧壁上方的至少一个间隙壁(例如,包括氮化硅间隙壁702sl和热氧化硅间隙壁702s2)。第一介电层720形成在半导体基材701上,至少覆盖微缩化-金属-氧化物半导体场效应晶体管700的主动区,包括覆盖栅极端子702、源极/漏极区704以及浅沟隔离结构705。

[0259]

多个开孔(例如开孔707a和707b)形成在第一介电层720中,藉以将硅质区702c的顶部71和源极/漏极区704的顶部72暴露于外。在一些实施例中,开孔707a和707b硅经由微影蚀刻制程移除一部分第一介电层720所形成,用以暴露出一部分的硅质区702c和源极/漏极区704的硅质区。在一些实施例中,每一个开孔707a和707b的尺寸可以等于最小特征尺寸(例如微缩化-金属-氧化物半导体场效应晶体管700的临界尺寸)。当然,开孔707a和707b的尺寸也可以大于最小特征尺寸。开孔707a和707b的底部(即硅质区702c暴露在外的顶部71和源极/漏极区704暴露在外的顶部72),分别由具有多晶硅/非晶硅或具有高导电率的重掺杂浓度的晶体硅材料所构成。栅极端子中暴露于外的硅质区702c和源极/漏极端子中暴露于外的硅质区,可以在后续所进行的选择性磊晶生长制程中作为晶种区,并基于此晶种区生长出柱状体(pillars)。

[0260]

然后,如图7(d)至图7(f)所绘示。通过选择性磊晶生长技术,于硅质区702c暴露在外的顶部71和源极/漏极区704暴露在外的顶部72上生长重掺杂导电硅质插塞(或导电柱),形成第一导体柱部分731a和第三导体柱部分731b。然后在第一介电层720上方形成第一介电子层740以使第一介电子层740的顶表面740s与第一导体柱部分731a和第三导体柱部分731b的顶表面基本共面。而第一导体柱部分731a和第三导体柱部分731b的那些「暴露于外的头部」(或暴露于外的顶部表面)可以用来作为后续进行选择性磊晶生长制程的晶种区。再者,由于第一导体柱部分731a及第三导体柱部分731b的上方具有晶种区或晶种柱,而该晶种区或晶种柱可用于后续选择性磊晶生长。随后,可以经由第二次选择性磊晶生长,在第一导体柱部分731a上方形成第二导体柱部分732a;并在第三导体柱部分731b上方形成第四导体柱部分732b。图7(d)系根据说明书的一实施例,绘示在第一导体柱部分731a和第三导体柱部分731b上方分别形成第二导体柱部分732a和第四导体柱部分732b之后的结构的俯视图。图7(e)系沿着图7(d)中的切线c7d1所绘示的结构剖面图。

[0261]

如图7(g)至图7(i)所绘示,可以在第一介电子层740的顶面740s上,以例如铜(cu)、铝(al)、钨(w)或其他合适的导电材料,沉积第一导电层750。然后在第一导电层750上沉积第二介电子层760。图案化第一导电层750和第二介电子层760以定义出开口709,其中第一导体柱730a穿过开口709而不与第一导电层750和第二介电子层760接触。图7(g)系根据说明书的一实施例,绘示在第一介电层740上方形成于第一导电层750与第二介电子层760之后的结构俯视图。图7(h)系沿着图7(g)中的切线c7g1所绘示的结构剖面图。图7(i)系沿着图7(g)中的切线c7g2所绘示的结构剖面图。

[0262]

如图7(j)至第7(l)图所绘示,沉积一个上方介电层770以覆盖第二介电子层760和第一介电子层740并填充开口709。上方介电层770的顶面770s低于第一导体柱730a(包括第一导体柱部分731a和第二导体柱部分732a)和第二导体柱730b(包括第三导体柱部分731b和第四导体柱部分732b)的顶面730t。然后,在上方介电层770上形成上方导电层780。其中,第一导体柱730a连接到上方导电层780但与第一导电层750断开。图7(j)系根据说明书的一

实施例,绘示在上方介电层770上形成上方导电层780之后的结构俯视图。图7(k)系沿着图7(j)中的切线c7j1所绘示的结构剖面图。图7(l)系沿着图7(j)中的切线c7j2所绘示的结构剖面图。

[0263]

如上所述,栅极端子暴露于外的硅质区702c和源极/漏极端子暴露于外的硅质区中的每一者,都具有晶种区,可以在后续进行的选择性磊晶生长制程中,基于晶种区而生长出柱状体。此外,第一导体柱部分731a和第三导体柱部分731b的上部还可以具有晶种区或晶种柱,该晶种区或晶种柱也可用于后续的选择性磊晶生长制程。在本实施例中,只要在导电端子的上部具有晶种子部分或晶种柱,且这些晶种子部分或晶种柱可被应用于后续所进行的选择性磊晶生长制程中;即可以通过一个垂直导电或导体插塞,以自对准方式,使第一内连线金属层m1或导电层直接连接至第x内连线金属层mx(而不连接到其他的内连线金属层导电层m2、m3、..mx-1)。其中,这些晶种子部分或晶种柱的材质不限于硅质,任何一种可以在后续进行的选择性磊晶生长制程中,被用作晶种的材料都未脱离本说明书的发明精神。

[0264]

综上所述,新型标准元件单元至少具有以下优点:

[0265]

(1)标准元件单元中晶体管的源极、漏极和栅极的线性尺寸可以被精确控制,线性尺寸可以微缩到最小特征尺寸lamda(λ)。因此,当两个相邻晶体管通过漏极/源极连接在一起时,晶体管的长度尺寸将可以微缩至3λ,而相邻两个晶体管的栅极边缘之间的距离可以微缩至2λ。当然,若考虑公差,晶体管的长度尺寸会介于3λ至6λ之间或更大,两个相邻晶体管的栅极边缘之间的距离可以介于3λ至5λ之间或更大。

[0266]

(2)第一内连线金属层m1可以通过自对准的微型接触结构直接连接至栅极、源极和/或漏极区,而无需使用传统的接触开口掩膜和/或使用连接第一内连线金属层m1的第零内连线金属转换层m0。

[0267]

(3)栅极和/或扩散区可以直接连接到第二内连线金属层m2,而无需以自对准方式连接至第一内连线金属层m1。因此,可以缩小一部分第一内连线金属层m1与另一部分第一内连线金属层m1之间的必要间隔,而且也会减少内连线结构之间的布线阻碍。此外,同样的结构可以应用于经由导体柱将下方金属层直接连接到位于其上方的上方金属层,但导体柱不会与位于下方金属层和上方金属层之间的任何中间金属层电连接。

[0268]

(4)新型标准元件单元中用于高电位vdd金属线和/或低电位vss金属线可以被分布在硅基材的原始硅表面下方。因此,即使微缩新型标准元件单元的尺寸,仍可避免造成连接至高电位vdd金属线和/或低电位vss的金属线等的接触结构尺寸和其布局之间的相互干扰。此外,在新型标准元件单元中,最初用来将源极/漏极区电性连接至第二内连线金属层m2或第三内连线金属层m3,以作为高电位vdd金属线或接地连接线的源极/漏极区开口,也可以省略。

[0269]

在一些实施例中,导体柱可以是金属导体柱,也可以是金属导体柱与位于其上部的晶种部分或晶种柱组合而成的复合导体柱。图8(a)系根据说明书的又一实施例,绘示一种用于新型标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管800的结构上视图。图8(b)系沿着图8(a)中的切线c8a1所绘示的结构剖面图。图8(c)系沿着图8(a)中的切线c8a2所绘示的结构剖面图。在本实施例中,微缩化-金属-氧化物半导体场效应晶体管800用于连接内连线层的导体柱,包括钨柱和第一高掺杂硅柱,以及位于其上部的晶种区或晶

种柱。

[0270]

例如,如图8(a)至图8(c)所绘示,可以移除图7(j)至图7(k)所绘示的高掺杂n+多晶硅质导体柱部分731a、732a、731b、732b,并以钨质柱状体830w、氮化钛层830n和高掺杂的硅质柱状体来替代。第一导体柱包括金属柱部分830a(其包括钨质柱状体830w和氮化钛层830n)和高掺杂的硅质柱状体810a,第二导体柱包括金属柱部分830b(其包括钨质柱状体830w和氮化钛层830n)和高掺杂的硅质柱状体810b。高掺杂的硅质柱状体810a和810b是被配置来作为生长导体柱的晶种区域或晶种柱,这些导体柱与后续形成的金属内连线连接。例如,高掺杂的硅质柱状体810a和810b可以做为后续选择性磊晶生长制程的晶种区域或晶种柱,进而在其上生长出另一个硅质柱状体,而此导体柱可配置来连接形成在第一介电子层840上方的第一导电层850(例如第一金属子层850a或第二金属子层850b)),使第一导电层850电连接至高掺杂硅质柱状体810a和810b。而这个导体柱的上部又可以具有晶种区或晶种柱。由于高掺杂的硅质柱状体810a和810b被配置来作为后续选择性磊晶生长制程生长另一个导体柱的晶种区域或晶种柱,因此可以满足无限延长的接触结构。

[0271]

在一些实施例中,金属导线(例如第一金属子层850a或850b)的宽度可以与接触结构(例如高掺杂的硅质柱状体810a和810b)的宽度相同或基本相同。当然,金属导线的宽度可以与第一接触结构的宽度不同。如图8(d)至图8(f)所绘示,即使金属导电层850(例如,第一金属子层850a或第二金属子层850b)的宽度与位于其下方的接触插塞的宽度并不相同(可以被微缩到硅质柱状体810a和810b的最小特征尺寸)。然而,虽然不必担心导电层和接触结构之间因为接触面积不足而产生电阻过高的问题。但是,金属导线和位于下方的接触塞之间,仍有可能没有对准。微影掩膜的错位容差仍可能导致金属导电层850(例如,第一金属子层850a或第二金属子层850b)不能完全覆盖接触结构(如图8(e)和图8(f)所绘示)。

[0272]

为了让金属导线和下方接触结构之间的电阻可以得到很好的控制。本发明进一步使用选择性磊晶生长制程生来生长一些额外的高掺杂硅质材料,用以连接金属导线和位于下方的接触插塞,藉以改善由金属导线和下方接触插塞之间因未对准所引起的电阻问题。在本实施例中,进一步使用选择性磊晶生长制程生长高掺杂的硅材料(侧柱820),附着于金属导电层850(例如,第一金属子层850a或第二金属子层850b)的垂直壁上。在图8(d)系根据说明书的再一实施例,绘示一种用于新型标准元件单元中的微缩化-金属-氧化物半导体场效应晶体管800’的结构上视图。图8(e)系沿着图8(d)中的切线c8d1所绘示的结构剖面图。图8(f)系沿着图8(d)中的切线c8d2所绘示的结构剖面图。

[0273]

传统标准元件单元并不允许栅极或源极/漏极在不经过第一内连线金属层m1的情况下,直接连接到第二内连线金属层m2。本发明公开了一种新的标准元件单元,其中栅极或源极/漏极可以经由一个垂直方向的导电插塞,以自对准的方式,连接到第二内连线金属层m2,而无需以第一内连线金属层m1作为过渡层。有关栅极或源极/漏极直接连接至第二内连线金属层m2的技术,可参考2021年11月17日提交,编号为17/528,957的美国专利申请案,标题为「interconnection structure and manufacture method thereof」。此编号为17/528,957的美国专利申请案,其全部内容通过引用并入的方式,全文收载于本说明书之中。

[0274]

另外,本发明公开了一种新型互补式金属-氧化物半导体晶体管结构,其中源极和漏极区被绝缘体完全隔离,这样的绝缘体不仅可以增加晶体管元件对闩锁问题的抵抗力,而且且可以增加基材中的隔离距离,藉以将相邻晶体管的接面加以分隔,从而可以减小各

个接面之间的表面距离(例如,缩小至3λ),从而减小标准元件单元的尺寸。下面简要介绍一种新型互补式金属-氧化物半导体晶体管结构,其中nmos晶体管的源极/漏极区的n+掺杂区被绝缘体完全隔离。

[0275]

请参照图9,图9系根据说明书的又再一实施例,绘示一种用于新型标准元件单元中的nmos晶体管52的结构剖面图。其栅极结构33包括有栅极介电层331和栅极导电层332(例如栅极金属),形成于半导体基材(例如硅质基材)的水平表面或原始表面之上。介电覆盖层333(例如硅氧化物层和氮化硅层的复合物)位于栅极导电层332上方。此外,可以包括由硅氧化物层341和氮化硅层342的复合物所构成的间隙壁34,用于覆盖在栅极结构33的侧壁上。在硅质基材中形成沟槽,源极区55和漏极区56的全部或至少一部分分别位于对应的沟槽之中。nmos晶体管52中的源极区55(或漏极区56)可以包括n+掺杂区552(或漏极区56的n+掺杂区562)或其他合适的掺杂分布区(例如,掺杂浓度从p-掺杂区至p+掺杂区渐层或逐步改变的掺杂区)。

[0276]

此外,包括一个位于沟槽之中且位于源极区下方(例如,氮化硅或其他高介电系数介电材料所构成)的局部隔离结构(localized isolation)48,以及位于另一沟槽之中,并位于漏极区下方的另一局部隔离结构48。这种局部隔离结构48位于在硅质基材的原始水平表面hss的下方,并且可以称为硅基材中的局部隔离结构(localized isolation into silicon substrate,liss)48。此硅基材中的局部隔离结构48可以是厚氮化硅层或介电层的复合物所构成。例如,局部隔离结构或硅基材中的局部隔离结构48可以包括复合局部隔离结构,其包括覆盖沟槽的至少一部分侧壁上的硅氧化物层(第三硅氧化物侧壁(oxide-3v)层481)和覆盖在沟槽的至少一部分底壁上的另一个硅氧化物层(第三硅氧化物底壁(oxide-3b)层482)。第三硅氧化物侧壁层481和第三硅氧化物底壁层482可以经由热氧化制程来形成。

[0277]

复合局部隔离结构48还包括第三氮化硅层483(nitride-3),其位于第三硅氧化物底壁层482上方并与第三硅氧化物侧壁层481接触。值得注意的是,只要第三硅氧化物侧壁层481保持最佳状态并且设计得当,氮化硅层483或第三氮化硅层(nitride-3)可以用任何合适的绝缘材料来加以代替。此外,图9中的浅沟隔离结构可以包括一种复合的浅沟隔离结构49,其包括第一浅沟隔离层491和第二浅沟隔离层492。其中,第一浅沟隔离层491和第二浅沟隔离层492可以分别由不同制程所形成的厚硅氧化物材料来构成。

[0278]

此外,图9中的源极(或漏极)区可以包括复合的源极区55和/或漏极区56。例如,在nmos晶体管51中,复合源极区55(或漏极区56)至少包括轻掺杂漏极551和位于沟槽中的n+重掺杂区552。值得注意的是,轻掺杂漏极551是以均匀的(110)晶格紧靠于暴露于外的硅质表面。暴露于外的硅质表面具有合适的凹陷厚度,其垂直边界可以对应栅极结构的边缘。在图9中凹陷厚度被标示为tec(即晶体管本替被蚀刻掉的厚度,可明确定义为有效通道长度的锐边(sharp edge of effective channel length))。暴露于外的硅质表面基本上与栅极结构对齐。暴露于外的硅质表面可以是晶体管通道的端面(terminal face)。

[0279]

轻掺杂漏极551和n+重掺杂区552可以是基于选择性磊晶生长制程(或原子层沉积(atomic layer deposition,ald)或其他合适选择性生长制程)从用作晶种区暴露于外的tec区中所生长出来的硅质区。其是在局部隔离结构liss上形成具有组织良好的(110)晶格区,这对于改变在复合源极区55或漏极区56中新形成的(110)晶格结构不起晶种作用

(seeding effect)。这种新形成的晶体(包括轻掺杂漏极551和n+重掺杂区552)可以被命名为tec-si,如图9所绘示。

[0280]

在一实施例中,tec与栅极结构33的边缘对齐或大致对齐,轻掺杂漏极551的长度可以调整,轻掺杂漏极551与tec相对的侧壁,与间隙壁34的侧壁对齐或大致对齐。复合源极区55(或复合漏极区56)还可以包括一些钨质(或其他合适的金属材料)插塞553(或复合漏极区56的钨质插塞563),与一部分tec-si形成水平连接,以完成整个源极/漏极区,如图9所绘示。流向金属内连线(例如第一内连线金属层m1)的主动通道电流,通过轻掺杂漏极551和n+重掺杂导电区552到达钨质(或其他金属材料)插塞553。其中,钨质插塞553系经由一些良好的金属对金属欧姆接触结构(metal-to-metal ohmic contact)直接连接到第一内连线金属层m1。金属对金属欧姆接触结构的电阻比传统的硅对接触结构(silicon-to-metal contact)低很多。

[0281]

nmos晶体管51的源极/漏极接触电阻可以根据源极/漏极结构中所使用的融合金属-半导体接面(merged metal-semiconductor junction)的结构而保持在合理的范围之内,如图9所示。这种源极/漏极结构中的融合金属-半导体接面可以改善电流聚集效应并降低接触电阻。此外,由于,源极/漏极结构的底部经由第三硅氧化物底壁层482与基材隔离(如图9所绘示),所以n+到n+或p+到p+的隔离可以保持在合理的范围之内。因此,pmos晶体管(未显示)的两个相邻主动区间的间距可以微缩小到2λ。第三硅氧化物底壁层482可以显著降低源极/漏极源接面的漏电流(source/drain junction leakage current),然后降低n+到n+或p+到p+的漏电流。

[0282]

此外,在目前现有的标准元件单元中,用于连接高压源vdd和低压源vss(或接地)的金属线,系分布在硅基材的原始硅表面之上。如果这些金属线之间没有足够的空间,这样的分布会干扰其他金属线。本发明提供一种新型标准元件单元,其中用于连接高压源vdd和低压源vss)的金属线分布在硅基材的原始硅表面下方。因此,即使缩小标准元件单元的尺寸,也可以避免接触结构的尺寸、连接高压源vdd和低压源vss的金属线等布局等之间的干扰。

[0283]

以图9为例,位于nmos晶体管51漏极区中的钨质(或其他金属材料)插塞553,可以直接电性连接至与高电位vdd金属线电性连接的p型井区pwell。在另一个实施例中,位于nmos晶体管51源极区中的钨质(或其他金属材料)插塞563,可以电性连接至接地的p型井或p型-基材。因此,新型标准元件单元,可以省略位于源极/漏极区中。原本是用来将源极/漏极区与第二内连线金属层m2或第三内连线金属层(m3)电性连接,用以作为高电位vdd金属线或接地连接线,的开口。上述结构的及其制造方法的详细描述可参见2020年8月12日提交,编号为16/991,044的美国专利申请案,标题为「transistor structure and related inverter」。此编号为16/991,044的美国专利申请案,其全部内容通过引用并入的方式,全文收载于本说明书之中。

[0284]

图10(a)系根据说明书的更再一实施例,绘示一种用于新型标准元件单元中的nmos晶体管51和pmos晶体管52的组合结构剖面图。图10(b)是沿图10(a)中的切线(x轴)所绘示的nmos晶体管51和pmos晶体管52的结构剖面图。图10(c)是沿图10(a)中的切线(y轴)所绘示的nmos晶体管51和pmos晶体管52的结构剖面图。如图10(b)所绘示,从n+掺杂区/p型井区接面通过p型井区(或p型基材)/n型井区到n型井区/p+掺杂区接面的路径变得更长。从

n型轻掺杂漏极(ldd-n)/p型井区接面,通过(p型井区/n型井区接面到n型井区/n型轻掺杂漏极(ldd-p)接面的可能闩锁路径(latch-up path),包括如图10(b)所绘示的长度

①

、长度

②

(一个liss区底壁的长度)、长度

③

、长度

④

、长度

⑤

、长度

⑥

、长度

⑦

(另一个liss区的底壁长度)以及长度

⑧

。另一方面,在结合图2所绘示的pmos晶体管12和nmos晶体管11的传统互补式金属-氧化物半导体结构中,从n+掺杂区/p型井区接面,通过p型井区/n型井区接面,到n型井区/p+掺杂区接面的可能闩锁路径只包括(如图2所绘示的)长度长度长度和长度图10(b)所绘示的可能闩锁路径比图2所绘示的可能闩锁路径长。因此,从元件布局的角度来看,图10(b)中pmos晶体管52和nmos晶体管51之间的保留边缘距离(xn+xp)小于图2所绘示的保留边缘距离。例如,保留边缘距离(xn+xp)可以介于2λ至4λ之间,例如3λ。

[0285]

此外,与上述传统标准元件单元不同之处在于,本发明在标准元件单元的pmos晶体管52和nmos晶体管51之间,使用了十字形的硅基材中的局部隔离结构(liss)(例如,第三氮化硅层(nitride-3)+第三硅氧化物层(oxide-3),使得pmos晶体管52和nmos晶体管51之间的可能闩锁路径比传统互补式金属-氧化物半导体结构中的可能闩锁路径更长,进而使得pmos晶体管52和nmos晶体管51之间所需的闩锁距离或保留边缘距离,可以比传统标准元件单元中所需要的闩锁距离或保留边缘距离要短。

[0286]

因此,无论制程技术节点的尺寸(或最小特征尺寸)为何,本发明的pmos晶体管52和nmos晶体管51之间的闩锁距离可微缩至8λ。在本发明中,pmos晶体管52和nmos晶体管51的源极和漏极区的n+掺杂和p+掺杂区分别被绝缘体完全隔离,这样的绝缘体不仅可以增加元件对于闩锁问题的抵抗力,而且还可以增加进入硅基材中的隔离距离,以分离pmos晶体管52和nmos晶体管51中的接面,从而可以减小接面之间的表面距离。pmos晶体管和mnos晶体管的新型组合结构的详细描述,可以参见2021年5月12日提交,编号为17/318,097的美国专利申请案,标题为「complementary mosfet structure with localized isolations in silicon substrate to reduce leakages and prevent latch-up」。此编号为17/318,097的美国专利申请案,其全部内容通过引用并入的方式,全文收载于本说明书之中。

[0287]

为了解决当源极/漏极接触结构尺寸微缩时i-on电流过小的问题,本发明可进一步使用选择性磊晶生长技术生长覆盖在主动区(例如在pmos晶体管52(或nmos晶体管51)的栅极结构33下方的鳍片结构1003)以增强电子/电动迁移率。例如,图10(c)是沿图10(a)中的切线(y轴)所绘示的nmos晶体管51和pmos52晶体管的结构剖面图。其中,薄通道层1001是一种未进行离子植入制程所形成的掺杂通道层。此外,薄通道层1001不是原始硅基材的一部分,因此,薄通道层1001独立于半导体基材。此外,在一个实施例中,薄通道层1001覆盖鳍片结构1003的第一侧壁和第二侧壁,但不覆盖鳍片结构1003的顶面。在另一个实施例中,薄通道层1001包括覆盖鳍片结构1003顶面的一个顶部(未绘示)以及覆盖鳍片结构的第一侧壁和第二侧壁的一个侧部,且顶部和侧部不是同时形成的。晶体管改进i-on电流的详细描述,请参照2021年7月29日提交,编号为第63/226,787号,的美国临时申请案,标题为「new transistor structure and processing method thereof」。此编号为第63/226,787号的美国临时申请案,其全部内容通过引用并入的方式,全文收载于本说明书之中。

[0288]

如上所述,在本发明的结构中,包含有反相器的标准元件单元(如图5(a)和图5(b)

所绘示的新型反相器标准单元500)的面积尺寸(2

×

cpp

×

cell_height)为192λ2。且与各公司(例如a公司、b公司和c公司)所提供的常规产品相比,随着制程技术节点微缩(至少从22nm微缩至5nm),反相器的标准元件单元的面积尺寸(以λ2表示)几乎保持一致,如图11所绘示。图11系绘示本发明所提供的新型标准元件单元之面积尺寸与其他各公司所提供之现有产品的面积尺寸比较结果。

[0289]

然而,新型标准元件单元的布局方式和面积尺寸并不局限于此。在一些其他实施例中,本发明的技术精神可以适用于各种具有不同布局样式和单元尺寸(例如,3

×

cpp

×

cell_height或5

×

cpp

×

cell_height)的标准元件单元(例如,标准元件单元可以是一种单一nor单元、单一nand单元、nor单元

×

2或nand单元

×

2)。

[0290]

例如,图12(a)至图12(c)是根据本说明书的一些实施例,绘示一种具有单一nor单元、单一nand单元和反相器单元

×

2的标准元件单元的结构俯视图和对应的等效电路图。根据说明书的一些实施例。第12图(d)至图12(e)是根据本说明书的一些实施例,绘示一种具有nor单元

×

2和nand单元

×

2的标准元件单元的结构俯视图和对应的等效电路图。其中,单一nor单元、单一nand单元和反相器单元

×

2的标准元件单元的单元尺寸可以为3

×

cpp

×

cell_height;nor单元

×

2和nand单元

×

2的标准元件单元的单元尺寸可以为5

×

cpp

×

cell_height。

[0291]

本发明在新型标准元件单元设计中开发了紧凑的布局样式。在本说明书的一些实施,新的紧凑布局样式可以使标准元件单元具有λ2的面积尺寸,其可以独立于以λ的微缩化(其中,λ是制程技术节点的最小特征尺寸)。通过本说明书所描述的布局设计,可以使标准元件单元的面积尺寸,相对于不同制程技术节点的微缩,仍保持一致或不太敏感,且不会随着标准元件单元的面积尺寸的微缩小而扩大闩锁问题。

[0292]

虽然本发明已以较佳实施例揭露如上,然其并非用以限定本发明,任何该技术领域中具有通常知识者,在不脱离本发明之精神和范围内,当可作些许之更动与润饰,因此本发明之保护范围当视后附的权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1