一种提高UIS性能的SGT-MOSFET及其制造方法与流程

本发明属于电子工程,涉及一种提高uis性能的sgt-mosfet及其制造方法。

背景技术:

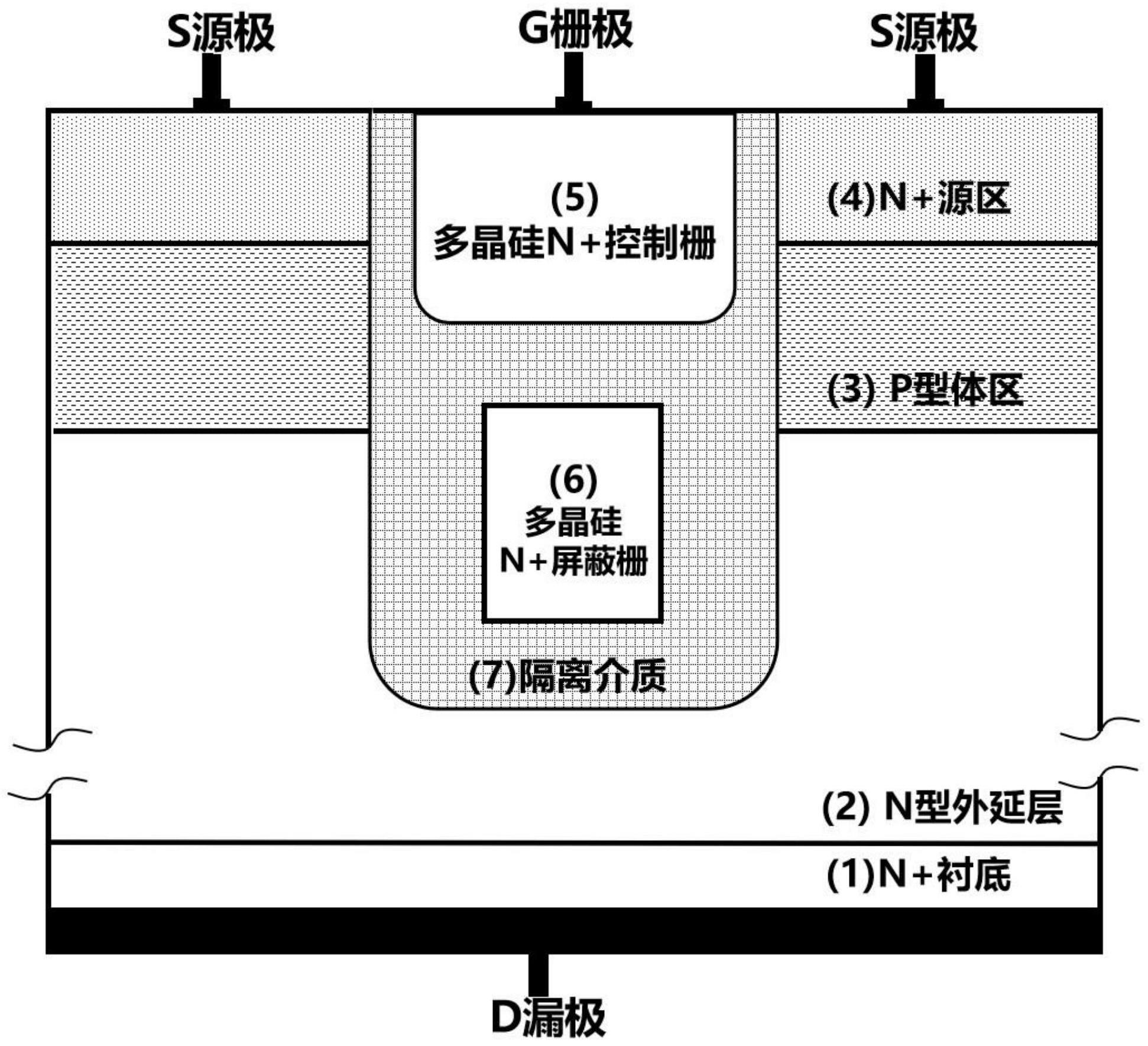

1、传统sgt-mosfet的沟槽结构由两个多晶硅部分组成:上半部分是控制栅,下半部分是屏蔽栅,屏蔽栅位于控制栅下方,如附图1所示。器件导通时漏极电流沿着沟槽的纵向侧壁,在体区表面形成反型层沟道,电子从源区通过沟道后,进入槽栅底部的漂移区,然后电流在整个元胞横截面宽度内展开。由于源区与体区之间的掺杂浓度分布平缓,体区电阻较高,所以寄生的源-体-外延层双极晶体管很容易打开,sgt-mosfet会发生二次击穿,使器件温度升高,uis性能下降,从而对器件造成永久性损坏。

技术实现思路

1、针对这些缺点,本发明提供了一种sgt-mosfet的制造方法,通过在体与源之间形成的抗穿通层,在体和源之间产生高掺杂浓度区域,实现陡峭的浓度分布,从而降低体电阻率,防止寄生双极晶体管开启,提高sgt-mosfet的uis能力。

2、本发明的第一方面在于公开一种提高uis性能的sgt-mosfet,在p型体区与n+源区之间设有抗穿通层。

3、在本发明的一些实施方式中,所述抗穿通层的掺杂浓度高于所述p型体区的掺杂浓度。

4、在本发明的一些实施方式中,所述抗穿通层的掺杂浓度在1e+16atoms/cm3和8e+17atoms/cm3之间。

5、在本发明的一些实施方式中,还包括衬底、n型外延层、多晶硅控制栅、多晶硅屏蔽栅、隔离介质、s源级、g栅极和d漏级。

6、本发明的第二方面在于公开一种第一方面所述的一种根据权利要求1-4任一所述的提高uis性能的sgt-mosfet的制造方法,包括以下步骤:

7、s01,在衬底上的外延层中形成沟槽栅极;

8、s02,在所述外延层上进行第一次推阱步骤,将p型掺杂剂扩散到外延层以形成p型主体区;

9、s03,在所述外延层上进行第二次推阱步骤,将n型的掺杂剂注入到外延层以形成n+源区;

10、s04,在所述p型主体区和所述n+源区界面处形成一个p型的抗穿通层。

11、在本发明的一些实施方式中,s01中,所述形成沟槽栅极的步骤包括在所述外延层中形成沟槽,在所述沟槽内生长屏蔽电极介质层,然后填充屏蔽栅多晶硅,再把上部分多余的多晶刻蚀掉,再形成控制栅和屏蔽栅中间的隔离层,最后再次多晶硅填充并刻蚀多余的多晶硅的步骤。

12、在本发明的一些实施方式中,在本发明的一些实施方式中,s02和s03中,所述p型体区和n+源区位于所述n型外延层的上下两部分或者左右两部分。

13、在本发明的一些实施方式中,s03中,采用25-40kev能量注入(3-5)e+18atoms/cm3浓度的as离子到源区。

14、在本发明的一些实施方式中,s02中,所述第一次推阱步骤中,900-1100℃25-35分钟热过程推阱。

15、在本发明的一些实施方式中,s03中,所述第二次推阱步骤中,1000-1200℃30s的快速热退火方式进行杂质激活。

16、在本发明的一些实施方式中,还包括降低所述抗穿通层在接近沟槽的位置的掺杂浓度的步骤;优选为光刻。

17、本发明的有益效果:

18、本发明的sgt-mosfet的制造方法,通过在体与源之间形成的抗穿通层,在体和源之间产生高掺杂浓度区域,实现陡峭的浓度分布,从而降低体电阻率,防止寄生双极晶体管开启,提高sgt-mosfet的uis能力。

19、本发明的sgt-mosfet的制造方法,在外延层上,以向衬底的方向逐渐减少注入剂量的方式进行第二导电类型掺杂剂的多次注入;在sgt-mosfet器件的体区与源区之间形成了抗穿通层,使体区和源区之间产生高掺杂浓度区域。同时,为保证器件工作时形成正常的导通沟道,通过光刻(或其他)的方式使得抗穿通层在接近沟槽的位置掺杂浓度较低。

技术特征:

1.一种提高uis性能的sgt-mosfet,其特征在于,在p型体区(3)与n+源区(4)之间设有抗穿通层(8)。

2.根据权利要求1所述的提高uis性能的sgt-mosfet,其特征在于,所述抗穿通层(8)的掺杂浓度高于所述p型体区(3)的掺杂浓度。

3.根据权利要求1或2所述的提高uis性能的sgt-mosfet,其特征在于,所述抗穿通层(8)的掺杂浓度在1e+16atoms/cm3和8e+17atoms/cm3之间。

4.根据权利要求1-3任一所述的提高uis性能的sgt-mosfet,其特征在于,还包括衬底(1)、n型外延层(3)、多晶硅控制栅(5)、多晶硅屏蔽栅(6)、隔离介质(7)、s源级、g栅极和d漏级。

5.一种根据权利要求1-4任一所述的提高uis性能的sgt-mosfet的制造方法,其特征在于,包括以下步骤:

6.根据权利要求5所述的提高uis性能的sgt-mosfet的制造方法,其特征在于,s01中,所述形成沟槽栅极的步骤包括在所述外延层(2)中形成沟槽,在所述沟槽内生长屏蔽电极介质层,然后填充屏蔽栅多晶硅,再把上部分多余的多晶刻蚀掉,再形成控制栅和屏蔽栅中间的隔离层,最后再次多晶硅填充并刻蚀多余的多晶硅的步骤。

7.根据权利要求5或6所述的提高uis性能的sgt-mosfet的制造方法,其特征在于,s02和s03中,所述p型体区(3)和n+源区(4)位于所述n型外延层(2)的上下两部分或者左右两部分。

8.根据权利要求5-7任一所述的提高uis性能的sgt-mosfet的制造方法,其特征在于,s03中,采用25-40kev能量注入(3-5)e+18atoms/cm3浓度的as离子到源区。

9.根据权利要求5-8任一所述的提高uis性能的sgt-mosfet的制造方法,其特征在于,s02中,所述第一次推阱步骤中,900-1100℃25-35分钟热过程推阱;

10.根据权利要求5-9任一所述的提高uis性能的sgt-mosfet的制造方法,其特征在于,还包括降低所述抗穿通层(8)在接近沟槽的位置的掺杂浓度的步骤;优选为光刻。

技术总结

本发明公开了一种提高UIS性能的SGT‑MOSFET及其制造方法,属于电子半导体技术领域。该提高UIS性能的SGT‑MOSFET在P型体区与N+源区之间设有抗穿通层。本发明的SGT‑MOSFET的制造方法,通过在体与源之间形成的抗穿通层,在体和源之间产生高掺杂浓度区域,实现陡峭的浓度分布,从而降低体电阻率,防止寄生双极晶体管开启,提高SGT‑MOSFET的UIS能力。本发明的SGT‑MOSFET的制造方法,在外延层上,以向衬底的方向逐渐减少注入剂量的方式进行第二导电类型掺杂剂的多次注入;在SGT‑MOSFET器件的体区与源区之间形成了抗穿通层,使体区和源区之间产生高掺杂浓度区域。同时,为保证器件工作时形成正常的导通沟道,通过光刻(或其他)的方式使得抗穿通层在接近沟槽的位置掺杂浓度较低。

技术研发人员:贾淑方,王芮,余健,洪学天,王尧林,赵大国,林和

受保护的技术使用者:弘大芯源(深圳)半导体有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!