半导体装置及其形成方法与流程

本发明涉及一种半导体装置及其形成方法,特别是涉及一种具有外延层的半导体装置及其形成方法。

背景技术:

1、随着集成电路的发展,耗电量少且适合高集成度的金属氧化物半导体(metal-oxide-semiconductor,mos)晶体管已被广泛地应用于半导体制作工艺中。mos晶体管一般包括栅极(gate)以及位于两侧的两掺杂区,分别作为源极(source)与漏极(drain)。在一些情况下,为了能进一步增加mos晶体管的载流子迁移率,还可选择对栅极沟道区施加压缩应力或是伸张应力。举例来说,若需要施加的是压缩应力,现有技术常利用选择性外延成长(selective epitaxial growth,seg)技术于基底内形成晶格排列与该基底相同的外延结构,例如硅化锗(silicon germanium,sige)外延结构。利用硅化锗外延结构的晶格常数(lattice constant)大于该基底晶格的特点,对p型金属氧化物半导体晶体管的该栅极沟道区产生应力,增加载流子迁移率(carrier mobility),并由此增加金属氧化物半导体晶体管的速度。反之,若是n型半导体晶体管则可选择于该基底内形成硅化碳(siliconcarbide,sic)外延结构,对该栅极沟道区产生伸张应力。

2、前述方法虽然可以有效提升沟道区的载流子迁移率,却导致整体制作工艺的复杂度以及制作工艺控制的难度,尤其是在半导体装置尺寸持续缩小的趋势下。举例来说,现有技术往往是以掩模在该基底定义一凹槽区,再于该凹槽区中形成外延结构。然而,当半导体装置日益微型化,无法精准控制该凹槽区形成的位置,容易衍生损伤轻掺杂漏极区(ldd)而导致短沟道效应(short channel effect)等负面影响,造成漏电流增加,因而损及元件的品质及效能。因此,现行技术还待进一步改良,以获得更具有可靠度的装置。

技术实现思路

1、本发明提供一种半导体装置及其形成方法,额外在外延层上设置包括氧化物材质的保护层,以改善漏电流问题,以获得更具有可靠度的半导体装置。

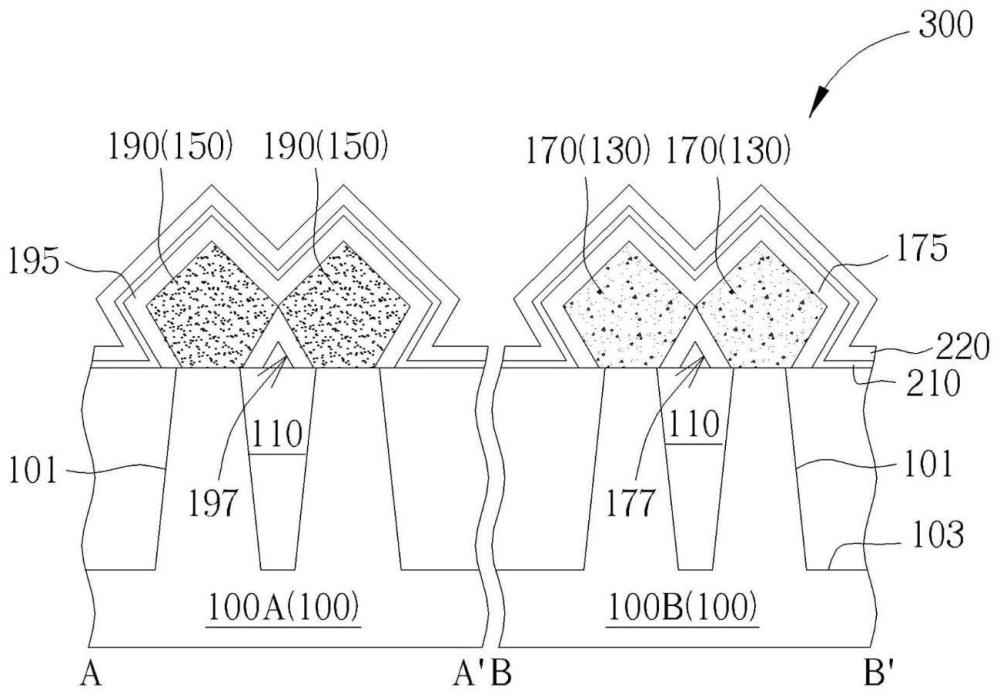

2、本发明的目的在于提供一种半导体装置,包括一基底、一第一外延层、一第一保护层、以及一接触孔蚀刻停止层。该基底包括一p型晶体管区,该第一外延层设置在该基底上并位于该p型晶体管区内。该第一保护层设置在该第一外延层上,覆盖该第一外延层的表面。该接触孔蚀刻停止层设置在该第一保护层与该基底上,其中,该第一保护层的一部分自该接触孔蚀刻停止层暴露出。

3、本发明的目的在于提供一种半导体装置的形成方法,包括以下步骤。首先,提供一基底,该基底包括一p型晶体管区。接着,在该基底上形成一第一外延层,位于该p型晶体管区内,并且在该第一外延层上形成一第一保护层,覆盖该第一外延层的表面。然后,在该第一保护层与该基底上形成一接触孔蚀刻停止层,其中,该第一保护层的一部分自该接触孔蚀刻停止层暴露出。

技术特征:

1.一种半导体装置,包括:

2.如权利要求1所述的半导体装置,其中,该第一保护层包括双层结构,该双层结构包括依序堆叠在该第一外延层上的第一氧化物层以及第二氧化物层。

3.如权利要求2所述的半导体装置,其中,该第二氧化物层的厚度大于该第一氧化物层。

4.如权利要求1所述的半导体装置,其中,还包括应力缓冲层,设置在该第一保护层与该接触孔蚀刻停止层之间,该应力缓冲层与该第一保护层包括相同材质。

5.如权利要求1所述的半导体装置,还包括:

6.如权利要求5所述的半导体装置,其中,该第一保护层与该第二保护层包括相同的厚度。

7.如权利要求5所述的半导体装置,其中,该第一保护层包括双层结构,该第二保护层包括单层结构。

8.如权利要求5所述的半导体装置,还包括:

9.如权利要求5所述的半导体装置,其中,该第二外延层包括硅化碳、硅化碳磷或硅化磷,该第一外延层包括硅化锗、硅化锗硼或硅化锗锡。

10.一种半导体装置的形成方法,包括:

11.如权利要求10所述的半导体装置的形成方法,其中,形成该第一保护层还包括:

12.如权利要求11所述的半导体装置的形成方法,其中,该第一氧化物层包括磷残留物,该第二氧化物层不包括磷残留物,并且,在该清洗制作工艺之后去除该第一氧化物层内的该磷残留物。

13.如权利要求11所述的半导体装置的形成方法,其中,在进行该清洗制作工艺时,完全移除该第一氧化物层,该第一保护层包括该第二氧化物层。

14.如权利要求11所述的半导体装置的形成方法,其中,在进行该清洗制作工艺时,部分移除该第一氧化物层,该第一保护层包括依序堆叠在该第一外延层上的残留的该第一氧化物层与该第二氧化物层。

15.如权利要求11所述的半导体装置的形成方法,还包括:

16.如权利要求15所述的半导体装置的形成方法,还包括:

17.如权利要求15所述的半导体装置的形成方法,还包括:

18.如权利要求11所述的半导体装置的形成方法,其中,该第一氧化处理与该第二氧化处理包括热氧化处理制作工艺。

19.如权利要求18所述的半导体装置的形成方法,其中,该接触孔蚀刻停止层的形成还包括:

20.如权利要求19所述的半导体装置的形成方法,其中,该应力缓冲层与该第一保护层包括相同材质。

技术总结

本发明公开一种半导体装置及其形成方法,包括基底、第一外延层、第一保护层以及接触孔蚀刻停止层。基底包括P型晶体管区,第一外延层设置在基底上并位于P型晶体管区内。第一保护层设置在第一外延层上,覆盖第一外延层的表面。接触孔蚀刻停止层设置在第一保护层与基底上,其中,第一保护层的一部分自接触孔蚀刻停止层暴露出。

技术研发人员:纪奕玮,许得彰,王尧展,吴孟筠,黄俊仁

受保护的技术使用者:联华电子股份有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!