一种低剖面硅基CMOS相控阵天线的制作方法

一种低剖面硅基cmos相控阵天线

技术领域

1.本发明属于天线技术领域,具体涉及一种低剖面硅基cmos相控阵天线。

背景技术:

2.传统相控阵天线分为砖块式和瓦块式两种架构,相控阵天线的集成方式通常以t/r组件形态及和天线的组装形式为依据。砖块式相控阵天线中t/r组件为纵向集成,天线结构为横向组装;而瓦块式相控阵天线的t/r组件为横向集成,天线结构为纵向组装。

3.传统由t/r组件组装起来的砖块式或瓦块式相控阵天线存在以下缺点:1、毫米波器件多采用化合物半导体微波毫米波单片集成电路(gaas/ganmmic)多芯片组合的方案,单通道的t/r成本较高;2、t/r组件封装采用微组装、微焊接等工艺,将各种集成芯片与片式元器件,封装在同一管壳或者腔体内,体积重量大、封装成本高;3、集成结构采用相控阵芯片-t/r组件-相控阵天线三层构架,集成度低、模块数量多、组装效率低。

技术实现要素:

4.为解决上述技术问题,本发明提供了一种低剖面硅基cmos相控阵天线,解决了传统砖块式和瓦块式相控阵天线集成度低、成本高,难以满足三毫米频段相控阵天线集成度和成本要求的难题。

5.本发明通过以下技术方案得以实现。

6.本发明提供的一种低剖面硅基cmos相控阵天线,包括天线单元、复合基板、t/r芯片、和差器、刚扰板以及波控板,所述复合基板为圆盘状,所述天线单元固定于复合基板的上表面,所述t/r芯片的一端固定连接于复合基板的下表面,另一端与所述和差器的上表面接触;所述和差器为金属腔体结构,上端连接于所述复合基板的下表面;所述波控板固定于所述和差器的下端面上,所述刚扰板包裹于和差器外部,一端与复合基板连接,另一端与所述波控板连接。

7.进一步的,所述t/r芯片为多通道硅基cmos t/r芯片,通道数为16。

8.进一步的,所述t/r芯片与复合基板接触的一面贴有散热片。

9.进一步的,所述多层基板与和差器连接安装时,先用定位销钉进行定位之间,再使用银浆对对接的缝隙处进行粘接。

10.进一步的,所述和差器的上端面设有与所述t/r芯片相适应的内凹槽,所述t/r芯片与固定连接于复合基板时置于和差器上端面的内凹槽中。

11.进一步的,所述波控板通过螺装工艺固定于和差器的下表面上。

12.进一步的,所述t/r芯片为64个,每16个为一个象限,均布于复合基板的下表面上。

13.进一步的,还包括功分器,所述功分器为4个,每个象限的16个t/r芯片通过1个功分器与和差器电路连接。

14.本发明的有益效果在于:通过本发明的实施,采用表贴式相控阵构架,替代传统相控阵芯片-t/r组件-相控阵天线三层构架,将多通道t/r组件集成到一颗芯片内部,直接表

贴在天线板上,构造一个低剖面三毫米频段相控阵天线;利用硅基cmos工艺高集成、低成本的优势,将16个t/r通道的接收、发射、收发控制、移相衰减控制、spi接口转换以及功分网络等功能电路集成到一颗硅基cmos三毫米相控阵t/r芯片中,实现三毫米相控阵天线组件高集成、芯片化、低成本;多通道硅基cmos三毫米t/r芯片经封装后直接贴装在天线电路多层微波复合基板上,基板紧锢在和差器金属结构件上,波控电源板同样固定在和差器金属结构件上,此种结构在散热性能好,解决了传统砖块式和瓦块式相控阵天线集成度低、成本高,难以满足三毫米频段相控阵天线集成度和成本要求的难题,该产品在某预研项目中得到运用,达到了预期效果。

附图说明

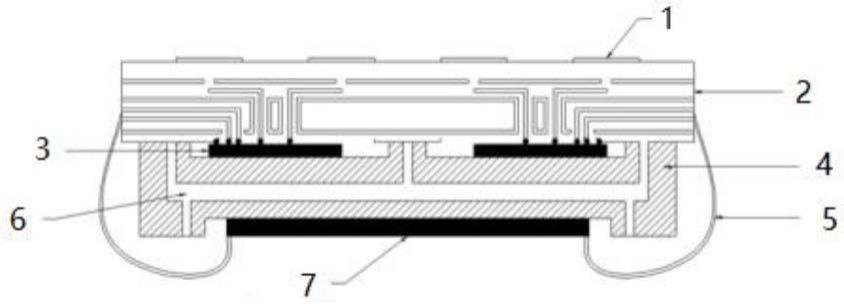

15.图1是本发明的结构示意图;

16.图2是本发明的功能组成框图;

17.图中:1-天线单元,2-复合基板,3-t/r芯片,4-和差器,5-刚扰板,6-和差网络,7-波控板。

具体实施方式

18.下面进一步描述本发明的技术方案,但要求保护的范围并不局限于所述。

19.如图1-2所示,本发明提供的一种低剖面硅基cmos相控阵天线,包括天线单元1、复合基板2、t/r芯片3、和差器4、刚扰板5以及波控板7,复合基板2为圆盘状,天线单元1固定于复合基板2的上表面,t/r芯片3的一端固定连接于复合基板2的下表面,另一端与和差器4的上表面接触;和差器4为金属腔体结构,上端连接于复合基板2的下表面;波控板7固定于和差器4的下端面上,刚扰板5包裹于和差器4外部,一端与复合基板2连接,另一端与波控板7连接。t/r芯片3为通道数为16的多通道硅基cmos t/r芯片3。t/r芯片3为64个,每16个为一个象限,均布于复合基板2的下表面上。还包括功分器,功分器为4个,每个象限的16个t/r芯片3通过1个功分器与和差器4电路连接。

20.复合基板2为多层微波复合基板2,天线单元1、t/r芯片3、控制与电源馈线网络集成于其中,t/r芯片3以倒装焊方式焊接于多层复合基板2底面;和差器4为金属腔结构,同时作为t/r芯片3的散热载体,t/r芯片3背面贴散热片与和差器4的金属腔壁贴装;多层基板与和差器4之间由销钉孔定位并通过银浆粘接在一起;天线的spi信号和电源信号通过刚扰板5与波控板7连接,波控板7螺装到和差器4的金属腔下表面。

21.本发明的低剖面硅基cmos相控阵天线具有超薄、超轻、可共形、可扩展等特点,其口径为127mm,总厚度为35mm,共使用64颗16通道硅基cmos三毫米t/r芯片,形成1024个通道,单元间距为2.4mm

×

2.4mm。

22.从功能上而言,本发明从上到下分别是天线阵面、散热板、和差网络6及波控网络,其中,在结构上散热板与和差网络6集中与和差器4上,即使用和差器4的腔体作为散热板,和差网络6设置于其中,波控网络设置在波控板7上。天线阵面包含天线单元1与集成芯片模块,阵面采用三角阵方式,在充分利用口径的前提下,减小通道数,实现天线阵面的低成本。集成芯片模块包含馈电网络,校准网络以及spi及供电信号转换电路并集成多通道硅基cmos t/r芯片及前级驱动芯片,实现数字波控信号到模拟幅相控制信号转换及收发切换开

关控制。散热板既是芯片和电路基片的载体,也是安装波控板7的盖板,同时是热容和导热良导体,散热板对应电路基片微带及器件位置,开盲槽避让;和差网络6采用波导电桥结构,实现四象限的和差差波束。波控网络的硬件电路包括数字控制dc-dc电源、射频供电dc-dc、数字控制逻辑。数字控制电路主要由fpga、配制芯片、并行flash(用于存储量化数据)、串行flash(用于存储指向精度数据)、低频连接器组成。

23.工作原理:

24.发射时,激励信号进入天线的和差器4后,等幅功分为4路,分别提供给天线阵面的天线单元1的4个象限。天线单元1的每象限内,微波信号16路等功分输入到16颗通道数为16的多通道硅基cmos t/r芯片上,经过16通道的多通道硅基cmos t/r芯片的t通道放大,相位调整,最后由阵面上的天线辐射到自由空间。

25.接收时,天线从自由空间中接收的信号有16通道的多通道硅基cmos t/r芯片的r通道放大,再由幅相控制器控制每路信号的幅相,再等幅合成,4路信号输入和差器4,产生和、差、差信号。

26.阵面的收发切换、波束扫描、通道开关等功能由信号处理分机通过spi控制接口控制;信处分机将频率、波束指向信号通过spi发给波控分机,波控分机经过解算后,结合板上存储的天线阵元幅相校准数据生成各通道对应的幅相控制信息,传送给多通道硅基cmos t/r芯片执行;电源分机提供的电源由电源板上dc/dc芯片给阵面的芯片供电。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1