显示装置的制作方法

显示装置

1.相关申请的交叉引用

2.本技术要求于2021年9月17日提交的第10-2021-0125175号韩国专利申请的优先权和权益,该韩国专利申请的全部公开内容通过引用以其整体并入本文中。

技术领域

3.本公开的各种实施方式涉及显示装置。

背景技术:

4.近来,随着对信息显示的兴趣的增加,已经持续开展对显示装置的研究和开发。

技术实现要素:

5.本公开的各种实施方式涉及显示装置,其中可以确保大到足以在其中布置发光元件的区域,从而可以提高发射效率,并且可以适当地降低功耗。

6.本公开不限于以上描述的方面,并且本领域技术人员根据以下描述将清楚地理解未提及的其它方面。

7.根据一些实施方式的显示装置可以包括:第一电力线和第二电力线,在衬底上;第一电极,通过在第一方向上连续布置的第一接触部分电连接到第一电力线;第二电极,通过第二接触部分电连接到第二电力线,并且在第一方向上与第一电极间隔开;发光元件,在第一电极和第二电极上;以及像素电路,电连接到发光元件,并且包括晶体管和存储电容器,存储电容器具有在平面图中在与第一方向不同的第二方向上延伸的形状。

8.显示装置还可以包括:第一子像素,配置成发射第一颜色的光;第二子像素,配置成发射第二颜色的光;以及第三子像素,配置成发射第三颜色的光,其中,第二方向与第一子像素、第二子像素和第三子像素沿其彼此间隔开的方向交叉。

9.显示装置还可以包括:第一子像素,配置成发射第一颜色的光;第二子像素,配置成发射第二颜色的光;以及第三子像素,配置成发射第三颜色的光,其中,存储电容器包括:第一存储电容器,在第一子像素中;第二存储电容器,在第二子像素中;以及第三存储电容器,在第三子像素中,以及其中,第一存储电容器、第二存储电容器和第三存储电容器在第一子像素、第二子像素和第三子像素沿其彼此间隔开的方向上彼此间隔开。

10.存储电容器相对于第一方向的最大长度或宽度可以小于存储电容器相对于第二方向的最大长度或宽度。

11.第一电力线可以在与第二方向交叉的方向上延伸。

12.显示装置还可以包括:第一子像素,配置成发射第一颜色的光;第二子像素,配置成发射第二颜色的光;以及第三子像素,配置成发射第三颜色的光,其中,第一电力线在第一子像素、第二子像素和第三子像素沿其彼此间隔开的方向上延伸。

13.第一电力线可以在第一方向上延伸,并且在第一接触部分和存储电容器之间。

14.第一接触部分在平面图中可能不与第一电力线重叠,并且可以通过在与第一电力

线相同的层处的电极图案电连接到第一电力线。

15.显示装置还可以包括与第二电极一体地形成的公共连接电极,其中,在平面图中,第一接触部分与第一电极重叠,并且第二接触部分与公共连接电极重叠。

16.显示装置还可以包括堤部,堤部在衬底的厚度方向上突出,并且限定:第二开口,第一接触部分和第二接触部分位于第二开口中,并且发光元件不位于第二开口中;以及第一开口,与其中定位有发光元件的发射区域重叠。

17.第一接触部分和第二接触部分在平面图中可能不与堤部重叠,其中,存储电容器的至少一部分在平面图中不与堤部重叠。

18.第一接触部分可以沿着在第一方向上延伸的第一线布置,其中,第二接触部分沿着在第一方向上延伸的第二线布置,以及其中,存储电容器在第一线和第二线之间。

19.第一方向可以与存储电容器沿其延伸的方向交叉。

20.显示装置还可以包括:第一子像素,配置成发射第一颜色的光;第二子像素,配置成发射第二颜色的光;以及第三子像素,配置成发射第三颜色的光,其中,存储电容器包括用于第一子像素的第一存储电容器、用于第二子像素的第二存储电容器以及用于第三子像素的第三存储电容器,以及其中,第一存储电容器、第二存储电容器和第三存储电容器沿其布置的方向与第一方向平行。

21.显示装置还可以包括子像素,子像素包括发光元件和颜色转换层,颜色转换层包括波长转换图案,使得子像素发射不同颜色的光。

22.子像素可以包括:第一子像素,配置成发射第一颜色的光;第二子像素,配置成发射第二颜色的光;以及第三子像素,配置成发射第三颜色的光,其中,发光元件配置成发射第三颜色的光。

23.波长转换图案可以包括配置成改变光的波长的量子点。

24.显示装置还可以包括滤色器层,滤色器层在颜色转换层上,并且配置成允许相应颜色的光选择性地从其穿过。

25.根据一些实施方式的显示装置可以包括:第一子像素,包括第一像素电路,并且配置成发射第一颜色的光,其中第一像素电路包括在第二方向上延伸的第一存储电容器;以及第二子像素,在与第二方向交叉的第一方向上与第一子像素间隔开,包括第二像素电路,并且配置成发射第二颜色的光,其中第二像素电路包括在第二方向上延伸并且在第一方向上与第一存储电容器间隔开的第二存储电容器。

26.根据一些实施方式的显示装置可以包括:衬底;第一电极和第二电极,在衬底上;发光元件,在第一电极和第二电极上;像素电路,电连接到发光元件,并且包括存储电容器;以及电力线,通过接触部分电连接到第一电极,电连接到发光元件,在第一方向上延伸,并且在平面图中位于接触部分和存储电容器之间。

27.本公开的方面可以不限于以上,并且本公开的其它方面对于本领域普通技术人员将从以下提供的公开内容连同附图清楚地理解。

附图说明

28.图1和图2是示出根据一些实施方式的发光元件的立体图和剖视图。

29.图3是示意性示出根据一些实施方式的显示装置的平面图。

30.图4是示出根据一些实施方式的包括在子像素中的像素电路的电路图。

31.图5是用于描述根据一些实施方式的显示装置中包括的堆叠结构的剖视图。

32.图6至图8是示出根据一些实施方式的像素中包括的电极的布局图。

33.图9和图10是示出发光元件的布置结构的平面图。

34.图11是示出根据一些实施方式的像素的平面图。

35.图12是沿着图11的线i-i'截取的剖视图。

36.图13和图14是沿着图3的线ii-ii'截取的剖视图。

具体实施方式

37.本公开的一些实施方式的方面以及实现其的方法可以通过参考对实施方式的详细描述以及附图而更容易理解。在下文中,将参考附图更详细地描述实施方式。然而,所描述的实施方式可以具有各种修改,并且可以以各种不同的形式实施,并且不应被解释为仅受限于本文中示出的实施方式。更确切地说,这些实施方式提供为示例使得本公开将是透彻且完整的,并且将向本领域技术人员充分地传达本公开的方面,并且应理解,本公开涵盖在本公开的构思和技术范围内的所有修改、等同和替换。因此,可以不描述对于本领域普通技术人员完整地理解本公开的方面而言不必要的过程、元件和技术。

38.除非另外说明,否则在全部附图和书面描述中,相同的附图标记、字符或其组合表示相同的元件,并且因此,将不重复其描述。另外,可能没有示出与实施方式的描述不相关或与之无关的部分以使得描述清楚。

39.在附图中,为了清楚,元件、层和区域的相对尺寸可以被夸大。另外,在附图中使用交叉影线和/或阴影通常是为了使相邻元件之间的边界清楚。因此,除非有说明,否则交叉影线或阴影的存在或不存在都不传达或指示对特定材料、材料性质、尺寸、比例、图示元件之间的共性和/或元件的任何其它特性、属性、性质等的任何偏好或要求。

40.本文中参考作为实施方式和/或中间结构的示意图的剖视图来描述各种实施方式。如此,将预期到例如由于制造技术和/或公差而导致的与图示形状的偏差。另外,本文中公开的特定结构性或功能性描述仅是说明性的,以用于描述根据本公开的构思的实施方式的目的。因此,本文中所公开的实施方式不应解释为受限于区域的具体示出的形状,而是将包括例如由制造而导致的形状的偏差。

41.例如,示出为矩形的植入区域将通常在其边缘处具有圆化的或曲化的特征和/或植入浓度的梯度,而不是从植入区域到非植入区域的二元变化。同样地,通过植入而形成的埋置区域可能导致在埋置区域与通过其发生植入的表面之间的区域中的一些植入。

42.因此,图中示出的区域本质上是示意性的,并且它们的形状不旨在示出装置的区域的实际形状,并且不旨在进行限制。此外,如本领域技术人员将认识到的,在均不背离本公开的精神或范围的情况下,所描述的实施方式可以以各种不同的方式进行修改。

43.在详细描述中,出于说明的目的,阐述了诸多具体细节以提供对各种实施方式的透彻理解。然而,显而易见的是,各种实施方式可以在没有这些具体细节或具有一个或多个等同布置的情况下实施。在其它实例中,公知的结构和装置以框图形式示出,以避免不必要地模糊各种实施方式。

44.为便于说明,可以在本文中使用空间相对术语,诸如“下面”、“下方”、“下部”、“之

下”、“上方”、“上部”等来描述如图中所示的一个元件或特征与另一(些)元件或特征的关系。将理解,除了附图中描绘的取向之外,空间相对术语旨在包含装置在使用或操作中的不同取向。例如,如果附图中的装置被翻转,则被描述为在其它元件或特征“下方”或“下面”或“之下”的元件将随之被取向在其它元件或特征“上方”。因此,示例性术语“下方”和“之下”可以包含上方和下方两种取向。装置可以具有另外的取向(例如,旋转90度或处于其它取向),并且本文中使用的空间相对描述语应相应地进行解释。类似地,当第一部分被描述为布置在第二部分“上”时,这指示第一部分布置在第二部分的上侧或下侧处,而不限于其基于重力方向的上侧。

45.此外,在本说明书中,短语“在平面上”或“平面图”意指从顶部观察目标部分,并且短语“在剖面上”意指从侧面观察通过竖直切割目标部分而形成的剖面。

46.将理解,当元件、层、区域或部件被称为“形成在”另一元件、层、区域或部件“上”、在另一元件、层、区域或部件“上”、“连接到”或“联接到”另一元件、层、区域或部件时,其可以直接形成在另一元件、层、区域或部件上、或者直接在另一元件、层、区域或部件上、或者直接连接到或直接联接到另一元件、层、区域或部件,或者间接形成在另一元件、层、区域或部件上、或者间接在另一元件、层、区域或部件上、或者间接连接到或间接联接到另一元件、层、区域或部件使得可以存在一个或多个中间的元件、层、区域或部件。另外,这可以总体上意指直接或间接的联接或连接、以及一体式或非一体式的联接或连接。例如,当层、区域或部件被称为“电连接”或“电联接”到另一层、区域或部件时,其可以直接电连接或直接电联接到另一层、区域和/或部件,或可以存在中间的层、区域或部件。然而,“直接连接/直接联接”或“直接在

…

上”表示在没有中间部件的情况下,一个部件直接地连接/联接另一部件或在另一部件上。同时,可以类似地解释描述部件之间的关系的其它表述,诸如“在

…

之间”和“直接在

…

之间”或“邻近于”和“直接邻近于”。此外,还将理解,当元件或层被称为在两个元件或层“之间”时,其可以是所述两个元件或层之间的唯一的元件或层,或者也可以存在一个或多个中间的元件或层。

47.出于本公开的目的,当位于一列表的元素之后时,诸如

“…

中的至少一个”的表述修饰整个列表的元素而不是修饰该列表中的个别元素。例如,“x、y和z中的至少一个”和“选自由x、y和z构成的组中的至少一个”可以解释为仅x、或仅y、或仅z、或x、y和z中的两个或更多个的任意组合(诸如,以xyz、xyy、yz和zz为例)、或其任何变形。类似地,诸如“a和b中的至少一个”的表述可以包括a、b、或a和b。如本文中所使用的,“或”通常意指“和/或”,并且术语“和/或”包括相关列出项目中的一个或多个的任何和所有组合。例如,诸如“a和/或b”的表述可以包括a、b、或a和b。

48.将理解的是,虽然在本文中可以使用术语“第一”、“第二”、“第三”等来描述各种元件、部件、区域、层和/或部分,但是这些元件、部件、区域、层和/或部分不应被这些术语限制。这些术语用于将一个元件、部件、区域、层或部分与另一元件、部件、区域、层或部分区分开。因此,在不背离本公开的精神和范围的情况下,以下所描述的第一元件、第一部件、第一区域、第一层或第一部分可以被称为第二元件、第二部件、第二区域、第二层或第二部分。将元件描述为“第一”元件可以不需要或可以不暗示第二元件或其它元件的存在。在本文中也可以使用术语“第一”、“第二”等来区分不同类别或不同组的元件。为了简洁,术语“第一”、“第二”等可以分别表示“第一类别(或第一组)”、“第二类别(或第二组)”等。

49.在示例中,x轴、y轴和/或z轴不限于直角坐标系的三个轴,并且可以以更宽泛的含义来解释。例如,x轴、y轴和z轴可以彼此垂直,或者可以表示彼此不垂直的不同的方向。这同样适用于第一方向、第二方向和/或第三方向。

50.本文中使用的术语仅用于描述特定实施方式的目的,并且不旨在限制本公开。如本文中所使用的,单数形式“一(a)”和“一个(an)”旨在也包括复数形式,除非上下文另有明确指示。还将理解,当在本说明书中使用时,术语“包括(comprises)”、“包括(comprising)”、“具有(have)”、“具有(having)”、“包括(includes)”和“包括(including)”指定所阐述的特征、整体、步骤、操作、元件和/或部件的存在,但不排除一个或多个其它特征、整体、步骤、操作、元件、部件和/或其组合的存在或添加。

51.当一个或多个实施方式可以不同地实施时,可以与所描述的顺序不同地执行具体的工艺顺序。例如,两个连续描述的工艺可以基本上同时执行或者以与所描述的顺序相反的顺序执行。

52.如本文中所使用的,术语“基本上”、“约”、“近似”和类似的术语用作近似术语而不用作程度术语,并且旨在解释将由本领域普通技术人员认识到的所测量或计算的值中的固有偏差。如本文中所使用的,“约”或“近似”包括所述值以及如由本领域普通技术人员在考虑到所讨论的测量和与特定量的测量相关的误差(即,测量系统的限制)时所确定的特定值的可接受偏差范围内的平均值。例如,“约”可以表示在一个或多个标准偏差内,或在所述值的

±

30%、

±

20%、

±

10%、

±

5%内。另外,在描述本公开的实施方式时使用的“可以”表示“本公开的一个或多个实施方式”。

53.除非另有限定,否则本文中使用的所有术语(包括技术术语和科学术语)具有与本公开所属领域中的普通技术人员所通常理解的含义相同的含义。还将理解的是,术语,诸如在常用字典中限定的那些术语,应被解释为具有与其在相关领域和/或本说明书的上下文中的含义一致的含义,并且除非在本文中明确地如此限定,否则不应以理想化或过于形式化的含义进行解释。

54.将参考图1和图2描述根据一些实施方式的包括在显示装置(参考图3的“dd”)中的发光元件ld。

55.图1和图2示出了根据一些实施方式的显示装置中包括的发光元件ld。图1和图2是示出根据一些实施方式的发光元件ld的立体图和剖视图。

56.参考图1至图2,发光元件ld可以包括第一半导体层sec1、第二半导体层sec2、以及插置在第一半导体层sec1和第二半导体层sec2之间的有源层al。发光元件ld还可以包括电极层ell。在一些实施方式中,第一半导体层sec1、有源层al、第二半导体层sec2和电极层ell可以在发光元件ld的纵向方向(例如,长度l的方向)上连续堆叠。

57.发光元件ld可以包括第一端ep1和第二端ep2。第一半导体层sec1可以与发光元件ld的第一端ep1相邻。第二半导体层sec2和电极层ell可以与发光元件ld的第二端ep2相邻。

58.在一些实施方式中,发光元件ld可以具有柱形状。柱形状可以表示在纵向方向(例如,长度l的方向)上延伸的诸如圆柱形状或棱柱形状的形状。换言之,发光元件ld的长度l可以大于其直径d(或其剖面的宽度)。发光元件ld的剖面形状可以包括棒状形状和杆状形状,但本公开不限于此。

59.发光元件ld可以具有与从纳米级到微米级的范围对应的尺寸。例如,发光元件ld

的直径d(或宽度)和长度l各自可以具有在纳米级至微米级的范围内的尺寸,但是本公开不限于此。

60.第一半导体层sec1可以是第一导电半导体层。例如,第一半导体层sec1可以包括n型半导体层。例如,第一半导体层sec1可以包括n型半导体层,其包括inalgan、gan、algan、ingan、aln和inn中的任何一种半导体材料,并且掺杂有诸如si、ge或sn的第一导电掺杂剂。然而,第一半导体层sec1的构成材料不限于此,并且第一半导体层sec1可以由各种其它材料形成。

61.有源层al可以位于第一半导体层sec1上。有源层al可以位于第一半导体层sec1和第二半导体层sec2之间。

62.有源层al可以包括algainp、algap、alingan、ingan和algan中的任何一种。例如,为了使有源层al能够输出红光,有源层al可以包括algainp和/或ingan。为了使有源层al能够发射绿光或蓝光,有源层al可以包括ingan。然而,本公开不限于前述示例。

63.有源层al可以具有单量子阱结构或多量子阱结构。

64.第二半导体层sec2可以位于有源层al上并且包括具有与第一半导体层sec1的类型不同类型的半导体层。例如,第二半导体层sec2可以包括p型半导体层。例如,第二半导体层sec2可以包括p型半导体层,其包括inalgan、gan、algan、ingan、aln和inn中的任何一种半导体材料,并且掺杂有诸如mg的第二导电掺杂剂。然而,用于形成第二半导体层sec2的材料不限于此,并且第二半导体层sec2可以由各种其它材料形成。

65.电极层ell可以形成在第二半导体层sec2上。电极层ell可以包括金属或金属氧化物。根据一些实施方式,电极层ell可以包括cr、ti、al、au、ni及其氧化物或合金以及诸如ito、izo、itzo的透明导电材料中的至少任何一种。

66.如果在发光元件ld的相对端之间施加等于或大于阈值电压的电压,则发光元件ld可以通过有源层al中的电子-空穴对的复合来发光。因为可以基于前述原理控制发光元件ld的发光,所以发光元件ld可以用作各种发光装置以及显示装置dd(参见图3)的像素的光源。

67.发光元件ld还可以包括设置在发光元件ld的表面上的绝缘膜inf。绝缘膜inf可以具有单层结构或多层结构。

68.绝缘膜inf可以允许发光元件ld的具有不同极性的相对端暴露于外部。例如,绝缘膜inf可以允许第一半导体层sec1的定位成与第一端ep1相邻的部分和电极层ell的定位成与第二端ep2相邻的部分暴露于外部。

69.绝缘膜inf可以包括氧化硅(sio

x

)、氮化硅(sin

x

)、氧氮化硅(sio

x

ny)、氧化铝(alo

x

)和氧化钛(tio

x

)中的至少一种。本公开不限于特定示例。

70.绝缘膜inf可以确保发光元件ld的电稳定性。另外,即使在多个发光元件ld彼此相邻地定位的情况下,也可以降低或防止在发光元件ld之间发生不期望的短路的可能性。

71.在一些实施方式中,除了第一半导体层sec1、有源层al、第二半导体层sec2、电极层ell和绝缘膜inf之外,发光元件ld还可以包括附加的其它部件。例如,发光元件ld还可以包括荧光层、有源层、半导体层和/或电极层。

72.图3是示意性示出了根据一些实施方式的显示装置dd的平面图。

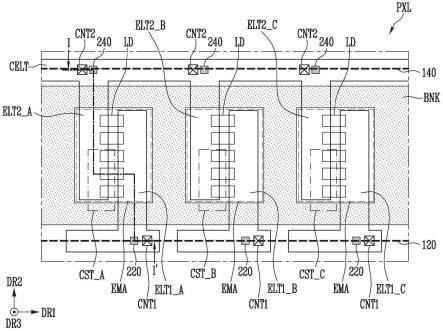

73.显示装置dd可以发光。参考图3,显示装置dd可以包括衬底sub和位于衬底sub上的

像素pxl。在一些实施方式中,显示装置dd还可以包括配置成驱动像素pxl的驱动电路层(例如,扫描驱动器和数据驱动器)、线和焊盘。

74.显示装置dd可以包括显示区域da和非显示区域nda。非显示区域nda可以表示除显示区域da之外的区域。非显示区域nda可以包围显示区域da的至少一部分。在一些实施方式中,取决于实施方式,非显示区域nda可以位于显示区域da中。

75.衬底sub可以形成显示装置dd的基底。衬底sub可以是刚性或柔性的衬底或膜,但不限于特定示例。

76.显示区域da可以表示在其中定位有像素pxl的区域。非显示区域nda可以表示在其中不定位有像素pxl的区域。连接到显示区域da中的像素pxl的驱动电路层、线和焊盘可以位于非显示区域nda中。

77.例如,像素pxl可以布置成条纹或布置结构等,但是本公开不限于此(例如,矩阵结构、结构或rgbg结构)。是韩国三星显示有限公司的注册商标。各种已知的实施方式可以应用于像素pxl的布置结构。

78.在一些实施方式中,像素pxl可以包括第一子像素spxl1、第二子像素spxl2和第三子像素spxl3。第一子像素spxl1、第二子像素spxl2和第三子像素spxl3各自可以是子像素。至少一个第一子像素spxl1、至少一个第二子像素spxl2和至少一个第三子像素spxl3可以形成发射各种颜色的光的一个像素单元。

79.例如,第一子像素spxl1、第二子像素spxl2和第三子像素spxl3各自可以发射具有相应颜色(例如,预定颜色)的光。例如,第一子像素spxl1可以是配置成发射红色(例如,第一颜色)光的红色像素,第二子像素spxl2可以是配置成发射绿色(例如,第二颜色)光的绿色像素,并且第三子像素spxl3可以是配置成发射蓝色(例如,第三颜色)光的蓝色像素。然而,可形成每个像素单元的第一子像素spxl1、第二子像素spxl2和第三子像素spxl3的颜色、类型和/或数量不限于特定示例。

80.图4是示出根据一些实施方式的包括在子像素spxl中的像素电路pxc的电路图。图4针对参考图3描述的第一子像素spxl1、第二子像素spxl2和第三子像素spxl3进行例示。为了便于说明,第一子像素spxl1、第二子像素spxl2和第三子像素spxl3中的任何一个将被指定为子像素spxl。

81.参考图4,子像素spxl可以包括发光元件ld和像素电路pxc。像素电路pxc可以驱动子像素spxl。像素电路pxc可以电连接到发光元件ld。

82.发光元件ld可以连接在第一电力线vdd和第二电力线vss之间。发光元件ld的一端(例如,p型半导体)可以经由像素电路pxc连接到第一电力线vdd,并且发光元件ld的另一端(例如,n型半导体)可以连接到第二电力线vss。

83.在一些实施方式中,当通过像素电路pxc向发光元件ld提供驱动电流时,发光元件ld可以发射具有与驱动电流对应的亮度的光。

84.在一些实施方式中,发光元件ld可以在第一电力线vdd和第二电力线vss之间通过各种连接结构彼此连接。例如,发光元件ld可以仅彼此并联连接,或者仅彼此串联连接。换言之,发光元件ld可以串联/并联组合结构彼此连接。

85.第一电力线vdd和第二电力线vss可以具有不同的电势以允许发光元件ld发射光。第一电力线vdd和第二电力线vss可以具有足以使光能够在子像素spxl的发射周期期间发

射的电势差。例如,第一电力线vdd可以设定成比第二电力线vss的电势高的电势。

86.像素电路pxc可以将第一电力线vdd与发光元件ld连接。像素电路pxc可以包括第一晶体管t1、第二晶体管t2、第三晶体管t3和存储电容器cst。

87.在一些实施方式中,第一晶体管t1的第一电极可以连接到第一电力线vdd,并且其第二电极可以连接到发光元件ld的一个电极(例如,阳极电极)。第一晶体管t1的栅电极可以连接到第一节点n1。第一晶体管t1可以响应于通过第一节点n1施加到其的电压来控制待提供给发光元件ld的电流。

88.在一些实施方式中,第二晶体管t2的第一电极可以连接到数据线dl,并且其第二电极可以连接到第一节点n1。第二晶体管t2的栅电极可以连接到扫描线sl。当从扫描线sl提供扫描信号时,第二晶体管t2可以导通,使得从数据线dl提供的数据信号可以被传输到第一节点n1。

89.在一些实施方式中,第三晶体管t3的第一电极可以连接到感测线senl,并且其第二电极可以连接到第二节点n2。第三晶体管t3的栅电极可以连接到感测信号线sel。在第三晶体管t3响应于从感测信号线sel提供的感测信号而导通的情况下,可以通过感测线senl向第二节点n2提供参考电压。

90.在一些实施方式中,参考电压可以用于将第一晶体管t1的与发光元件ld连接的电极(例如,第一晶体管t1的源电极)的电压初始化或设定成相应的值(例如,预定值)。例如,参考电压可以设定为等于或小于第二电力线vss的电压的电压。

91.在一些实施方式中,在第三晶体管t3响应于从感测信号线sel提供的感测信号而导通的情况下,感测电流可以被传输到感测线senl。

92.在一些实施方式中,感测电流可以用于计算第一晶体管t1的迁移率和阈值电压的变化。

93.存储电容器cst可以连接在第一节点n1(或第一晶体管t1的栅电极)和第二节点n2(或第一晶体管t1的第二电极)之间。存储电容器cst可以存储与第一节点n1和第二节点n2之间的电压的差有关的信息。

94.像素电路pxc的结构不限于图4中所示的结构,并且可以以各种形式实施。此外,尽管图4示出了第一晶体管t1至第三晶体管t3均由n型晶体管形成,但是本公开不限于此。在一些实施方式中,第一晶体管t1至第三晶体管t3各自可以由p型晶体管形成。

95.在下文中,将侧重于根据一些实施方式的显示装置dd的电极的结构进行描述。然而,在描述显示装置dd的电极之前,将首先描述限定在显示装置dd中的堆叠结构。

96.图5是用于描述根据一些实施方式的显示装置dd中包括的堆叠结构的剖视图。

97.参考图5,根据一些实施方式的显示装置dd中包括的堆叠结构可以以设置成通过连续堆叠衬底sub、阻挡电极层bml、缓冲层bfl、有源层act、栅极绝缘层gi、栅电极层ge、第一层间绝缘层ild1、源/漏电极层sdl、第二层间绝缘层ild2、钝化层psv、对准电极层elt、第一接触电极层cne1和第二接触电极层cne2并且然后图案化其至少一部分而形成的结构的形式。

98.衬底sub可以形成显示装置dd的基底,并且可以表示刚性或柔性的衬底或膜。

99.缓冲层bfl可以表示用于减少或防止杂质扩散到包括半导体的有源层act中或用于减少或防止水分渗透的层。在一些实施方式中,缓冲层bfl可以包括氮化硅(sin

x

)、氧化

硅(sio

x

)、氧氮化硅(sio

x

ny)和诸如氧化铝(alo

x

)的金属氧化物中的至少一种。

100.有源层act可以是包括半导体的层。例如,有源层act可以包括多晶硅、低温多晶硅(ltps)、非晶硅和氧化物半导体中的至少一种。在一些实施方式中,有源层act可以形成第一晶体管t1至第三晶体管t3的沟道,并且其接触源/漏电极层sdl的部分可以掺杂有杂质。

101.阻挡电极层bml、栅电极层ge、源/漏电极层sdl、对准电极层elt、第一接触电极层cne1和第二接触电极层cne2各自可以是包括导电材料的层。

102.在一些实施方式中,阻挡电极层bml、栅电极层ge和源/漏电极层sdl各自可以具有单层结构或多层结构。在一些实施方式中,阻挡电极层bml、栅电极层ge和源/漏电极层sdl各自可以包括金(au)、银(ag)、铝(al)、钼(mo)、铬(cr)、钛(ti)、镍(ni)、钕(nd)、铜(cu)和铂(pt)中的任何一种。然而,本公开不限于此。

103.为了将有源层act、栅电极层ge、源/漏电极层sdl和对准电极层elt彼此电分离,栅极绝缘层gi、第一层间绝缘层ild1、第二层间绝缘层ild2和钝化层psv可以插置在相应层之间。在一些实施方式中,期望的电极图案可以通过形成在栅极绝缘层gi、第一层间绝缘层ild1、第二层间绝缘层ild2和钝化层psv中的任何一个中的接触孔(例如,图7的接触部分cnt1和cnt2)彼此电连接。

104.在一些实施方式中,栅极绝缘层gi、第一层间绝缘层ild1、第二层间绝缘层ild2和钝化层psv各自可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氧氮化硅(sio

x

ny)和氧化铝(alo

x

)中的至少一种。在一些实施方式中,栅极绝缘层gi、第一层间绝缘层ild1、第二层间绝缘层ild2和钝化层psv各自可以包括有机材料,并且由单层或多层形成。

105.在一些实施方式中,对准电极层elt可以包括导电材料。例如,对准电极层elt可以包括钼(mo)、镁(mg)、银(ag)、铂(pt)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钛(ti)、铜(cu)和铝(al)中的一种。然而,本公开不限于前述示例。

106.绝缘层可以分别插置在对准电极层elt、第一接触电极层cne1和第二接触电极层cne2之间,使得所述层可以彼此电分离/绝缘。例如,第一接触电极层cne1和第二接触电极层cne2可以通过第一绝缘层(参考图12的“ins1”)与对准电极层elt分离开。第一接触电极层cne1和第二接触电极层cne2可以通过第三绝缘层(参考图12的“ins3”)彼此分离开。

107.在下文中,将参考图6至图8侧重于设置在显示装置dd中的电极来描述根据一些实施方式的显示装置dd。

108.图6至图8是示出根据一些实施方式的像素pxl中包括的电极的布局图。

109.图6至图8示出了像素pxl的电极。图6至图8示出了位于相同区域中的不同层(例如,在平面图中)。

110.图6示出了已参考图5描述的阻挡电极层bml、有源层act和栅电极层ge。在图6中,用于将不同电极图案彼此电连接的接触孔被呈现为正方形形状。

111.图7示出了以上参考图5描述的源/漏电极层sdl和对准电极层elt。图7进一步示出了根据一些实施方式的堤部bnk。在图7中,源/漏电极层sdl由粗实线指示。此外,配置成将不同的电极图案彼此电连接的接触部分cnt1和cnt2由以

×

标记的方框指示。

112.图8示出了已参考图5描述的对准电极层elt、第一接触电极层cne1和第二接触电极层cne2。在图8中,用于将不同电极图案彼此电连接的接触部件220和240被呈现为正方形形状。

113.在一些实施方式中,第一晶体管t1至第三晶体管t3、存储电容器cst、数据线dl、扫描线sl、感测线senl、第一电力线vdd和第二电力线vss可以被包括在像素pxl中且位于像素pxl中。

114.如以上参考图4所述,第一晶体管t1至第三晶体管t3和存储电容器cst可以形成一个像素电路pxc。在图6中,示出了第一晶体管t1至第三晶体管t3和存储电容器cst形成三个不同像素电路pxc的结构。

115.第一晶体管t1可以包括第1_a晶体管t1_a、第1_b晶体管t1_b和第1_c晶体管t1_c。这里,第1_a晶体管t1_a可以表示包括在第一子像素spxl1的像素电路pxc中的第一晶体管t1。第1_b晶体管t1_b可以表示包括在第二子像素spxl2的像素电路pxc中的第一晶体管t1。第1_c晶体管t1_c可以表示包括在第三子像素spxl3的像素电路pxc中的第一晶体管t1。

116.第二晶体管t2可以包括第2_a晶体管t2_a、第2_b晶体管t2_b和第2_c晶体管t2_c。这里,第2_a晶体管t2_a可以表示包括在第一子像素spxl1的像素电路pxc中的第二晶体管t2。第2_b晶体管t2_b可以表示包括在第二子像素spxl2的像素电路pxc中的第二晶体管t2。第2_c晶体管t2_c可以表示包括在第三子像素spxl3的像素电路pxc中的第二晶体管t2。

117.第三晶体管t3可以包括第3_a晶体管t3_a、第3_b晶体管t3_b和第3_c晶体管t3_c。这里,第3_a晶体管t3_a可以表示包括在第一子像素spxl1的像素电路pxc中的第三晶体管t3。第3_b晶体管t3_b可以表示包括在第二子像素spxl2的像素电路pxc中的第三晶体管t3。第3_c晶体管t3_c可以表示包括在第三子像素spxl3的像素电路pxc中的第三晶体管t3。

118.存储电容器cst可以包括第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c。

119.第一存储电容器cst_a可以表示包括在第一子像素spxl1的像素电路pxc中的存储电容器cst。第二存储电容器cst_b可以表示包括在第二子像素spxl2的像素电路pxc中的存储电容器cst。第三存储电容器cst_c可以表示包括在第三子像素spxl3的像素电路pxc中的存储电容器cst。

120.在一些实施方式中,第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c可以在第一方向dr1上连续定位。

121.例如,第一存储电容器cst_a可以在第一方向dr1上与第二存储电容器cst_b和第三存储电容器cst_c间隔开。第二存储电容器cst_b可以在第一方向dr1上与第一存储电容器cst_a和第三存储电容器cst_c间隔开。第三存储电容器cst_c可以在第一方向dr1上与第一存储电容器cst_a和第二存储电容器cst_b间隔开。

122.这里,第一方向dr1可以表示第一子像素spxl1、第二子像素spxl2和第三子像素spxl3沿其连续布置的方向。在这种情况下,第一子像素spxl1、第二子像素spxl2和第三子像素spxl3沿其布置的方向可以与第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c沿其布置的方向相同。

123.在一些实施方式中,第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c可以在与第一子像素spxl1、第二子像素spxl2和第三子像素spxl3沿其布置的布置方向(例如,第一方向dr1)相交的方向(例如,第二方向dr2)上延伸。

124.在一些实施方式中,第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c各自可以大致具有在第二方向dr2上延伸的形状。例如,第一存储电容器cst_a、

第二存储电容器cst_b和第三存储电容器cst_c中的每个相对于第一方向dr1的最大长度或宽度可以小于其相对于第二方向dr2的最大长度。

125.例如,第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c中的每个相对于第一方向dr1的第一最大长度或宽度202可以小于第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c中的每个相对于第二方向dr2的第二最大长度204。

126.扫描线sl可以在第一方向dr1上延伸。在一些实施方式中,像素pxl的扫描线sl可以在第二方向dr2上与第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c间隔开。

127.数据线dl可以包括第一数据线dl_a、第二数据线dl_b和第三数据线dl_c。这里,第一数据线dl_a可以表示包括在第一子像素spxl1的像素电路pxc中的数据线dl。第二数据线dl_b可以表示包括在第二子像素spxl2的像素电路pxc中的数据线dl。第三数据线dl_c可以表示包括在第三子像素spxl3的像素电路pxc中的数据线dl。

128.在一些实施方式中,数据线dl可以在第二方向dr2上延伸。数据线dl可以在第一方向dr1上彼此间隔开。例如,数据线dl可以在与第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c沿其延伸的方向相同的方向上延伸。数据线dl可以在与第一子像素spxl1、第二子像素spxl2和第三子像素spxl3沿其彼此间隔开的方向相交的方向上延伸。

129.参考图7,在一些实施方式中,感测线senl可以在第一方向dr1上延伸。感测线senl可以在与第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c沿其延伸的方向(例如,第二方向dr2)相交的方向(例如,第一方向dr1)上延伸。感测线senl可以在与第一子像素spxl1、第二子像素spxl2和第三子像素spxl3沿其彼此间隔开的方向相同的方向上延伸。

130.在一些实施方式中,对准电极层elt可以包括第一电极elt1、第二电极elt2和第三电极elt3以及公共连接电极celt。第一电极elt1可以包括第1_a电极elt1_a、第1_b电极elt1_b和第1_c电极elt1_c。第二电极elt2可以包括第2_a电极elt2_a、第2_b电极elt2_b和第2_c电极elt2_c。第三电极elt3可以包括第3_a电极elt3_a、第3_b电极elt3_b和第3_c电极elt3_c。

131.在一些实施方式中,第1_a电极elt1_a、第2_a电极elt2_a和第3_a电极elt3_a可以是第一子像素spxl1的对准电极。例如,基于分别提供给第1_a电极elt1_a、第2_a电极elt2_a和第3_a电极elt3_a的电信号,第一子像素spxl1的发光元件ld可以定位在将在其中形成第一子像素spxl1的区域中。

132.在一些实施方式中,第1_b电极elt1_b、第2_b电极elt2_b和第3_b电极elt3_b可以是第二子像素spxl2的对准电极。例如,基于分别提供给第1_b电极elt1_b、第2_b电极elt2_b和第3_b电极elt3_b的电信号,第二子像素spxl2的发光元件ld可以定位在将在其中形成第二子像素spxl2的区域中。

133.在一些实施方式中,第1_c电极elt1_c、第2_c电极elt2_c和第3_c电极elt3_c可以是第三子像素spxl3的对准电极。例如,基于分别提供给第1_c电极elt1_c、第2_c电极elt2_c和第3_c电极elt3_c的电信号,第三子像素spxl3的发光元件ld可以定位在将在其中形成第三子像素spxl3的区域中。

134.参考图8,在一些实施方式中,像素pxl可以包括开口区域500。开口区域500可以表示在将向其提供阳极信号的对准电极层elt之间分离开的区域。例如,开口区域500可以表示第1_a电极elt1_a和第1_b电极elt1_b之间的区域。开口区域500可以表示第1_b电极elt1_b和第1_c电极elt1_c之间的区域。开口区域500可以通过在整个表面上沉积对准电极层elt并且然后通过蚀刻设置在将设置开口区域500的位置处的电极来设置。当设置开口区域500时,将向其提供阳极信号的电极部件可以彼此电划分,使得第一子像素spxl1、第二子像素spxl2和第三子像素spxl3可以被单独驱动。

135.在一些实施方式中,第一接触部分cnt1可以包括第1_1接触部分cnt1_1、第1_2接触部分cnt1_2和第1_3接触部分cnt1_3。第1_1接触部分cnt1_1、第1_2接触部分cnt1_2和第1_3接触部分cnt1_3可以彼此间隔开,且开口区域500设置在它们之间。

136.在一些实施方式中,源/漏电极层sdl的电极部件可以设置成网状结构,以便形成通过其提供电信号的电极路径。例如,包括在源/漏电极层sdl中的第一电力线vdd可以在第一方向dr1上延伸。源/漏电极层sdl的至少一部分可以具有在第二方向dr2上延伸的形状。

137.第一电力线vdd可以通过第一接触部分cnt1电连接到第一电极elt1。第一电力线vdd可以通过第一接触部分cnt1向第一电极elt1提供电信号(例如,阳极信号)。

138.例如,第一电力线vdd的一部分可以通过第1_1接触部分cnt1_1电连接到第1_a电极elt1_a。第一电力线vdd的一部分可以通过第1_2接触部分cnt1_2电连接到第1_b电极elt1_b。第一电力线vdd的一部分可以通过第1_3接触部分cnt1_3电连接到第1_c电极elt1_c。

139.第二电力线vss可以通过第二接触部分cnt2电连接到公共连接电极celt。第二电力线vss可以通过第二接触部分cnt2向公共连接电极celt提供电信号(例如,阴极信号)。在一些实施方式中,公共连接电极celt可以电连接到第二电极elt2和第三电极elt3。因此,第二电力线vss可以向第二电极elt2和第三电极elt3提供电信号(例如,阴极信号)。

140.例如,第二电力线vss可以通过第二接触部分cnt2和公共连接电极celt向第2_a电极elt2_a、第2_b电极elt2_b和第2_c电极elt2_c提供电信号。第二电力线vss可以通过第二接触部分cnt2和公共连接电极celt向第3_a电极elt3_a、第3_b电极elt3_b和第3_c电极elt3_c提供电信号。

141.第一电力线vdd和第二电力线vss可以在第一方向dr1上延伸。例如,第一电力线vdd和第二电力线vss可以在与第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c沿其延伸的方向交叉的方向上延伸。第一电力线vdd和第二电力线vss可以在第一子像素spxl1、第二子像素spxl2和第三子像素spxl3沿其彼此间隔开的方向上延伸。

142.在一些实施方式中,在第一方向dr1上延伸的第一电力线vdd可以位于第一接触部分cnt1与第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c之间。

143.例如,第一电力线vdd可以位于第一存储电容器cst_a和第1_1接触部分cnt1_1之间。第一电力线vdd可以位于第二存储电容器cst_b和第1_2接触部分cnt1_2之间。第一电力线vdd可以位于第三存储电容器cst_c和第1_3接触部分cnt1_3之间。

144.这里,第一子像素spxl1的第1_a晶体管t1_a可以通过第1_1接触部分cnt1_1电连接到第1_a电极elt1_a。第二子像素spxl2的第1_b晶体管t1_b可以通过第1_2接触部分cnt1_2电连接到第1_b电极elt1_b。第三子像素spxl3的第1_c晶体管t1_c可以通过第1_3接

触部分cnt1_3电连接到第1_c电极elt1_c。

145.在一些实施方式中,可以设置多个第一接触部分cnt1,并且多个第一接触部分cnt1在第一方向dr1上连续布置。

146.在一些实施方式中,在平面图中,第1_1接触部分cnt1_1、第1_2接触部分cnt1_2和第1_3接触部分cnt1_3可以不与第一电力线vdd重叠。例如,第1_1接触部分cnt1_1、第1_2接触部分cnt1_2和第1_3接触部分cnt1_3可以不与第一电力线vdd重叠,并且可以电连接到形成在源/漏电极层sdl上的电极图案。电极图案可以通过接触孔(例如,预定接触孔)电连接到第一电力线vdd。在一些实施方式中,第1_1接触部分cnt1_1、第1_2接触部分cnt1_2和第1_3接触部分cnt1_3可以通过在与第一电力线vdd相同的层处的电极图案电连接到第一电力线vdd。因此,第1_1接触部分cnt1_1、第1_2接触部分cnt1_2和第1_3接触部分cnt1_3可以在其中定位有发光元件ld的区域的周边中位于彼此间隔开的位置处。在其中定位有发光元件ld的区域可以具有足够大的表面面积。

147.然而,本公开不限于前述示例。在一些实施方式中,在平面图中,第一接触部分cnt1中的每个可以与第一电力线vdd重叠。在一些实施方式中,在平面图中,第一接触部分cnt1中的任何一个可以与第1_a电极elt1_a重叠,并且另一个可以与第1_b电极elt1_b重叠,并且其余一个可以与第1_c电极elt1_c重叠。

148.在一些实施方式中,第1_1接触部分cnt1_1、第1_2接触部分cnt1_2和第1_3接触部分cnt1_3沿其布置的方向(例如,第一方向dr1)可以与第一电力线vdd沿其延伸的方向基本上平行或相同。

149.可以设置多个第二接触部分cnt2,并且多个第二接触部分cnt2在第一方向dr1上连续布置。在平面图中,第二接触部分cnt2中的每个可以与第二电力线vss重叠。在一些实施方式中,在平面图中,第二接触部分cnt2可以与公共连接电极celt重叠。

150.在一些实施方式中,第一接触部分cnt1和第二接触部分cnt2可以位于由堤部bnk限定的第二开口op2中。

151.在一些实施方式中,存储电容器cst可以位于其上布置有第一接触部分cnt1的线与其上布置有第二接触部分cnt2的线之间。下面将参考图11对其进行详细描述。

152.堤部bnk可以以一图案(例如,预定图案)布置,并且可以限定发射区域ema和非发射区域nea。堤部bnk可以包括有机材料或无机材料,但不限于特定示例。

153.在一些实施方式中,发射区域ema可以是其中不定位有堤部bnk的区域,并且可以表示其中定位有发光元件ld并且从其发射光的区域。非发射区域nea可以表示在其中定位有堤部bnk的区域。例如,在平面图中,堤部bnk和发射区域ema可以不彼此重叠。在平面图中,堤部bnk和非发射区域nea可以彼此重叠。

154.堤部bnk可以具有在显示装置dd的显示方向(例如,第三方向dr3)上突出的形状,并且可以形成开口op。

155.在一些实施方式中,开口op可以包括第一开口op1和第二开口op2。第一开口op1可以是其中不定位有堤部bnk的区域,并且可以包括其中定位有发光元件ld的区域。第二开口op2可以是其中不定位有堤部bnk的区域,并且可以包括其中不定位有发光元件ld的区域。第二开口op2可以具有在第一方向dr1上延伸的形状。在一些实施方式中,第一接触部分cnt1和第二接触部分cnt2可以位于第二开口op2中。

156.在一些实施方式中,第一开口op1可以形成为提供空间,该空间配置成在执行用于传递发光元件ld的喷墨工艺时接收流体。例如,在形成堤部bnk之后,可以在由堤部bnk限定的空间中提供包括发光元件ld和溶剂的油墨。此后,可以通过执行形成电场的工艺来布置发光元件ld。

157.在一些实施方式中,可以形成多个第一开口op1。第一开口op1可以分别设置在第一子像素spxl1、第二子像素spxl2和第三子像素spxl3中。例如,第一开口op1中的任何一个可以形成第一子像素spxl1的发射区域ema。第一开口op1中的另一个可以形成第二子像素spxl2的发射区域ema。第一开口op1中的其余一个可以形成第三子像素spxl3的发射区域ema。例如,在平面图中,第一开口op1可以与发射区域ema重叠。

158.图8示出了在第一子像素spxl1、第二子像素spxl2和第三子像素spxl3中的每个中形成两个线路径区域的接触电极层cne1和cne2的结构。然而,在一些实施方式中,可以在第一子像素spxl1、第二子像素spxl2和第三子像素spxl3中的每个中提供形成四个线路径区域的接触电极层cne1和cne2的结构。下面将参考图9和图10对其进行详细描述。

159.第一接触电极层cne1可以位于对准电极层elt上。在一些实施方式中,第一接触电极层cne1可以包括第1_a接触电极cne1_a、第1_b接触电极cne1_b和第1_c接触电极cne1_c。

160.第一接触电极层cne1可以将每个发光元件ld分别电连接到对准电极层elt中的一个。

161.例如,第1_a接触电极cne1_a可以将第1_a电极elt1_a与位于第1_a电极elt1_a和第2_a电极elt2_a上的发光元件ld电连接,并且可以将第3_a电极elt3_a与位于第1_a电极elt1_a和第3_a电极elt3_a上的发光元件ld电连接。

162.第1_b接触电极cne1_b可以将第1_b电极elt1_b与位于第1_b电极elt1_b和第2_b电极elt2_b上的发光元件ld电连接,并且可以将第3_b电极elt3_b与位于第1_b电极elt1_b和第3_b电极elt3_b上的发光元件ld电连接。

163.第1_c接触电极cne1_c可以将第1_c电极elt1_c与位于第1_c电极elt1_c和第2_c电极elt2_c上的发光元件ld电连接,并且可以将第3_c电极elt3_c与位于第1_c电极elt1_c和第3_c电极elt3_c上的发光元件ld电连接。

164.第二接触电极层cne2可以位于对准电极层elt上。第二接触电极层cne2可以位于第一接触电极层cne1上。第二接触电极层cne2可以将每个发光元件ld电连接到对准电极层elt中的任何一个。第二接触电极层cne2可以包括第2_a接触电极cne2_a、第2_b接触电极cne2_b和第2_c接触电极cne2_c。

165.第二接触电极层cne2可以将每个发光元件ld电连接到对准电极层elt中的任何一个。

166.在一些实施方式中,第2_a接触电极cne2_a可以包括第一部件222和第二部件224。第2_a接触电极cne2_a的第一部件222和第二部件224可以通过相同的工艺形成(或设置)并且彼此间隔开。这里,第2_a接触电极cne2_a的第一部件222可以将第1_a电极elt1_a与位于第1_a电极elt1_a和第3_a电极elt3_a上的发光元件ld电连接。第2_a接触电极cne2_a的第二部件224可以将第2_a电极elt2_a和公共连接电极celt与位于第1_a电极elt1_a和第2_a电极elt2_a上的发光元件ld电连接。

167.在一些实施方式中,第2_b接触电极cne2_b可以包括第一部件232和第二部件234。

第2_b接触电极cne2_b的第一部件232和第二部件234可以通过相同的工艺形成(或设置)并且彼此间隔开。这里,第2_b接触电极cne2_b的第一部件232可以将第1_b电极elt1_b与位于第1_b电极elt1_b和第3_b电极elt3_b上的发光元件ld电连接。第2_b接触电极cne2_b的第二部件234可以将第2_b电极elt2_b和公共连接电极celt与位于第1_b电极elt1_b和第2_b电极elt2_b上的发光元件ld电连接。

168.在一些实施方式中,第2_c接触电极cne2_c可以包括第一部件242和第二部件244。第2_c接触电极cne2_c的第一部件242和第二部件244可以通过相同的工艺形成(或设置)并且彼此间隔开。第2_c接触电极cne2_c的第一部件242可以将第1_c电极elt1_c与位于第1_c电极elt1_c和第3_c电极elt3_c上的发光元件ld电连接。第2_c接触电极cne2_c的第二部件244可以将第2_c电极elt2_c和公共连接电极celt与位于第1_c电极elt1_c和第2_c电极elt2_c上的发光元件ld电连接。

169.在一些实施方式中,第二接触电极层cne2可以通过接触部件220和240电连接到对准电极层elt。

170.例如,第2_a接触电极cne2_a的第一部件222可以通过第一接触部件220电连接到第1_a电极elt1_a。第2_a接触电极cne2_a的第二部件224可以通过第二接触部件240电连接到公共连接电极celt。

171.第2_b接触电极cne2_b的第一部件232可以通过第一接触部件220电连接到第1_b电极elt1_b。第2_b接触电极cne2_b的第二部件234可以通过第二接触部件240电连接到公共连接电极celt。

172.第2_c接触电极cne2_c的第一部件242可以通过第一接触部件220电连接到第1_c电极elt1_c。第2_c接触电极cne2_c的第二部件244可以通过第二接触部件240电连接到公共连接电极celt。

173.接下来,将参考图9和图10描述根据一些实施方式的发光元件ld的布置结构。可能与以上描述的实施方式的描述相同的描述将被简化或省略。

174.图9和图10是示出发光元件ld的布置结构的平面图。为了便于说明,将基于第一子像素spxl1来描述发光元件ld的布置结构。

175.图9是示出根据一些实施方式的第一子像素spxl1的平面图,并且示出在三个对准电极elt1_a、elt2_a和elt3_a上设置两个线路径区域422和424的一些实施方式。图9中所示的平面结构可以通过简化以上参考图8描述的结构来获得。

176.这里,线路径区域422和424各自可以表示在其中发光元件ld在一个方向上布置的区域。

177.在一些实施方式中,第一子像素spxl1可以包括第一线路径区域422和第二线路径区域424。

178.在第一线路径区域422中,每个相应的发光元件ld的一端可以通过第1_a接触电极cne1_a的一部分电连接到第1_a电极elt1_a,并且发光元件ld的另一端可以通过第2_a接触电极cne2_a的第二部件224电连接到第2_a电极elt2_a。

179.在第二线路径区域424中,每个相应的发光元件ld的一端可以通过第1_a接触电极cne1_a的另一部分电连接到第3_a电极elt3_a,并且发光元件ld的另一端可以通过第2_a接触电极cne2_a的第一部件222电连接到第1_a电极elt1_a。

180.图10是示出了根据一些实施方式的第一子像素spxl1的平面图,并且图10示出了在三个对准电极elt1_a、elt2_a和elt3_a上设置四个线路径区域522、524、526和528的一些实施方式。这里,线路径区域522、524、526和528各自可以表示在其中发光元件ld在一个方向上布置的区域。

181.在一些实施方式中,第一子像素spxl1可以包括第一线路径区域522、第二线路径区域524、第三线路径区域526和第四线路径区域528。

182.在第一线路径区域522中,每个相应的发光元件ld的一端可以通过第2_a接触电极cne2_a的第一部件322电连接到第2_a电极elt2_a和公共连接电极celt,并且发光元件ld的另一端可以通过第1_a接触电极cne1_a的一部分电连接到第1_a电极elt1_a。

183.在第二线路径区域524中,每个相应的发光元件ld的一端可以通过第2_a接触电极cne2_a的第二部件324电连接到第1_a电极elt1_a,并且发光元件ld的另一端可以通过第1_a接触电极cne1_a的一部分电连接到第2_a电极elt2_a和公共连接电极celt。

184.在第三线路径区域526中,每个相应的发光元件ld的一端可以通过第2_a接触电极cne2_a的第三部件326电连接到第1_a电极elt1_a,并且发光元件ld的另一端可以通过第1_a接触电极cne1_a的一部分电连接到第3_a电极elt3_a和公共连接电极celt。

185.在第四线路径区域528中,每个相应的发光元件ld的一端可以通过第2_a接触电极cne2_a的第二部件324电连接到第3_a电极elt3_a和公共连接电极celt,并且发光元件ld的另一端可以通过第1_a接触电极cne1_a的一部分电连接到第1_a电极elt1_a。

186.实验上,在子像素spxl中的线路径区域的数量增加的情况下,可以增强子像素spxl的亮度。例如,根据参考图10描述的一些实施方式的子像素spxl的亮度效率可以高于根据参考图9描述的一些实施方式的子像素spxl的亮度效率。然而,由于电极结构的设置,根据以上参考图10描述的一些实施方式,可能适合于确保具有足够长度以提供子像素spxl的线路径。

187.在一些实施方式中,由于存储电容器cst、第一接触部分cnt1、第二接触部分cnt2和第一电力线vdd之间的设置关系,可以确保足够的线路径长度,从而可以容易地提供包括多个线路径区域的结构。因此,在一些实施方式中,可以进一步改善子像素spxl的亮度。

188.在下文中,将参考图11至图14更详细地描述根据一些实施方式的像素pxl的结构。

189.图11是示出根据一些实施方式的像素pxl的平面图。

190.在一些实施方式中,对于第一子像素spxl1、第二子像素spxl2和第三子像素spxl3中的每个,第一接触部分cnt1和第二接触部分cnt2可以定位成比发射区域ema更向外。由于第一接触部分cnt1和第二接触部分cnt2位于外部区域中,所以可以充分地确保可在其中定位有发光元件ld的区域。下面将描述与之相关的结构特征。

191.所设置的多个第一接触部分cnt1中的至少一些可以沿着在第一方向dr1上延伸的第一线120定位。这里,词语“第一接触部分cnt1沿着第一线120定位”可以意指具有第一接触部分cnt1在第一方向dr1上示意性地布置的趋势。

192.所设置的多个第二接触部分cnt2中的至少一些可以沿着在第一方向dr1上延伸的第二线140定位。这里,词语“第二接触部分cnt2沿着第二线140定位”可以意指具有第二接触部分cnt2在第一方向dr1上示意性地布置的趋势。

193.这里,第一线120和第二线140可以彼此间隔开足够的距离。因此,相对于第二方向

dr2,可以确保在其中布置有发光元件ld的区域(例如,发射区域ema)的足够长度。在这种情况下,更多数量的发光元件ld可以位于发射区域ema中,从而可以增强像素pxl的发射性能。

194.在一些实施方式中,在平面图中,第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c可以不与第一接触部分cnt1和第二接触部分cnt2重叠。第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c可以位于第一接触部分cnt1沿其布置的第一线120(其可以是假想的)和第二接触部分cnt2沿其布置的第二线140(其可以是假想的)之间。在平面图中,第一线120和第二线140可能不与堤部bnk重叠。

195.在一些实施方式中,第一线120和第二线140沿其延伸的方向可以与存储电容器cst_a、cst_b和cst_c沿其延伸的方向相交(或可以基本上与之垂直)。

196.在一些实施方式中,第一线120和第二线140沿其延伸的方向可以与存储电容器cst_a、cst_b和cst_c沿其连续布置的方向相同(或基本上与之平行)。

197.在一些实施方式中,在平面图中,第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c中的一些可以不与堤部bnk重叠。例如,第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c中的至少一些可以定位成与在其中不定位有堤部bnk的发射区域ema重叠。

198.在一些实施方式中,如上所述,第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c各自可以具有其在第二方向dr2上的长度大于其在第一方向dr1上的长度的形状。第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c可在第一方向dr1上连续定位。

199.根据前述结构,可在其中布置发光元件ld的发射区域ema可以具有足够大的尺寸。

200.实验上,在第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c各自大致具有在第一方向dr1上延伸的形状的情况下,第一接触部分cnt1和第二接触部分cnt2可以定位成与在其中布置有发光元件ld的区域相邻,以避免形成另外不必要的电极结构。换言之,可以减小第一线120和第二线140之间的距离。在这种情况下,可以减小可在其中定位有发光元件ld的区域。在每个第一接触部分cnt1和每个第二接触部分cnt2形成在钝化层psv(其是下绝缘层之一)上的情况下,可以在形成第一接触部分cnt1和第二接触部分cnt2中的每个的相邻区域中形成凹槽,从而可以在相邻区域与在其中未形成第一接触部分cnt1和第二接触部分cnt2的区域之间形成台阶差。因此,可能适合于将发光元件ld定位在与第一接触部分cnt1和第二接触部分cnt2间隔开的位置处。

201.然而,在一些实施方式中,因为第一存储电容器cst_a、第二存储电容器cst_b和第三存储电容器cst_c中的每个具有在第二方向dr2(其是第一接触部分cnt1和第二接触部分cnt2沿其彼此间隔开的方向)上延伸的形状,所以第一接触部分cnt1和第二接触部分cnt2可以彼此间隔开足够的距离并且位于外部区域中。因此,可以确保可在其中定位有发光元件ld的足够大的区域。

202.在一些实施方式中,每个第一接触部分cnt1在平面图中可以不与堤部bnk重叠。第一接触部分cnt1可以在第二方向dr2上与发射区域ema间隔开。第一接触部分cnt1可以在第二方向dr2上与堤部bnk间隔开。每个第二接触部分cnt2在平面图中可能不与堤部bnk重叠。第二接触部分cnt2可以在第二方向dr2上与发射区域ema间隔开。第二接触部分cnt2可以在第二方向dr2上与堤部bnk间隔开。因此,由堤部bnk限定的发射区域ema可以足够大。

203.因此,根据本公开,发射区域ema可以足够大,使得可以定位在发射区域ema中的发光元件ld的数量可以增加。在这种情况下,可以降低提供所需亮度所需的电力,从而可以减轻发热和功耗,由此可以改善发射效率。

204.具体地,为了提供根据以上参考图10描述的一些实施方式的像素pxl,需要充分地增加发光元件ld所位于的每个线路径的长度。根据本公开,因为发光元件ld所位于的线路径的长度可以延伸,所以像素pxl的结构可以实施为使得可以提供多个线路径区域。因此,可以进一步改善显示装置dd的亮度。

205.图12是沿着图11的线i-i'截取的剖视图。图12是示出根据一些实施方式的第一子像素spxl1的剖面结构的视图。为了便于说明,将基于第一子像素spxl1、第二子像素spxl2和第三子像素spxl3中的第一子像素spxl1参考图12进行下面的描述。取决于实施方式,基于第一子像素spxl1描述的技术特征可以应用于第二子像素spxl2和第三子像素spxl3。将省略或简化将与以上描述的实施方式的描述相同的描述。

206.参考图12,第一子像素spxl1可以包括衬底sub、像素电路层pcl和显示元件层dpl。

207.衬底sub可以设置为基础表面。像素电路层pcl和显示元件层dpl可以位于衬底sub上。

208.像素电路层pcl可以位于衬底sub上。像素电路层pcl可以包括缓冲层bfl、第1_a晶体管t1_a、栅极绝缘层gi、第一层间绝缘层ild1、第二层间绝缘层ild2、第一存储电容器cst_a、电力线pl、钝化层psv、第一接触部分cnt1和第二接触部分cnt2。

209.缓冲层bfl可以位于衬底sub上。缓冲层bfl可以减少或防止杂质另外从外部扩散。

210.第1_a晶体管t1_a可以是薄膜晶体管。在一些实施方式中,第1_a晶体管t1_a可以是驱动晶体管。

211.第1_a晶体管t1_a可以电连接到发光元件ld。第1_a晶体管t1_a可以通过第一接触部分cnt1电连接到第1_a电极elt1_a。

212.第1_a晶体管t1_a可以包括有源层act、第一晶体管电极te1、第二晶体管电极te2和栅电极层ge。

213.有源层act可以表示半导体层。有源层act可以位于缓冲层bfl上。

214.有源层act可以包括接触第一晶体管电极te1的第一接触区域和接触第二晶体管电极te2的第二接触区域。第一接触区域和第二接触区域中的每个可以是掺杂有杂质的半导体图案。第一接触区域和第二接触区域之间的区域可以是沟道区域。沟道区域可以是不掺杂杂质的本征半导体图案。

215.栅电极层ge可以位于栅极绝缘层gi上。栅电极层ge的位置可以对应于有源层act的沟道区域的位置。例如,栅电极层ge可以位于有源层act的沟道区域上,且栅极绝缘层gi插置在其间。

216.栅极绝缘层gi可以位于有源层act上。栅极绝缘层gi可以包括无机材料。

217.第一层间绝缘层ild1可以位于栅电极层ge上。

218.第一晶体管电极te1和第二晶体管电极te2可以位于第一层间绝缘层ild1上。第一晶体管电极te1可以穿过栅极绝缘层gi和第一层间绝缘层ild1与有源层act的第一接触区域接触。第二晶体管电极te2可以穿过栅极绝缘层gi和第一层间绝缘层ild1与有源层act的第二接触区域接触。例如,第一晶体管电极te1可以是漏电极,并且第二晶体管电极te2可以

是源电极,但是本公开不限于此。

219.在一些实施方式中,第一晶体管电极te1和第二晶体管电极te2各自可以包括导电材料。例如,第一晶体管电极te1和第二晶体管电极te2各自可以包括诸如钼(mo)、镁(mg)、银(ag)、铂(pt)、钯(pd)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钛(ti)、铜(cu)、铝(al)的金属和/或其合金。例如,第一晶体管电极te1和第二晶体管电极te2各自可以具有包括钛和铜的多层结构。

220.第二层间绝缘层ild2可以位于第一晶体管电极te1和第二晶体管电极te2上。

221.第一存储电容器cst_a可以包括第一存储板320和第二存储板340。第一存储板320和第二存储板340可以彼此面对,且第一层间绝缘层ild1插置在其间。第一存储板320可以位于栅极绝缘层gi上。第二存储板340可以位于第一层间绝缘层ild1上。

222.电力线pl可以位于第一层间绝缘层ild1上。电力线pl可以通过第二接触部分cnt2和公共连接电极celt与第2_a电极elt2_a电连接。

223.钝化层psv可以位于第二层间绝缘层ild2上。在一些实施方式中,与第一晶体管电极te1的一个区域连接的第一接触部分cnt1和与电力线pl的一个区域连接的第二接触部分cnt2可以形成在钝化层psv中。第一接触部分cnt1和第二接触部分cnt2各自可以穿过钝化层psv和第二层间绝缘层ild2。

224.显示元件层dpl可以位于像素电路层pcl上。显示元件层dpl可以包括第一绝缘图案inp1、第二绝缘图案inp2、堤部bnk、第1_a电极elt1_a、第2_a电极elt2_a、公共连接电极celt、第一绝缘层ins1、发光元件ld、第二绝缘层ins2、第1_a接触电极cne1_a、第三绝缘层ins3、第2_a接触电极cne2_a和第四绝缘层ins4。

225.第一绝缘图案inp1和第二绝缘图案inp2可以在衬底sub的厚度方向上(例如,在第三方向dr3上)突出。在平面图中,第一绝缘图案inp1和第二绝缘图案inp2可以布置成包围其中定位有发光元件ld的区域的形状。第一绝缘图案inp1和第二绝缘图案inp2各自可以包括有机材料或无机材料。

226.第1_a电极elt1_a可以位于第一绝缘图案inp1上。第2_a电极elt2_a可以位于第二绝缘图案inp2上。第1_a电极elt1_a和第2_a电极elt2_a可以将从发光元件ld提供的光反射到显示装置dd的显示方向(例如,第三方向dr3)上。因此,可以提高第一子像素spxl1的光效率。

227.堤部bnk可以位于第一绝缘层ins1上。堤部bnk可以在衬底sub的厚度方向上突出。其中定位有发光元件ld的区域可以设置在堤部bnk之间。

228.第1_a电极elt1_a可以设置在钝化层psv上。在一些实施方式中,第1_a电极elt1_a的一部分可以位于第一绝缘图案inp1上。

229.第1_a电极elt1_a可以将第1_a晶体管t1_a与第1_a接触电极cne1_a电连接。第1_a电极elt1_a可以通过第一接触部分cnt1与第1_a晶体管t1_a电连接。例如,第1_a电极elt1_a可以向第1_a接触电极cne1_a提供阳极信号。

230.第2_a电极elt2_a可以设置在钝化层psv上。在一些实施方式中,第2_a电极elt2_a的一部分可以位于第二绝缘图案inp2上。

231.第2_a电极elt2_a可以通过公共连接电极celt电连接到电力线pl。

232.公共连接电极celt可以位于钝化层psv上。公共连接电极celt可以与第2_a电极

elt2_a一体地形成。

233.公共连接电极celt可以向第2_a接触电极cne2_a提供电信号(例如,阴极信号)。公共连接电极celt可以通过第二接触部分cnt2电连接到电力线pl。公共连接电极celt可以将电力线pl电连接到第2_a电极elt2_a。

234.第一绝缘层ins1可以位于钝化层psv上。第一绝缘层ins1可以覆盖第1_a电极elt1_a和第2_a电极elt2_a。第一绝缘层ins1可以稳定电极部件之间的连接并减少外部影响。第一绝缘层ins1可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氧氮化硅(sio

x

ny)和氧化铝(alo

x

)中的任何一种。

235.发光元件ld可以位于第一绝缘层ins1上。发光元件ld各自可以基于从第1_a接触电极cne1_a和第2_a接触电极cne2_a提供的电信号发光。

236.在一些实施方式中,可以基于由提供给第1_a电极elt1_a和第2_a电极elt2_a的电信号形成的电场来布置发光元件ld。例如,第一电信号可以提供给第1_a电极elt1_a,并且第二电信号可以提供给第2_a电极elt2_a。第一电信号和第二电信号可以在第1_a电极elt1_a和第2_a电极elt2_a之间形成电场。可以通过由电场产生的外力(例如,介电电泳(dep)力)来布置发光元件ld。

237.第二绝缘层ins2可以位于发光元件ld上。第二绝缘层ins2可以覆盖发光元件ld中的每个的有源层al。在一些实施方式中,第二绝缘层ins2可以包括有机材料和无机材料中的任何一种。

238.第1_a接触电极cne1_a和第2_a接触电极cne2_a可以位于第一绝缘层ins1上。第1_a接触电极cne1_a可以通过第一接触部件220电连接到第1_a电极elt1_a。第1_a接触电极cne1_a可以将发光元件ld电连接到第1_a电极elt1_a。第2_a接触电极cne2_a可以通过第二接触部件240电连接到公共连接电极celt。第2_a接触电极cne2_a可以将发光元件ld电连接到公共连接电极celt。

239.第1_a接触电极cne1_a和第2_a接触电极cne2_a可以包括导电材料。例如,第1_a接触电极cne1_a和第2_a接触电极cne2_a可以包括透明导电材料,其包括氧化铟锡(ito)、氧化铟锌(izo)和氧化铟锡锌(itzo),但是本公开不限于此。

240.第三绝缘层ins3可以位于第1_a接触电极cne1_a上。第三绝缘层ins3的至少一部分可以位于第1_a接触电极cne1_a和第2_a接触电极cne2_a之间,从而降低或防止第1_a接触电极cne1_a和第2_a接触电极cne2_a之间短路的可能性。在一些实施方式中,第三绝缘层ins3可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氧氮化硅(sio

x

ny)和氧化铝(alo

x

)中的至少一种。

241.第四绝缘层ins4可以位于显示元件层dpl的外部分中。第四绝缘层ins4可以保护显示元件层dpl的各个部件免受外部影响。在一些实施方式中,第四绝缘层ins4可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氧氮化硅(sio

x

ny)和氧化铝(alo

x

)中的至少一种。

242.第一子像素spxl1的结构不限于前述示例。在一些实施方式中,第一子像素spxl1还可以包括附加部件。

243.例如,还可以在第四绝缘层ins4上设置平坦化层。平坦化层可减轻由位于其下方的各种部件形成的台阶差。平坦化层的顶表面可以是大致平坦的。在一些实施方式中,平坦化层包括有机绝缘层。

244.在下文中,将参考图13和图14描述根据一些实施方式的位于像素pxl的显示元件层dpl上的层。

245.图13和图14是沿着图3的线ii-ii'截取的剖视图。图13示出了根据一些实施方式的像素pxl的剖面结构。图14示出了根据其它实施方式的像素pxl的剖面结构。在图13和图14中,为了便于说明,示意性地示出了像素电路层pcl和显示元件层dpl的各个部件。

246.将参考图13描述根据一些实施方式的像素pxl的剖面结构。

247.在一些实施方式中,分别位于第一子像素spxl1、第二子像素spxl2和第三子像素spxl3中的发光元件ld可以发射相同颜色的光。例如,第一子像素spxl1、第二子像素spxl2和第三子像素spxl3可以包括配置成发射第三颜色的光(例如,蓝光)的发光元件ld。可以在第一子像素spxl1、第二子像素spxl2和第三子像素spxl3中设置颜色转换层ccl和/或滤色器层cfl,从而可以显示全色图像。然而,本公开不限于此。例如,第一子像素spxl1、第二子像素spxl2和第三子像素spxl3可以包括配置成发射不同颜色的光的发光元件ld。

248.在一些实施方式中,颜色转换层ccl可以位于与显示元件层dpl的层相同的层上。例如,颜色转换层ccl可以位于堤部bnk之间。

249.颜色转换层ccl可以包括波长转换图案wcp、光透射图案ltp和第一封盖层cap1。例如,波长转换图案wcp可以包括第一波长转换图案wcp1和第二波长转换图案wcp2。

250.第一波长转换图案wcp1可以定位成与第一子像素spxl1的发射区域ema重叠。例如,第一波长转换图案wcp1可以设置在相应的堤部bnk之间,并且在平面图中与第一子像素spxl1的发射区域ema重叠。

251.第二波长转换图案wcp2可以定位成与第二子像素spxl2的发射区域ema重叠。例如,第二波长转换图案wcp2可以设置在相应的堤部bnk之间,并且在平面图中与第二子像素spxl2的发射区域ema重叠。

252.光透射图案ltp可以定位成与第三子像素spxl3的发射区域ema重叠。例如,光透射图案ltp可以设置在堤部bnk之间,并且可以在平面图中与第三子像素spxl3的发射区域ema重叠。

253.在一些实施方式中,第一波长转换图案wcp1可以包括将从发光元件ld发射的第三颜色的光转换成第一颜色的光的第一颜色转换颗粒。例如,在每个发光元件ld是配置成发射蓝光的蓝色发光元件并且第一子像素spxl1是红色像素的情况下,第一波长转换图案wcp1可以包括将从蓝色发光元件发射的蓝光转换成红光的第一量子点。

254.例如,第一波长转换图案wcp1可以包括分散在诸如基础树脂的基质材料(例如,预定基质材料)中的多个第一量子点。第一量子点可以吸收蓝光,可以根据能量跃迁来变换其波长,并且因此可以发射红光。在第一子像素spxl1是配置成发射不同颜色的光的像素的情况下,第一波长转换图案wcp1可以包括与从第一子像素spxl1发射的光的颜色对应的第一量子点。

255.在一些实施方式中,第二波长转换图案wcp2可以包括将从发光元件ld发射的第三颜色的光转换成第二颜色的光的第二颜色转换颗粒。例如,在每个发光元件ld是配置成发射蓝光的蓝色发光元件并且第二子像素spxl2是绿色像素的情况下,第二波长转换图案wcp2可以包括将从蓝色发光元件发射的蓝光转换成绿光的第二量子点。

256.例如,第二波长转换图案wcp2可以包括分散在诸如基础树脂的基质材料(例如,预

定基质材料)中的多个第二量子点。第二量子点可以吸收蓝光,可以根据能量跃迁变换其波长,并且因此可以发射绿光。在第二子像素spxl2是配置成发射不同颜色的光的像素的情况下,第二波长转换图案wcp2可以包括与从第二子像素spxl2发射的光的颜色对应的第二量子点。

257.第一量子点和第二量子点各自可以呈具有球形状、金字塔形状、多臂形状或立方体形状的纳米颗粒、纳米管、纳米纤维、平面纳米颗粒等的形式,但本公开不限于此。第一量子点和第二量子点中的每个的形状可以以各种方式改变。

258.在一些实施方式中,当在可见光范围中具有相对短波长的蓝光入射在第一量子点和第二量子点中的每个上时,第一量子点和第二量子点的吸收系数可以增加。最后,可以提高从第一子像素spxl1和第二子像素spxl2中的每个发射的光的效率,并且可以确保令人满意的颜色再现性。此外,因为包括第一子像素spxl1、第二子像素spxl2和第三子像素spxl3的像素单元由配置成发射相同颜色的光的发光元件ld(例如,蓝色发光元件)形成,所以可以提高制造显示装置的效率。

259.在一些实施方式中,可以设置光透射图案ltp以有效地使用从发光元件ld发射的第三颜色的光。例如,在每个发光元件ld是配置成发射蓝光的蓝色发光元件并且第三子像素spxl3是蓝色像素的情况下,光透射图案ltp可以包括至少一种类型的光散射颗粒以有效地使用从发光元件ld发射的光。

260.例如,光透射图案ltp可以包括分散在诸如基础树脂的基质材料(例如,预定基质材料)中的多个光散射颗粒。例如,光透射图案ltp包括光散射颗粒,但是光散射颗粒的构成材料不限于此。

261.不需要将光散射颗粒仅定位在第三子像素spxl3的发射区域ema中。例如,光散射颗粒也可以选择性地包括在第一波长转换图案wcp1和/或第二波长转换图案wcp2中。

262.第一封盖层cap1可以密封(或覆盖)波长转换图案wcp和光透射图案ltp。第一封盖层cap1可以位于低折射层lrl和显示元件层dpl之间。第一封盖层cap1可以设置成遍及第一子像素spxl1、第二子像素spxl2和第三子像素spxl3。第一封盖层cap1可以降低或防止颜色转换层ccl被诸如水或空气的外部杂质的渗透损坏或污染的可能性。

263.在一些实施方式中,第一封盖层cap1可以由包括氧化硅(sio

x

)、氮化硅(sin

x

)、氧氮化硅(sio

x

ny)、氧化铝(alo

x

)和氧化钛(tio

x

)中的至少一种绝缘材料的单层或多层形成,但本公开不限于此。

264.光学层opl可以包括低折射层lrl和第二封盖层cap2。光学层opl可以位于颜色转换层ccl上。光学层opl可以位于显示元件层dpl上。

265.低折射层lrl可以位于第一封盖层cap1和第二封盖层cap2之间。低折射层lrl可以位于颜色转换层ccl和滤色器层cfl之间。低折射层lrl可以设置成遍及第一子像素spxl1、第二子像素spxl2和第三子像素spxl3。

266.低折射层lrl可以用于通过基本上全反射再循环从颜色转换层ccl提供的光,并且因此可以提高光效率。因此,与颜色转换层ccl的折射率相比,低折射层lrl可以具有相对低的折射率。

267.在一些实施方式中,低折射层lrl可以包括基础树脂和分散在基础树脂中的中空颗粒。中空颗粒可以是中空二氧化硅颗粒。可选地,中空颗粒可以具有由致孔剂形成的孔,

但本公开不限于此。此外,低折射层lrl可以包括氧化锌(zno)颗粒、二氧化钛(tio2)颗粒和纳米硅酸盐颗粒中的至少一种,但本公开不限于此。

268.第二封盖层cap2可以位于低折射层lrl上。第二封盖层cap2可以位于滤色器层cfl和低折射层lrl之间。第二封盖层cap2可以设置成遍及第一子像素spxl1、第二子像素spxl2和第三子像素spxl3。第二封盖层cap2可以降低或防止低折射层lrl被外部杂质(诸如,水或空气)的渗透损坏或污染的可能性。

269.在一些实施方式中,第二封盖层cap2可以由包括氧化硅(sio

x

)、氮化硅(sin

x

)、氧氮化硅(sio

x

ny)、氧化铝(alo

x

)和氧化钛(tio

x

)中的至少一种绝缘材料的单层或多层形成,但本公开不限于此。

270.滤色器层cfl可以位于第二封盖层cap2上。滤色器层cfl可以设置成遍及第一子像素spxl1、第二子像素spxl2和第三子像素spxl3。滤色器层cfl可以包括滤色器cf1、cf2和cf3、平坦化层pla和外涂层oc。

271.在一些实施方式中,滤色器cf1、cf2和cf3可以位于第二封盖层cap2上。在平面图中,滤色器cf1、cf2和cf3可以分别与第一子像素spxl1、第二子像素spxl2和第三子像素spxl3的发射区域ema重叠。

272.在一些实施方式中,第一滤色器cf1可以允许第一颜色的光从其穿过,并且可以减少或防止第二颜色的光和第三颜色的光从其穿过。例如,第一滤色器cf1可以包括用于第一颜色的着色剂。

273.在一些实施方式中,第二滤色器cf2可以允许第二颜色的光从其穿过,并且可以减少或防止第一颜色的光和第三颜色的光从其穿过。例如,第二滤色器cf2可以包括用于第二颜色的着色剂。

274.在一些实施方式中,第三滤色器cf3可以允许第三颜色的光从其穿过,并且可以减少或防止第一颜色的光和第二颜色的光从其穿过。例如,第三滤色器cf3可以包括用于第三颜色的着色剂。

275.在一些实施方式中,平坦化层pla可以位于滤色器cf1、cf2和cf3上。平坦化层pla可以覆盖滤色器cf1、cf2和cf3。平坦化层pla可以补偿由滤色器cf1、cf2和cf3引起的台阶差。平坦化层pla可以设置成遍及第一子像素spxl1、第二子像素spxl2和第三子像素spxl3。

276.例如,平坦化层pla可以包括有机材料,诸如丙烯酸酯树脂、环氧树脂、酚醛树脂、聚酰胺树脂、聚酰亚胺树脂、聚酯树脂、聚苯硫醚树脂或苯并环丁烯(bcb)。然而,本公开不限于此。平坦化层pla可以包括各种无机材料,其包括氧化硅(sio

x

)、氮化硅(sin

x

)、氧氮化硅(sio

x

ny)、氮化铝(aln

x

)、氧化铝(alo

x

)、氧化锆(zro

x

)、氧化铪(hfo

x

)和氧化钛(tio

x

)。

277.外涂层oc可以位于平坦化层pla上。外涂层oc可以位于上膜层ufl和平坦化层pla之间。外涂层oc可以设置成遍及第一子像素spxl1、第二子像素spxl2和第三子像素spxl3。外涂层oc可以覆盖包括滤色器层cfl的下部件。外涂层oc可以减少或防止水或空气渗透下部件。此外,外涂层oc可以保护下部件免受诸如灰尘的外来物质的影响。

278.在一些实施方式中,外涂层oc可以包括有机材料,诸如丙烯酸酯树脂、环氧树脂、酚醛树脂、聚酰胺树脂、聚酰亚胺树脂、聚酯树脂、聚苯硫醚树脂或苯并环丁烯(bcb)。然而,本公开不限于此。外涂层oc可以包括各种无机材料,其包括氧化硅(sio

x

)、氮化硅(sin

x

)、氧氮化硅(sio

x

ny)、氮化铝(aln

x

)、氧化铝(alo

x

)、氧化锆(zro

x

)、氧化铪(hfo

x

)和氧化钛

(tio

x

)。

279.上膜层ufl可以位于滤色器层cfl上。上膜层ufl可以位于显示装置dd的外部分中以减少对显示装置dd的外部影响。上膜层ufl可以设置成遍及第一子像素spxl1、第二子像素spxl2和第三子像素spxl3。

280.在一些实施方式中,上膜层ufl可以包括抗反射(ar)涂层。ar涂层可以表示通过将具有抗反射功能的材料施加到特定部件的表面而形成的部件。这里,待施加的材料可以具有低反射率。例如,用于ar涂层的材料可以包括sio

x

、zio

x

、al

x

oy和tio

x

中的任何一种。然而,本公开不限于此,并且可以使用各种已知的材料。

281.接下来,将描述根据其它实施方式的像素pxl的结构。

282.参考图14,根据本实施方式的像素pxl与根据前述实施方式(参考图13)的像素pxl的不同之处在于,颜色转换层ccl位于与显示元件层dpl的层不同的层处。

283.在一些实施方式中,颜色转换层ccl可以位于显示元件层dpl上。例如,第一封盖层cap1可以密封(或覆盖)在其中定位有发光元件ld的区域。颜色转换层ccl可以位于第一封盖层cap1上。

284.在一些实施方式中,颜色转换层ccl还可以包括光阻挡层lbl。光阻挡层lbl可以位于显示元件层dpl上。光阻挡层lbl可以位于第一封盖层cap1和第二封盖层cap2之间。光阻挡层lbl可以位于第一子像素spxl1、第二子像素spxl2和第三子像素spxl3之间的边界中,以包围第一波长转换图案wcp1、第二波长转换图案wcp2和光透射图案ltp。

285.光阻挡层lbl可以限定像素pxl的发射区域ema和非发射区域nea。例如,在平面图中,光阻挡层lbl可以不与发射区域ema重叠。光阻挡层lbl可以在平面图中与非发射区域nea重叠。在一些实施方式中,其中不定位有光阻挡层lbl的区域可以被限定为第一子像素spxl1、第二子像素spxl2和第三子像素spxl3的发射区域ema。

286.在一些实施方式中,光阻挡层lbl可以由包括石墨、碳块、块颜料和黑色染料中的至少一种的材料形成,或者由包括铬(cr)的金属形成。光阻挡层lbl的材料不受限制,只要所述材料可以减少或防止光透射并且可以吸收光即可。

287.在一些实施方式中,第二封盖层cap2可以密封(或覆盖)第一波长转换图案wcp1、第二波长转换图案wcp2和光透射图案ltp。

288.在一些实施方式中,低折射层lrl可以位于第二封盖层cap2和第三封盖层cap3之间。第三封盖层cap3可以以与第一封盖层cap1和第二封盖层cap2的方式相同的方式,由包括氧化硅(sio

x

)、氮化硅(sin

x

)、氧氮化硅(sio

x

ny)、氧化铝(alo

x

)和氧化钛(tio

x

)中的至少一种绝缘材料的单层或多层形成,但是本公开不限于此。

289.本公开的一些实施方式可以提供一种显示装置,其中可以确保大到足以在其中布置发光元件的区域,从而可以提高发射效率,并且可以适当地降低功耗。

290.本公开的方面可以不限于以上,并且本公开的其它方面对于本领域普通技术人员而言将从提供有附图的公开内容中清楚地理解。

291.尽管出于说明的目的已经描述了本公开的实施方式,但是本领域技术人员将理解,在不背离本公开的范围和精神的情况下,各种修改、添加和替换是可能的。因此,本公开的以上描述的实施方式可以单独地或组合地实施。

292.因此,在本文中公开的实施方式不旨在限制而是描述本公开的技术精神,并且本

公开的范围不限于这些实施方式。本公开的范围应由所附权利要求来解释,且其功能等同被包括在其中,并且其等同的范围内的技术精神应被解释为包括在本公开的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1