非对称融合视觉传感器像素结构及其制备与信号控制方法

1.本发明属于半导体图像感测技术领域,涉及一种非对称融合视觉传感器像素结构及其制备与信号控制方法。

背景技术:

2.以cmos图像传感器(cis)为代表的主流技术已经发展成熟,但其基本原理为pn结在一帧曝光时间范围内进行光电积分,因此不利于大动态范围(high dynamic range)高速动态画面成像。近十余年来,动态视觉传感器(dynamic vision sensor)引起了学术界和工业界的广泛兴趣,基于事件相机(event camera)和帧差法(frame difference)的动态视觉技术被提出,有望解决传统cis技术在动态成像方面应用的瓶颈(参见g.kim,m.barangi,z.foo,n.pinckney,s.bang,d.blaauw,and d.sylvester,"a 467nw cmos visual motion sensor with temporal averaging and pixel aggregation."pp.480-481.和c.li,l.longinotti,f.corradi,and t.delbruck,"a132by 104 10μm-pixel 250μw 1kefps dynamic vision sensor with pixel-parallel noise and spatial redundancy suppression."pp.c216-c217.)。

3.动态视觉传感器优点众多,如更大的动态范围,更小的数据冗余,更低的功耗。因此可以广泛应用于自动驾驶,行为检测,特征识别等领域(参见k.d.choo,l.xu,y.kim,j.h.seol,x.wu,d.sylvester,and d.blaauw,"5.2energy-efficient low-noise cmos image sensor with capacitor array-assisted charge-injection sar adc for motion-triggered low-power iot applications."pp.96-98.和b.son,y.suh,s.kim,h.jung,j.s.kim,c.shin,k.park,k.lee,j.park,j.woo,y.roh,h.lee,y.wang,i.ovsiannikov,and h.ryu,"4.1a 640×480dynamic vision sensor with a 9µm pixel and 300meps address-event representation."pp.66-67.)。然而,基于事件的技术一般只有运动信号输出,无法提供像素本身的灰度值。此外,基于事件相机和帧差法两种技术目前都需要大量的像素内部(in-pixel)电路,造成像素结构的复杂和填充因子的降低。

4.为解决上述问题,本发明提供了一种非对称的融合视觉传感器像素结构。

技术实现要素:

5.本发明的目的就是为了提供一种非对称的融合视觉传感器像素结构及其制备与信号控制方法,以实现结构紧凑的同时,可输出绝对光强信号和差分光强信号等。

6.基于单晶体管光电子原位探测器件(pisd)(参见j.liu,y.f.cao,x.j.wang,y.l.jiang,and j.wan,“a novel one-transistor active pixel sensor with tunable sensitivity,”ieee electron device letters,vol.42,no.6,pp.927-930,apr,2021.)原理,本发明设计了一种全新的基于帧差法的紧凑型像素结构及其信号控制方法。本发明的创新之处在于,在像素晶体管一侧引入一个复位栅极控制该侧差分电容运算,其结果再通

过差分信号读出晶体管放大读出。因此在紧凑的像素结构中即可同时融合输出连续帧的光强绝对信号和差分信号。

7.本发明的目的可以通过以下技术方案来实现:

8.本发明的技术方案之一提供了一种非对称融合视觉传感器像素结构,包括底部的抗反射层、以及位于抗反射层上的混合型衬底与左侧衬底,其中,

9.所述混合型衬底上形成有浅槽隔离侧墙和衬底欧姆接触区域,并支撑起上方的第一氧化埋层与最上层的第一顶层区域,所述第一顶层区域包括三段像素有源区、位于两相邻像素有源区之间的第一顶层沟道区,两道第一顶层沟道区的上方还分别设有主体栅极与复位栅极,所述复位栅极位于主体栅极的左侧,所述主体栅极与复位栅极分别通过其下方的栅氧化层控制对应的第一顶层沟道区的通断,所述主体栅极与复位栅极的两侧均形成保护性侧墙,在混合型衬底的左右两侧形成深槽隔离侧墙,

10.所述的左侧衬底支撑起上方的第二氧化埋层和最上层的第二顶层区域,所述第二顶层区域包括两段读出晶体管有源区、以及位于两读出晶体管有源区之间的第二顶层沟道区,所述第二顶层沟道区上方设有读出晶体管栅极,该读出晶体管栅极也通过其下方的栅氧化层控制第二顶层沟道区的通断,所述读出晶体管栅极的两侧也均形成保护性侧墙,

11.复位栅极右侧的像素有源区、读出晶体管栅极右侧的读出晶体管有源区上还分别设有源极金属接触电极,位于主体栅极右侧的像素有源区、复位栅极左侧的像素有源区、读出晶体管栅极左侧的读出晶体管有源区上则分别设有漏极金属接触电极,所述衬底欧姆接触区域上设有衬底金属接触电极,所述主体栅极、复位栅极和读出晶体管栅极上则分别设有栅极金属接触电极。

12.进一步的,所述的混合型衬底与左侧衬底均为半导体,分别独立的选自硅、锗、锗硅、氮化镓或铟镓砷。

13.进一步的,像素有源区、读出晶体管有源区、第一顶层沟道区和第二顶层沟道区也均采用半导体,且分别独立的选自硅、锗、锗硅、氮化镓或铟镓砷。

14.进一步的,所述第一氧化埋层、第二氧化埋层分别独立的为二氧化硅、氧化铝或氧化铪绝缘材料。

15.进一步的,所述的混合型衬底与左侧衬底为p型轻掺杂,掺杂浓度为10

15-10

17

cm-3

。

16.进一步的,所述像素有源区、读出晶体管有源区则为n型重掺杂,掺杂浓度为10

19-10

21

cm-3

。

17.进一步的,所述衬底欧姆接触区域为p型重掺杂,掺杂浓度为10

19-10

21

cm-3

。

18.进一步的,抗反射层由抗反射sio2层、抗反射si3n4层和抗反射sio2层组成。

19.本发明的技术方案之二提供了一种基于全耗尽绝缘层上硅衬底的融合视觉传感器像素结构的制备方法,包括以下步骤:

20.(1)在起始的绝缘层上硅晶片上,通过刻蚀与外延形成混合型衬底、左侧衬底、第一氧化埋层、第二氧化埋层、以及第一顶层沟道区和第二顶层沟道区;

21.(2)光刻并刻蚀后,在混合型衬底中氧化生长形成一处浅槽隔离侧墙和两处深槽隔离侧墙;

22.(3)光刻并离子注入形成衬底欧姆接触区;

23.(4)在结构上淀积生长栅极氧化层和外延生长栅极材料,光刻并刻蚀后得到主体

栅极、复位栅极和读出晶体管栅极;

24.(5)通过原子层沉积形成保护性侧墙;

25.(6)光刻并刻蚀除掉主体栅极、复位栅极和读出晶体管栅极覆盖的顶层硅部分,后外延生长并原位掺杂,得到像素有源区和读出晶体管有源区;

26.(7)光刻并打开各栅极、源漏极接触区、衬底欧姆接触区窗口,淀积金属并退火,以在像素有源区、读出晶体管有源区和各栅极顶部形成金属接触电极;

27.(8)淀积生长抗反射层。

28.经上述制备工艺形成的像素结构具有多晶体管、多栅极的特征,除晶体管主栅极外,复位栅极起到联通差分电容的作用,最外侧晶体管为差分信号读出晶体管。因此,本发明实现的像素可同时实现光强绝对信号和差分信号的融合读出。

29.进一步的,步骤(1)中,第一氧化埋层和第二氧化埋层的厚度为10nm~1000nm。

30.进一步的,步骤(1)中,第一顶层沟道区和第二顶层沟道区的厚度为5nm~500nm。

31.进一步的,步骤(3)中,离子注入采用硼或者氟化硼,剂量为10

13

cm-2

~10

16

cm-2

,能量为1kev~100kev,离子激活退火温度为900~1200℃,时间为1微秒~10秒。

32.进一步的,步骤(4)中,栅极氧化层的厚度为1~30nm。

33.进一步的,步骤(4)中,所生长的栅极材料的厚度为10nm~500nm。

34.进一步的,步骤(7)中,沉积的金属为铝,镍,钛或者金属硅化物,退火温度为300~900℃。

35.本发明的技术方案之三提供了一种基于全耗尽绝缘层上硅衬底的融合视觉传感器像素结构的信号控制方法,该融合视觉传感器像素结构包括混合型衬底上的像素晶体管部分与左侧衬底上的差分信号读出晶体管部分,该信号控制方法包括以下步骤:

36.(a)将读出晶体管栅极上的栅极金属接触电极与复位栅极左侧的漏极金属接触电极相连接,同时,将像素晶体管部分与差分信号读出晶体管部分的源、漏和栅极电压偏置,其中,所有源极接地gnd,除复位栅极左侧的漏极外的其余两个漏极接一高电位电源v

ds

,主体栅极接另一高电位电源v

gs

,使像素晶体管处于常开状态;

37.(b)积分开始之前,将复位栅极拉为低电平,同时衬底金属接触电极处于高电平状态;

38.(c)对衬底金属接触电极施加一低电平瞬态脉冲,在混合型衬底形成一个深的耗尽区,以准备收集光生电子;

39.(d)光照开启,光生载流子开始在上述耗尽区内积分;

40.(e)光照结束,将复位栅极拉为高电平,衬底金属接触电极复位之前从差分信号读出晶体管部分的漏极读取第一帧差分信号i

e1

;同时从像素晶体管部分上最右侧的漏极读取第一帧绝对信号i

out1

;

41.(f)衬底金属接触电极拉到高电平复位,第一帧结束,同时差分电容(指复位栅极控制的晶体管电容,对应称作差分电容)存储第一帧光强信号;然后对衬底金属接触电极施加一低电平瞬态脉冲,在混合型衬底形成一个深的耗尽区,以准备收集光生电子;

42.(g)光照开启,光生载流子开始在上述耗尽区内积分;

43.(h)光照结束,将复位栅极拉为高电平;衬底金属接触电极复位之前从差分信号读出晶体管部分的漏极读取第二帧差分信号i

e2

,同时从像素晶体管部分右侧的漏极读取第二

帧绝对信号i

out2

;

44.(i)衬底金属接触电极拉到高电平复位,第二帧结束,同时差分电容存储第二帧光强信号。

45.(j)重复以上步骤,中间的像素晶体管部分即可得到每帧的光强绝对信号,左侧的差分电容即可计算每帧与上一帧之间的光强差分信号。

46.与现有技术相比,本发明通过施加衬底脉冲在埋氧化层/衬底界面下形成虚拟的光电二极管,在像素有源区上引入一个辅助的复位栅极作为复位开关来实现像素内部的差分运算,在深槽隔离包围区域外增加一个差分信号读出晶体管。其中中间晶体管感应衬底虚拟二极管的光强信号并放大读出,复位栅极联通的电容对帧与帧之间的光强信号做差分运算,结果通过对应的差分信号读出晶体管放大读出。本发明基于单晶体管光电子原位探测器(photoelectron in-situ sensing device:pisd)结构,在紧凑的像素架构内部可同时读出光强绝对信号和差分信号,实现了传统图像传感器(active pixel sensor:aps)光强数据和动态视觉传感器(dynamic vision sensor:dvs)事件数据的融合,为pisd在下一代新型动态视觉传感器中的应用奠定了基础。

附图说明

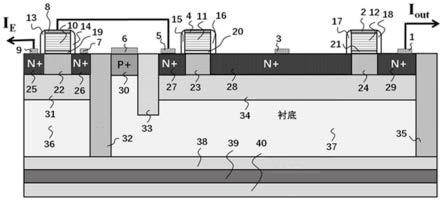

47.图1为本发明的融合视觉传感器像素的结构图示。

48.图2为本发明的融合视觉传感器像素的制备流程图示。

49.图3为本发明的融合视觉传感器像素的信号控制方法图示。

50.图4为本发明的融合视觉传感器像素的实施例2的结构。

51.图5为本发明的融合视觉传感器像素的的实施例2的信号控制方法图示。

具体实施方式

52.下面结合附图和具体实施例对本发明进行详细说明。本实施例以本发明技术方案为前提进行实施,给出了详细的实施方式和具体的操作过程,但本发明的保护范围不限于下述的实施例。

53.基于同一工作原理,像素的结构和对应的制备、信号控制方法可以不同,具体实施方式体现在不同实施例中。

54.另外,以下各实施例中,如无特别说明的功能部件结构、或处理技术,则表明其均为本领域为实现对应功能的常规部件结构,或常规处理技术。

55.实施例1(对应图1的像素结构,图2的工艺流程和图3的控制信号):

56.如图1所示,本实施例提供的基于全耗尽绝缘层上硅衬底的融合视觉传感器像素结构,包括底部的抗反射层(其由氧化硅层38、氮化硅层39和氧化硅层40组成)、以及位于抗反射层上的混合型衬底37与左侧衬底36,其中,

57.所述混合型衬底37上形成有浅槽隔离侧墙33和衬底欧姆接触区域30,并支撑起上方的第一氧化埋层34与最上层的第一顶层区域,所述第一顶层区域包括三段像素有源区27、28、29、位于两相邻像素有源区(即像素有源区27和像素有源区28、像素有源区28和像素有源区29)之间的第一顶层沟道区23、24,两道第一顶层沟道区23、24的上方还分别设有复位栅极11与主体栅极12,所述复位栅极11位于主体栅极12的左侧,所述主体栅极12与复位

栅极11分别通过其下方的栅氧化层21、20控制对应的第一顶层沟道区23、24的通断,所述主体栅极12与复位栅极11的两侧均形成保护性侧墙17、18、15、16,在混合型衬底37的左右两侧形成深槽隔离侧墙32、35,

58.所述的左侧衬底36支撑起上方的第二氧化埋层31和最上层的第二顶层区域,所述第二顶层区域包括两段读出晶体管有源区25、26、以及位于两读出晶体管有源区25、26之间的第二顶层沟道区22,所述第二顶层沟道区22上方设有读出晶体管栅极10,该读出晶体管栅极10也通过其下方的栅氧化层19控制第二顶层沟道区22的通断,所述读出晶体管栅极10的两侧也均形成保护性侧墙13、14,

59.像素有源区28、读出晶体管有源区26上还分别设有源极金属接触电极3、7,像素有源区29、像素有源区27、读出晶体管有源区25上则分别设有漏极金属接触电极1、5、9,所述衬底欧姆接触区域30上设有衬底金属接触电极6,所述主体栅极12、复位栅极11和读出晶体管栅极10上则分别设有栅极金属接触电极2、4、8。

60.如图2所示,实施例1的工艺流程主要有以下步骤:

61.(1)如图2(a)所示,为起始的绝缘层上硅晶片。其衬底掺杂一般为弱p型掺杂的硅,掺杂浓度在10

15-10

17

cm-3

之间。根据探测的光学波长不同,衬底也可为锗硅,氮化镓或者铟镓砷等材料。其埋层一般为二氧化硅,厚度在10nm至1000nm之间。上层的沟道一般为硅、锗硅,氮化镓或者铟镓砷等材料。厚度为5nm至500nm之间。

62.(2)利用光刻胶为掩膜刻蚀完氧化埋层至衬底硅,随后外延生长硅;光刻并打开衬底侧墙隔离sti和dti的窗口,之后利用光刻胶为掩膜刻蚀衬底硅,接着氧化生长二氧化硅。可以采用化学气相淀积(cvd)或者物理气相淀积(pvd)的方法形成sti和dti氧化隔离层,如图2(b)。刻蚀可选用干法或者湿法方法:干法刻蚀一般使用氟基或者卤族元素气体,如sf6、cl2等;而湿法腐蚀一般使用强酸或强碱如hf、nh4hf2等溶液。

63.(3)光刻并打开衬底接触区的窗口,对混合衬底表面进行离子注入或外延掺杂形成衬底欧姆接触区,离子注入一般使用硼或者氟化硼,剂量为10

13

cm-2

至10

16

cm-2

之间,能量为1kev至100kev之间,离子激活退火温度一般为900度至1200度之间,时间为1微秒至10秒,如图2(c);

64.(4)在结构上淀积生长栅极氧化层和外延生长栅极材料。氧化层可以是氧化铪或者氧化铝等高k介质材料,通过原子层沉积系统(ald)淀积,其厚度一般为1nm至30nm之间。栅极材料可以为多晶硅层或是多晶硅和金属的复合层,其厚度可为10nm至500nm。

65.(5)光刻并打开三个栅极的窗口,之后利用光刻胶为掩膜,对步骤(4)中生长材料进行刻蚀以形成栅极的图形,如图2(d)所示;刻蚀可选用干法或者湿法方法。干法刻蚀一般使用氟基或者卤族元素气体,如sf6,chf3,hbr或者cl2等。而湿法腐蚀一般使用tmah,koh等溶液。

66.(6)淀积一层栅极侧墙材料,如常用的氮化硅,二氧化硅,又或者是siocn和sibcn等低介电常数介质。淀积可使用化学气相沉积(cvd),原子层淀积(ald)等工艺。之后进行刻蚀以形成如图2(e)所示的栅极侧墙。刻蚀一般使用具有垂直方向性的反应离子刻蚀,干法刻蚀一般使用氟基气体,如sf6,chf3或者ch3f等。

67.(7)光刻并打开像素和读出晶体管有源区窗口,利用光刻胶为掩膜刻蚀掉除栅极覆盖的顶层硅部分,接着外延生长硅,外延生长时进行原位掺杂,掺杂浓度在10

19

cm-3

至

10

21

cm-3

之间。最终形成n型重掺杂的有源区(即像素有源区与读出晶体管有源区),如图2(f)。

68.(8)光刻并打开三个栅极、源漏极接触区、衬底欧姆接触区窗口,淀积金属并退火以在n型重掺杂有源区和三个栅极顶部形成如图2(g)所示的电极;常用金属为铝,镍,钛或者金属硅化物,如镍硅,钛硅等,退火温度为300~900℃之间;

69.(9)淀积生长sio2/si3n4/sio2抗反射层,可以采用化学气相淀积(cvd)或者物理气相淀积(pvd)的方法形成,如图2(h)。

70.如图3所示,图中左侧数字标号为各电极的编号,上述实施例所得像素结构的信号控制方法如下:

71.漏极金属接触电极5和栅极金属接触电极8相连短接。首先,将像素晶体管和差分信号读出晶体管的源、漏和栅极电压偏置在合适的固定偏置,其中所有源极(即源极金属接触电极3、7)接地gnd;所有漏极(即漏极金属接触电极1、9)接一高电位电源v

ds

(如0.8v);同时像素晶体管处的栅极(即栅极金属接触电极2)接另一高电位电源v

gs

(如1.8v)使晶体管处于常开状态。

72.积分开始之前,将复位栅极(即栅极金属接触电极4)拉为低电平;同时像素晶体管衬底偏置(即衬底金属接触电极6)处于高电平状态;

73.然后,对衬底偏置施加一低电平瞬态脉冲,在混合型衬底37形成一个深的耗尽区(虚拟光电二极管),以准备收集光生电子;

74.光照开启,光生载流子开始在上述耗尽区内积分;

75.光照结束,将复位栅极拉为高电平;衬底偏置复位之前从差分信号读出晶体管漏极(即漏极金属接触电极9)读取第一帧差分信号i

e1

;同时从像素晶体管漏极(即漏极金属接触电极1)读取第一帧绝对信号i

out1

;

76.衬底偏置拉到高电平复位,第一帧结束,同时差分电容记录第一帧光强信号;然后对衬底偏置施加一低电平瞬态脉冲,在衬底形成一个深的耗尽区(虚拟光电二极管),以准备收集光生电子;

77.光照开启,光生载流子开始在上述耗尽区内积分;

78.光照结束,将复位栅极拉为高电平;衬底偏置复位之前从差分信号读出晶体管漏极(9)读取第二帧差分信号i

e2

;同时从像素晶体管漏极读取第二帧绝对信号i

out2

;

79.衬底偏置拉到高电平复位,第二帧结束,同时差分电容记录第二帧光强信号。

80.重复以上步骤,中间像素晶体管即可得到每帧的光强绝对信号,左侧的差分电容即可计算每帧与上一帧之间的光强差分信号。

81.实施例2(对应图4的像素结构和图5的控制信号):

82.如图4所示,实施例2与实施例1类似,区别在于衬底为n型轻掺杂,且上层硅层中的晶体管是p型的,而非n型。因此,此实施例的工艺流程与实施例1类似,只需更换步骤(1)中的soi衬底,并将步骤(3)和(7)外延生长时的原位掺杂杂质类型反转。

83.如图5所示,实施例2的信号控制只需要针对器件掺杂类型的变化,将对应的部分信号控制改变,即可完成实施例2对应的功能。信号控制具体如下:

84.漏极金属接触电极5和栅极金属接触电极8相连短接。首先,将像素晶体管和差分信号读出晶体管的源、漏和栅极电压偏置在合适的固定偏置,其中所有源极(即源极金属接

触电极3、7)接地gnd;所有漏极(即漏极金属接触电极1、9)接一低电位电源v

ds

(如-0.8v);同时像素晶体管栅极(即栅极金属接触电极2)接另一低电位电源v

gs

(如-1.8v)使晶体管处于常开状态。

85.积分开始之前,将复位栅极(即栅极金属接触电极4)拉为高电平;同时像素晶体管衬底偏置(即衬底金属接触电极6)处于低电平状态;

86.然后,对衬底偏置施加一高电平瞬态脉冲,在衬底形成一个深的耗尽区(虚拟光电二极管),以准备收集光生电子;

87.光照开启,光生载流子开始在上述耗尽区内积分;

88.光照结束,将复位栅极拉为低电平;衬底偏置复位之前从差分信号读出晶体管漏极(即漏极金属接触电极9)读取第一帧差分信号i

e1

;同时从像素晶体管漏极(即漏极金属接触电极1)读取第一帧绝对信号i

out1

;

89.衬底偏置拉到低电平复位,第一帧结束,同时差分电容记录第一帧光强信号;然后对衬底偏置施加一高电平瞬态脉冲,在衬底形成一个深的耗尽区(虚拟光电二极管)以准备收集光生电子;

90.光照开启,光生载流子开始在上述耗尽区内积分;

91.光照结束,将复位栅极拉为低电平;衬底偏置复位之前从差分信号读出晶体管漏极读取第二帧差分信号i

e2

;同时从像素晶体管漏极读取第二帧绝对信号i

out2

;

92.衬底偏置拉到低电平复位,第二帧结束,同时差分电容记录第二帧光强信号。

93.重复以上步骤,中间像素晶体管即可得到每帧的光强绝对信号,左侧的差分电容即可计算每帧与上一帧之间的光强差分信号。

94.上述的对实施例的描述是为便于该技术领域的普通技术人员能理解和使用发明。熟悉本领域技术的人员显然可以容易地对这些实施例做出各种修改,并把在此说明的一般原理应用到其他实施例中而不必经过创造性的劳动。因此,本发明不限于上述实施例,本领域技术人员根据本发明的揭示,不脱离本发明范畴所做出的改进和修改都应该在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1