基于静电吸附量子点制备图案化QLED的方法

基于静电吸附量子点制备图案化qled的方法

技术领域

1.本发明属于纳米led制备技术领域,尤其涉及一种基于静电吸附量子点制备图案化qled的方法。

背景技术:

2.胶体量子点是一种半径尺寸范围在波尔半径左右的微粒,其特殊的尺寸效应使得它具有优异的光电特性。例如,通过控制微粒尺寸大小实现连续的高亮度光谱调控。此外,它还具有核壳结构,这使得量子点具有极高量子产率和良好的稳定性。这些优点使得量子点在下一代显示器的开发中具有广阔的前景。目前,虽然基于量子点构筑的量子点发光二极管器件已有重大的突破,但是在制造高分辨率和均匀的图案技术仍然缺乏。实现量子点发光二极管器件纳米图案化的困难在于溶液/基板界面处的复杂性。为了以纳米精度在定义的位置对齐,它需要量子点和底物之间的一系列相互作用。它需要长距离的粒子-基板吸引力来富集基板上的量子点以实现高效和快速的组装,需要强大的短程吸引力来将量子点固定在设计的位置,并通过反作用来避免量子点在不希望的区域的非特异性沉积。

技术实现要素:

3.针对现有技术的缺陷和不足,本发明提出一种基于静电吸附量子点制备图案化qled的方法,采用dpn(蘸水笔纳米光刻术)法制备图案化的薄膜并与配体修饰相结合的技术,利用静电吸附原理,使量子点精确被固定于设计的位置,从而获得高亮度、高ppi的显示像素单元,可应用下一代显示。

4.其先制备p4vp(4-乙烯基吡啶二嵌段共聚物)薄膜,再用dpn(蘸水笔纳米光刻术)法制备图案化的p4vp薄膜,最后在p4vp薄膜上旋涂配体(如羧酸、膦酸和硫醇末端的配体)修饰的量子点。

5.在p4vp薄膜上的图案是由于局部质子化形成的,通过静电作用可以吸附由于配体电离而带负电的量子点得到图案化的量子点薄膜。

6.以此为基础可以通过在p4vp薄膜上设计和制备不同尺寸的图案,从而获得亚微米以及纳米级别的量子点薄膜发光像素,通过转印技术把图案化的量子点薄膜转移到预制qled基底功能层上,制备出qled器件。

7.这种基于静电吸附量子点制备纳米led的方法使qled器件的像素尺寸可缩小至纳米级别,从而获得高亮度、高ppi的显示像素单元,可应用下一代显示。

8.本发明具体采用以下技术方案:一种基于静电吸附量子点制备图案化qled的方法,其特征在于:首先制备p4vp薄膜,再用dpn法制备图案化的p4vp薄膜,最后在p4vp薄膜上旋涂配体修饰的量子点;其中,在p4vp薄膜上的图案是通过局部质子化形成的,通过静电作用吸附由于配体电离而带负电的量子点得到图案化的量子点薄膜;通过转印技术把图案化的量子点薄膜

转移到预制qled基底功能层上,制备获得qled器件。

9.进一步地,其包括以下步骤:步骤s1:在it0玻璃基底电极上制备空穴注入层;步骤s2:在空穴注入层上沉积空穴传输层;步骤s3:在空穴传输层上沉积图案化量子点薄膜;步骤s4:在量子点薄膜上沉积电子传输层;步骤s5:在电子传输层上蒸镀金属电极作为顶电极,得到qled器件;在步骤s3中,先制备p4vp薄膜,再用dpn法将p4vp薄膜图案化,然后在p4vp薄膜上旋涂量子点,最后将量子点薄膜转印到ito基底的功能层上。

10.进一步地,步骤s1中所述空穴注入功能层材料为聚合物pedot:pss、氧化钼、氧化镍和硫氰亚铜中的至少一种;步骤s2中所述空穴传输功能层的材料为聚合物tfb、poly-tpd、pvk中的至少一种;步骤s3中所述量子点溶液中的量子点材料为羧酸、膦酸和硫醇末端的配体其中之一修饰后的量子点;步骤s4中所述金电子传输层材料为zn0纳米颗粒、掺杂金属阳离子的zn0纳米颗粒和ti0纳米颗粒中的至少一种;步骤s5中所述顶电极为al、ag、cu、au或合金电极中的一种,其中合金为al、ag、cu和au中至少两种元素的合金。

11.进一步地,步骤s1、s2和s4对应的外延层的制备方法均为旋涂。

12.进一步地,步骤s3的制备过程中,量子点溶液的溶剂为氯苯和甲苯中至少一种。

13.进一步地,步骤s1中所述空穴注入层的厚度5~10nm;步骤s2中所述空穴传输层的厚度为20~60nm;步骤s3中所述金属氧化物薄膜的厚度为100~150nm;步骤s4中所述顶电极的厚度为100~150nm。

14.进一步地,步骤s3中所述电量子点薄膜的形成经过退火固化得到发光层,退火的温度为70~110

°

c,固化的时间为30min。优选的退火温度为80

°

c。

15.进一步地,步骤s1中,所述it0玻璃基底电极在使用前需进行清洗处理,清洗处理为依次用丙酮、异丙醇、去离子水和超声震荡基底电极材10~15min;步骤s5中,顶电极制备完成后,经过封装得到qled器件。

16.与现有技术相比,本发明及其优选方案:(1)利用p4vp薄膜上的局部质子化固定了配体修饰后的量子点,使qled器件的像素尺寸可缩小至纳米级别,从而获得高亮度、高ppi的显示像素单元,可应用下一代显示。

17.(2)采用的制备过程安全无污染,不生成副产物,工艺简单易操作;(3)采用的p4vp薄膜还可以进一步设计成图案化。

附图说明

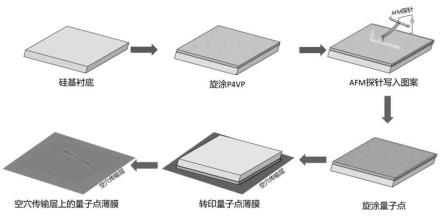

18.下面结合附图和具体实施方式对本发明进一步详细的说明:图1为本发明实施例转印图案化量子点制备纳米led的成品结构示意图;图2为本发明实施例在空穴传输层上沉积图案化量子点薄膜的工艺流程示意图。

具体实施方式

19.为让本专利的特征和优点能更明显易懂,下文特举实施例,作详细说明如下:应该指出,以下详细说明都是示例性的,旨在对本技术提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本技术所属技术领域的普通技术人员通常理解的相同含义。

20.需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本技术的示例性实施方式。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式。

21.如图2所示,本发明方案的关键工艺,即在空穴传输层上沉积图案化量子点薄膜的工艺流程具体包括以下步骤:(1)制备p4vp薄膜:将p型硅晶片浸入食人鱼溶液中清洗,其中食人鱼溶液由35%过氧化氢(h2o2)和98%硫酸(h2so4)组成,体积比为3:7,在80-90

°

c下搅拌30分钟以去除污染物。随后,用沸水清洗硅片60分钟,然后在n2下干燥。然后将清洁的晶片浸入hf水溶液中,以去除硅表面的天然氧化物层,用超纯水彻底冲洗,并用n2干燥。将p4vp在正丁醇(10 mg/ml)中的溶液以2000 rpm的转速旋涂到硅衬底上60 s。用450 w中压汞灯照射聚合物涂覆的衬底15分钟(照射时间包括约2分钟的预热,以使紫外线灯达到其最大强度)。将样品在正丁醇中浸泡3小时,去除未结合的聚合物,并用氮气干燥剩余的薄膜。

22.(2)p4vp薄膜图案化:在图案化过程之前,将afm(原子力显微镜)尖端浸入磷酸盐缓冲溶液中1分钟,然后用n2吹干。其中,磷酸盐缓冲溶液由将适当比例的磷酸二氢钠(nah2po4)和磷酸氢钠(na2hpo4)溶解在蒸馏水中制备(ph 4.0缓冲溶液比例为 13.8 和 0.036 g/l)。样品接地,同时向尖端施加偏压。将afm探针浸入ph为4.0的酸性磷酸盐缓冲溶液中。在图案化操作过程中,墨水笔尖以80 nm/s的固定写入速度在聚合物表面上扫描,同时笔尖与表面之间的接触力保持恒定。

23.(3)制备量子点薄膜:在图案化的p4vp薄膜上旋涂量子点。其中,量子点为羧酸修饰的cdse/zns量子点;旋涂时,量子点浓度为10~ 30mg/ ml ,旋涂转速为1000~2500rpm/min,时间为20~ 50s,旋涂成膜后于50~100

°

c下退火30~ 60min。

24.如图1所示,在以上工艺流程的基础上制备qled器件:纳米qled器件结构依次为ito层、空穴注入层、空穴传输层、图案化量子点薄膜、电子传输层、金属阴极。其中空穴注入层使用pedot:pss溶液,空穴传输层使用tfb溶液,利用匀胶机旋涂成膜,转速为3000rpm且时间为40s。图案化量子点薄膜通过转印至空穴传输层上,然后电子传输层是将掺杂有机聚合物pvp的zno纳米颗粒溶液旋涂成膜,转速为2000rpm且时间为40s。金属阴极通过真空镀膜机沉积100nm的ag电极。

25.本专利不局限于上述最佳实施方式,任何人在本专利的启示下都可以得出其它各种形式的基于静电吸附量子点制备图案化qled的方法,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本专利的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1