用于多芯片封装的凸块制备工艺的制作方法

本发明涉及半导体封装,具体涉及用于多芯片封装的凸块制备工艺。

背景技术:

1、半导体封装中的多芯片封装(multi chip package)是过个加工完成的芯片进行封装,在封装过程中需要在加工完成的芯片上制备凸块(bump)。

2、现有的凸块制备工艺为了缩短工艺流程,通常采用的基于沉积的光刻胶层进行电镀完成凸块制作,主要包括以下两种工艺:

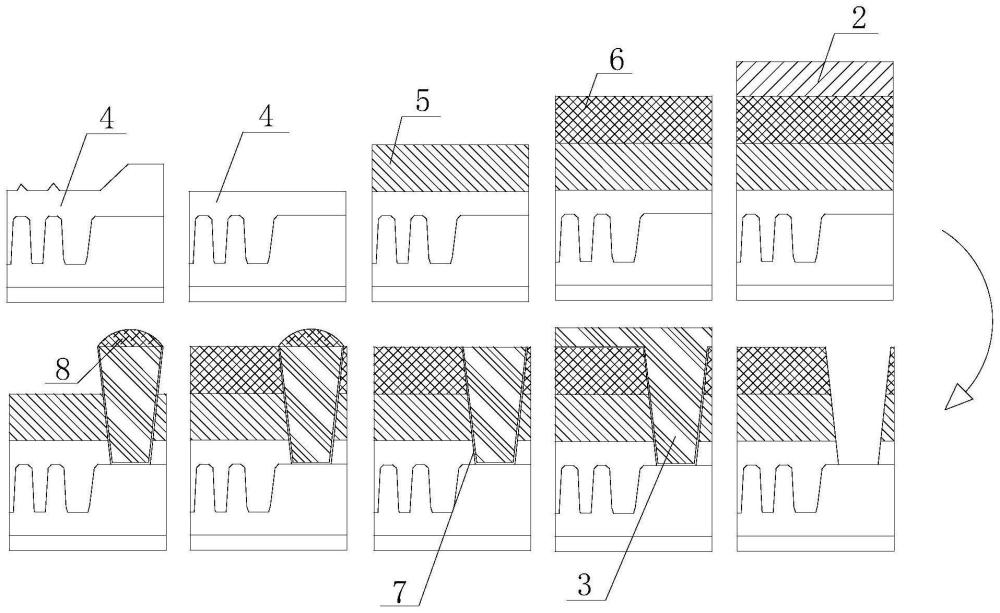

3、a、如图1所示,第一步:在加工完成的芯片上端面沉积一层种子层1,该种子层1采用和凸块相同的材料;第二步:在种子层1上沉积光刻胶层2;第三步:采用刻蚀工艺刻蚀光刻胶层2形成洞;第四步:采用电镀工艺向洞内填充金属形成金属层3,填充的金属与种子层1为相同材料;第五步:挥发去除光刻胶层2剩余面积;第六步:刻蚀掉去除光刻胶层2后暴露的种子层1完成凸块制备。

4、b、如图2所示,第一步:在加工完成的芯片上端面沉积光刻胶层2;第二步:采用刻蚀工艺刻蚀光刻胶层2形成洞;第三步:采用电镀工艺向洞内填充金属形成金属层3;第四步:挥发去除光刻胶层2剩余面积,根据凸块的图案需要,采用刻蚀工艺刻蚀金属层3,完成凸块制备。

5、上述两个工艺均是基于沉积的光刻胶层,采用电镀工艺制备凸块,虽然工艺简化降低了工艺成本,但是,由于光刻胶(pr)的粘度变化太大,导致光刻胶层的厚度分散严重,扩散电容(cd)的分散度更大,cd分散度大会导致电镀凸块时的高低压及宽度的统一性变差,会导致凸块节点阻力的问题,引起阻力性不良。

技术实现思路

1、本发明的目的在于提供用于多芯片封装的凸块制备工艺,以解决现有凸块制备工艺导致电镀凸块时的高低压及宽度的统一性较差的问题,降低凸块阻力性不良率。

2、本发明通过下述技术方案实现:

3、用于多芯片封装的凸块制备工艺,包括以下步骤:

4、s1、在加工完成的芯片上端面沉积高密度等离子体层,

5、s2、在高密度等离子体层的上端面沉积氮化硅层;

6、s3、在氮化硅层的上端面涂覆抗反射涂层;

7、s4、在抗反射涂层的上端面沉积光刻胶层;

8、s5、采用刻蚀工艺从上到下刻蚀光刻胶层、抗反射涂层、氮化硅层和等离子体层形成洞;

9、s6、挥发去除光刻胶层;

10、s7、采用电镀工艺在洞内填充金属形成金属层;

11、s8、对金属层的上端面进行平坦化处理,

12、s9、在金属层的顶部电镀形成导电端子;

13、s10、刻蚀去除抗反射涂层。

14、本发明的抗反射涂层能够吸收光刻反射光的物质。本发明的沉积工艺、涂覆工艺、刻蚀工艺和挥发工艺均是现有工艺。

15、本发明通过在光刻胶层(pr层)之前先制备高密度等离子体层、沉积氮化硅层和抗反射涂层,采用沉积氮化硅层和抗反射涂层的等效替换一定高度的光刻胶层,能够降低光刻胶层的厚度,即可以将现有的bump pr采用一般的i_line pr替换,由于光刻胶层的厚度降低了,能够缓解因pr的粘度变化太大,导致pr厚度的分散严重、cd的分散度大导致的电镀凸块时的高低压及宽度的统一性变差,能够降低因凸块阻力引起的不良。

16、进一步地,制备完成高密度等离子体层、氮化硅层和抗反射涂层后均采用化学机械研磨工艺进行表面平坦化处理。

17、本发明的化学机械研磨工艺(cmp工艺)为现有技术,能够实现表面平坦化。

18、进一步地,在洞内填充金属之前,先在洞的内壁沉积一层黏附层,所述黏附层用于提高金属层与洞内壁的附着稳定性。

19、本发明通过先沉积一层黏附层,能够使金属层的附着性更好。

20、进一步地,黏附层在洞的顶部向外水平延伸至抗反射涂层上端面。

21、进一步地,当金属层采用的金属为单质铜或铜锰合金时,黏附层采用氮化钽。

22、进一步地,抗反射涂层的厚度、氮化硅层的厚度和光刻胶层的厚度呈逐渐缩小的趋势。

23、进一步地,采用化学机械研磨工艺对导电端子进行平坦化处理,使凸块的高度变得均一,防止多芯片封装时凸块高度不良带来的芯片间的接触不良。

24、进一步地,抗反射涂层为碳涂层(soc层)。

25、进一步地,导电端子的材料为银锡合金。

26、进一步地,金属层为单质金属或合金。

27、本发明与现有技术相比,具有如下的优点和有益效果:

28、1、本发明通过在光刻胶层(pr层)之前先制备高密度等离子体层、沉积氮化硅层和抗反射涂层,能够降低光刻胶层的厚度,缓解了因pr的粘度变化太大,导致pr厚度的分散严重、cd的分散度大导致的电镀凸块时的高低压及宽度的统一性变差,能够降低因凸块阻力引起的不良。

29、2、本发明通过先沉积一层黏附层,能够提高金属层在洞内壁的附着稳定性。

30、3、本发明对导电端子进行平坦化处理,使凸块的高度变得均一,防止多芯片封装时凸块高度不良带来的芯片间的接触不良。

31、4、本发明可采用逐渐变得通用化的soc制备凸块。

32、5、本发明制备的凸块的关键尺寸和厚度公差是稳定的。

技术特征:

1.用于多芯片封装的凸块制备工艺,其特征在于,包括以下步骤:

2.根据权利要求1所述的用于多芯片封装的凸块制备工艺,其特征在于,制备完成高密度等离子体层(4)、氮化硅层(5)和抗反射涂层(6)后均采用化学机械研磨工艺进行表面平坦化处理。

3.根据权利要求1所述的用于多芯片封装的凸块制备工艺,其特征在于,在洞内填充金属之前,先在洞的内壁沉积一层黏附层(7),所述黏附层(7)用于提高金属层(3)与洞内壁的附着稳定性。

4.根据权利要求3所述的用于多芯片封装的凸块制备工艺,其特征在于,黏附层(7)在洞的顶部向外水平延伸至抗反射涂层(6)上端面。

5.根据权利要求3所述的用于多芯片封装的凸块制备工艺,其特征在于,当金属层(3)采用的金属为单质铜或铜锰合金时,黏附层(7)采用氮化钽。

6.根据权利要求1所述的用于多芯片封装的凸块制备工艺,其特征在于,抗反射涂层(6)的厚度、氮化硅层(5)的厚度和光刻胶层(2)的厚度呈逐渐缩小的趋势。

7.根据权利要求1所述的用于多芯片封装的凸块制备工艺,其特征在于,采用化学机械研磨工艺对导电端子(8)进行平坦化处理。

8.根据权利要求1所述的用于多芯片封装的凸块制备工艺,其特征在于,抗反射涂层(6)为碳涂层。

9.根据权利要求1所述的用于多芯片封装的凸块制备工艺,其特征在于,导电端子(8)的材料为银锡合金。

10.根据权利要求1-9任一项所述的用于多芯片封装的凸块制备工艺,其特征在于,金属层(3)为单质金属或合金。

技术总结

本发明公开了用于多芯片封装的凸块制备工艺,包括以下步骤:S1、在加工完成的芯片上端面沉积高密度等离子体层,S2、在高密度等离子体层的上端面沉积氮化硅层;S3、在氮化硅层的上端面涂覆抗反射涂层;S4、在抗反射涂层的上端面沉积光刻胶层;S5、采用刻蚀工艺从上到下刻蚀光刻胶层、抗反射涂层、氮化硅层和等离子体层形成洞;S6、挥发去除光刻胶层;S7、采用电镀工艺在洞内填充金属形成金属层;S8、对金属层的上端面进行平坦化处理,S9、在金属层的顶部电镀形成导电端子;S10、刻蚀去除抗反射涂层。本发明解决了现有凸块制备工艺导致电镀凸块时的高低压及宽度的统一性较差的问题,降低了凸块阻力性不良率。

技术研发人员:崔栽荣

受保护的技术使用者:成都高真科技有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!