阵列基板和显示面板的制作方法

1.本技术涉及显示领域,具体涉及一种阵列基板和显示面板。

背景技术:

2.随着高分辨率、高清晰度的显示设备市场需求进一步增加,金属氧化物凭借其相对非晶硅更高的迁移率及相对低温多晶硅更低的漏电流,且与当前工艺较为兼容及出色的制程均匀性等特点,成为了近年来阵列基板领域研究的热点,越来越多被应用在lcd和amoled的显示器件中。但碍于当前常规的氧化铟镓锌器件迁移率相对较低,目前还难以应用于对于分辨率和清晰度要求更高的智能终端高端产品中。

3.因此,亟需提供一种性能优异的阵列基板,用以解决现有技术的问题。

技术实现要素:

4.本技术的目的在于提供一种阵列基板,可以提高器件迁移率,解决了上述现有技术的不足。

5.本技术提供一种阵列基板,包括:衬底基板,以及设置于所述衬底基板上的栅极、栅绝缘层和有源层;所述有源层包括层叠设置的第一有源层和第二有源层;其中,所述第一有源层靠近所述栅极设置,所述第二有源层位于所述第一有源层背离所述栅极的一侧;所述第一有源层的迁移率高于所述第二有源层的迁移率。

6.可选的,在本技术的一些实施例中,所述有源层的材料包括氧化物半导体和稀土金属氧化物。

7.可选的,在本技术的一些实施例中,所述氧化物半导体包括氧化铟镓锌、氧化铟镓锡、氧化铟镓、氧化铟和氧化铟锌中的一种或多种。

8.可选的,在本技术的一些实施例中,所述稀土金属氧化物中的稀土元素包括钐、铽、镝、铕、铒、锡、镧、铈、镱和镨中的一种或多种。

9.可选的,在本技术的一些实施例中,所述第一有源层中的稀土元素包括钐、铽、镝、铕、铒和锡中的一种或多种。

10.可选的,在本技术的一些实施例中,所述第一有源层中的稀土金属氧化物的掺杂比为0.001-0.1。进一步地,所述第一有源层中的稀土金属氧化物的掺杂比为0.01-0.05。

11.可选的,在本技术的一些实施例中,所述第二有源层中的稀土元素包括镧、铽、镝、铈、铒、镱和镨中的一种或多种。

12.可选的,在本技术的一些实施例中,所述第二有源层中的稀土金属氧化物的掺杂比为0.1-0.3。

13.可选的,在本技术的一些实施例中,所述第二有源层中的稀土金属氧化物的掺杂比与所述第一有源层中的稀土金属氧化物的掺杂比相同,所述第二有源层中的稀土元素的迁移率比所述第一有源层中的稀土元素的迁移率低。

14.可选的,在本技术的一些实施例中,所述第二有源层中的稀土元素与所述第一有源层中的稀土元素相同,所述第二有源层中的稀土金属氧化物的掺杂比为0.15-0.3。

15.可选的,在本技术的一些实施例中,所述第二有源层中的稀土元素与所述第一有源层中的稀土元素不相同,且所述第二有源层中的稀土元素的迁移率比所述第一有源层中的稀土元素低,所述第二有源层中的稀土金属氧化物的掺杂比为0.1-0.3。

16.可选的,在本技术的一些实施例中,所述第一有源层内掺杂的稀土金属氧化物的迁移率高于所述第二有源层内稀土金属氧化物的迁移率。

17.可选的,在本技术的一些实施例中,所述阵列基板包括:衬底基板;第二有源层,设置在所述衬底基板上;第一有源层,设置在所述第二有源层上,所述第一有源层包括源区、沟道区及漏区;栅绝缘层,设置在所述第一有源层上的沟道区;栅极,设置在所述栅绝缘层上;源极,设置在所述第一有源层上的源区;漏极,设置在所述第一有源层上的漏区;钝化层,设置在所述第二有源层、所述第一有源层、所述栅绝缘层、所述栅极、所述源极和所述漏极上。

18.可选的,在本技术的一些实施例中,所述阵列基板包括:衬底基板;栅极,设置在所述衬底基板上;栅绝缘层,设置在所述栅极和所述衬底基板上;第一有源层,设置在所述栅绝缘层上;第二有源层,设置在所述第一有源层上;所述第二有源层包括源区、沟道区及漏区;源极,设置在所述第二有源层上的源区;漏极,设置在所述第二有源层上的漏区;钝化层,设置在所述栅极、所述栅绝缘层、所述第一有源层、所述第二有源层、所述源极和所述漏极上。

19.可选的,在本技术的一些实施例中,所述阵列基板还包括刻蚀阻挡层。

20.所述刻蚀阻挡层设置在所述第二有源层与所述源极、所述漏极之间。

21.所述刻蚀阻挡层设置在所述第二有源层上的沟道区以及部分的源区和部分的漏区。

22.可选的,在本技术的一些实施例中,所述钝化层的材料包括sio

x

(硅的氧化物)和sin

x

(硅的氮化物)中的一种或多种。

23.可选的,在本技术的一些实施例中,所述钝化层包括第一钝化层和/或第二钝化层。

24.本技术的有益效果在于:本技术实施例采用掺杂稀土元素的叠层有源层,前沟道侧形成迁移率相对较高、

开态电流相对较高的薄膜,可以提高开态电流;在背沟道侧形成迁移率较低和关态电流相对较低的薄膜,可以降低关态电流。

附图说明

25.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

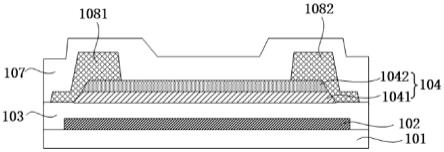

26.图1是本技术实施例提供的阵列基板的结构示意图一;图2是本技术实施例提供的阵列基板的结构示意图二;图3是本技术实施例提供的阵列基板的结构示意图三;图4是本技术实施例1~4提供的器件参数及特性检测的数据图;图5是本技术实施例9~12提供的器件参数及特性检测的数据图;图6是本技术实施例17~20提供的器件参数及特性检测的数据图;图7是本技术实施例5~8提供的器件特参数及性检测的数据图;图8是本技术实施例13~16提供的器件参数及特性检测的数据图;图9是本技术实施例21~24提供的器件参数及特性检测的数据图。

具体实施方式

27.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本技术,并不用于限制本技术。另外,在本技术的描述中,术语“包括”是指“包括但不限于”。用语第一、第二、第三等仅仅作为标示使用,并没有强加数字要求或建立顺序。本技术的各种实施例可以以一个范围的型式存在;应当理解,以一范围型式的描述仅仅是因为方便及简洁,不应理解为对本技术范围的硬性限制;因此,应当认为所述的范围描述已经具体公开所有可能的子范围以及该范围内的单一数值。

28.在对现有技术的研究和实践过程中,本技术的发明人发现,使用稀土元素掺杂的金属氧化物半导体因在具备低漏电流的基础上,进一步增加迁移率,使之更为满足高端显示产品的开发需求。然而,由于相对传统的氧化铟镓锌体系有较低的稳定性,故限制了其推广。本技术发明人精准控制稀土掺杂量及做好器件结构的设计,进而实现器件性能的进一步提高。

29.本技术发明人提出了由稀土元素和特定摩尔比的叠层金属氧化物半导体器件,能同时兼备不同掺杂比下器件的不同优势,使器件兼备更为优异的性能。

30.本技术实施例提供一种阵列基板(tft,thin film transistor)和显示面板。以下分别进行详细说明。需说明的是,以下实施例的描述顺序不作为对实施例优选顺序的限定。

31.本技术实施例提供一种阵列基板,包括衬底基板、栅极、栅绝缘层和有源层。栅极、栅绝缘层和有源层均设置于所述衬底基板上。

32.所述有源层包括层叠设置的第一有源层和第二有源层。进一步地,所述第一有源层靠近所述栅极设置,所述第二有源层位于所述第一有源层背离所述栅极的一侧;所述第一有源层的迁移率高于所述第二有源层的迁移率。

33.本技术实施例通过叠层有源层结构,形成同时兼备多种掺杂氧化物半导体的优势,提升阵列基板的性能。

34.本技术实施例中,阵列基板中的有源层为叠层结构,靠近栅极的那一层的迁移率要高于远离栅极的那一层。本技术可以通过有源层的材料来调控迁移率,进而时实现迁移率的高低的效果。

35.在本技术的一些实施例中,所述有源层的材料包括氧化物半导体和稀土金属氧化物。进一步地,所述氧化物半导体包括氧化铟镓锌、氧化铟镓锡、氧化铟镓、氧化铟和氧化铟锌中的一种或多种。进一步地,所述稀土金属氧化物中的稀土元素包括钐、铽、镝、铕、铒、锡、镧、铈、镱和镨中的一种或多种。

36.更进一步地,所述稀土元素掺杂以其金属氧化物形式,例如,稀土金属氧化物选自氧化钐、氧化铽、氧化镝、氧化铕、氧化铒、氧化锡、氧化镧、氧化铈、氧化镱和氧化镨中的一种或多种。

37.可以理解,所述第一有源层内掺杂的稀土金属氧化物的迁移率高于所述第二有源层内稀土金属氧化物的迁移率。也就是说,第一有源层,前沟道需使用迁移率较高的氧化物半导体;第二有源层,背沟道使用迁移率相对较低的金属氧化物半导体。

38.在本技术的一些实施例中,所述第一有源层包括所述氧化物半导体和所述稀土金属氧化物。其中,所述第一有源层中的稀土元素包括钐、铽、镝、铕、铒和锡中的一种或多种。并且,所述第一有源层中的稀土金属氧化物的掺杂比为0.001-0.1。进一步地,所述第一有源层中的稀土金属氧化物的掺杂比可以为0.01-0.05。可以理解,本技术的掺杂比为掺杂元素的摩尔比,例如0.001-0.1即为0.001-0.1:1,将第一有源层的记为1计算得到。例如,稀土金属氧化物在第一有源层中的掺杂比可以为0.001:1、0.002:1、0.003:1、0.004:1、0.005:1、0.006:1、0.007:1、0.008:1、0.009:1、0.01:1、0.02:1、0.03:1、0.04:1、0.05:1、0.06:1、0.07:1、0.08:1、0.09:1或0.1:1。

39.在本技术的一些实施例中,所述第二有源层包括所述氧化物半导体和所述稀土金属氧化物。其中,所述第二有源层中的稀土元素包括镧、铽、镝、铈、铒、镱和镨中的一种或多种。所述第二有源层中的稀土金属氧化物的掺杂比为0.1-0.3。进一步地,所述第二有源层中的稀土金属氧化物的掺杂比为0.3~0.7:1。例如,稀土金属氧化物在第二有源层中的掺杂比可以为0.1:1、0.12:1、0.15:1、0.2:1、0.25:1或0.3:1。

40.所述第一有源层内掺杂的稀土金属氧化物的迁移率高于所述第二有源层内稀土金属氧化物的迁移率。本技术实施例中,可以通过调整第一有源层、第二有源层内的稀土金属氧化物的稀土元素的种类和/或稀土金属氧化物的具体掺杂比来控制第一有源层和第二有源层迁移率差。

41.例如,当所述第二有源层中的稀土金属氧化物的掺杂比与所述第一有源层中的稀土金属氧化物的掺杂比相同,所述第二有源层中的稀土元素的迁移率比所述第一有源层中的稀土元素的迁移率低。

42.例如,当所述第二有源层中的稀土元素与所述第一有源层中的稀土元素相同时,

所述第二有源层中的稀土金属氧化物的掺杂比为0.15-0.3。可以理解,此时通过掺杂比,使得第一有源层的迁移率高于第二有源层的迁移率。

43.例如,当所述第二有源层中的稀土元素与所述第一有源层中的稀土元素不相同时,且所述第二有源层中的稀土元素的迁移率比所述第一有源层中的稀土元素低。也就是说,不同元素在同掺杂比例下,能够使得第一有源层内掺杂的稀土金属氧化物的迁移率高于第二有源层内稀土金属氧化物的迁移率。此时,所述第二有源层中的稀土金属氧化物的掺杂比可以为0.1-0.3。

44.本技术实施例中,稀土金属氧化物的掺杂比为该稀土金属氧化物中的稀土元素在对应的有源层中的摩尔掺杂比。

45.本技术实施例中,形成使用稀土元素掺杂的特定摩尔比的氧化物半导体叠层薄膜,前沟道侧形成迁移率相对较高、开态电流相对较高的薄膜,可以提高开态电流;在背沟道侧形成迁移率较低和关态电流相对较低的薄膜,可以降低关态电流。

46.在本技术的一些实施例中,所述钝化层的材料包括sio

x

(硅的氧化物)和sin

x

(硅的氮化物)中的一种或多种。进一步地,所述钝化层包括第一钝化层和/或第二钝化层。例如,所述第一钝化层的材料为sio

x

;例如,所述第二钝化层的材料为sin

x

。

47.在本技术的一些实施例中,本技术的阵列基板可为bce结构的阵列基板。请参阅图1,所述阵列基板包括:设置在衬底基板101上的栅极102、栅绝缘层103、有源层104、源极1081、漏极1082、钝化层107。

48.具体地,在阵列基板中,栅极102设置在所述衬底基板101上。栅绝缘层103设置在所述栅极102和所述衬底基板101上。有源层104设置在所述栅绝缘层103上。所述有源层104包括源区、沟道区及漏区。源极1081设置在所述有源层104上的源区。漏极1082设置在所述有源层104上的漏区。钝化层107设置在所述栅极102、所述栅绝缘层103、所述有源层104、所述源极1081和所述漏极1082上。

49.请继续参阅图1,有源层104包括层叠设置的第一有源层1041和第二有源层1042。此时,有源层104的双层叠层结构中,靠近栅极102的为第一有源层1041,远离栅极102的为第二有源层1042,第一有源层1041的迁移率要高于第二有源层1042。参考上述对有源层掺杂的稀土元素以及掺杂比的选择,实现第一有源层1041的迁移率高于第二有源层1042的迁移率。例如,第一有源层1041可以使用迁移率较高的稀土金属氧化物,而第二有源层1042使用迁移率相对较低的稀土金属氧化物,用以实现第一有源层1041的迁移率相对高于第二有源层1042的迁移率。此外,还可以采用相同氧化物半导体但掺杂比不同,进而实现第一有源层1041的迁移率相对高于第二有源层1042的迁移率。

50.在本技术的一些实施例中,本技术的阵列基板可为esl结构的阵列基板。请参阅图2,所述阵列基板包括:设置在衬底基板201上的栅极202、栅绝缘层203、有源层204、刻蚀阻挡层205、源极2081、漏极2082、钝化层207。

51.具体地,在阵列基板中,栅极202设置在所述衬底基板201上。栅绝缘层203设置在所述栅极202和所述衬底基板201上。有源层204设置在所述栅绝缘层203上;所述有源层204包括源区、沟道区及漏区。刻蚀阻挡层205设置在所述有源层204上的沟道区,以及部分的源区和部分的漏区。源极2081设置在所述有源层204上的源区,并且,设置在部分的所述刻蚀阻挡层上。漏极2082设置在所述有源层204上的漏区,并且,设置在部分的所述刻蚀阻挡层

205上。钝化层207设置在所述栅极202、所述栅绝缘层203、所述有源层204、所述源极2081和所述漏极2082上。

52.本技术实施例中,刻蚀阻挡层(esl)结构的阵列基板可以提高氧化物阵列基板稳定性,该结构可有效降低外界环境因素与源漏电极的刻蚀损伤对背沟道的影响。

53.请继续参阅图2,有源层204包括层叠设置的第一有源层2041和第二有源层2042。此时,在有源层204的双层叠层结构中,靠近栅极202的为第一有源层2041,远离栅极202的为第二有源层2042,第一有源层2041的迁移率要高于第二有源层2042。同理,双层叠层结构中的迁移率差,可以通过有源层中掺杂的稀土元素以及掺杂比的选择来实现第一有源层2041的迁移率高于第二有源层2042的迁移率的目的。例如,第一有源层2041可以使用迁移率较高的稀土金属氧化物,而第二有源层2042使用迁移率相对较低的稀土金属氧化物,用以实现第一有源层2041的迁移率相对高于第二有源层2042的迁移率。此外,还可以采用相同氧化物半导体但掺杂比不同,进而实现第一有源层2041的迁移率相对高于第二有源层2042的迁移率。

54.在本技术的一些实施例中,本技术的阵列基板可为顶栅型(top-gate)阵列基板。请参阅图3,所述阵列基板包括:设置在衬底基板301上的有源层304、栅绝缘层305、栅极306、源极3081、漏极3082、钝化层。

55.具体地,在阵列基板中,有源层304设置在所述衬底基板301上,所述有源层304包括源区、沟道区及漏区。栅绝缘层305设置在所述有源层304上的沟道区。栅极306设置在所述栅绝缘层305上。源极3081设置在所述有源层304上的源区。漏极3082设置在所述有源层304上的漏区。钝化层设置在所述有源层304、所述栅绝缘层305、所述栅极306、所述源极3081和所述漏极3082上。

56.本实施例中,请继续参阅图3,有源层304包括层叠设置的第一有源层3041和第二有源层3042。此时,有源层304的双层叠层结构中,靠近栅极306的为第一有源层3041,远离栅极306的为第二有源层3042,第一有源层3041的迁移率要高于第二有源层3042。例如,第一有源层3041可以使用迁移率较高的稀土金属氧化物,而第二有源层3042使用迁移率相对较低的稀土金属氧化物,这样可以实现第一有源层3041的迁移率相对高于第二有源层3042的迁移率。此外,还可以采用相同氧化物半导体但掺杂比不同,进而实现第一有源层3041的迁移率相对高于第二有源层3042的迁移率。

57.进一步地,请继续参阅图3,钝化层包括第一钝化层307和第二钝化层309。

58.进一步地,请继续参阅图3,先在衬底基板301设置有金属层302以及覆盖在金属层302上的绝缘层303。再在绝缘层303上依次设置上述的有源层304、栅绝缘层305、栅极306、源极3081、漏极3082、钝化层。进一步地,所述钝化层包括第一钝化层307和第二钝化层309。

59.本技术实施例的阵列基板的制备方法,包括:通过稀土金属氧化物靶和金属氧化物基质靶共溅射形成氧化物半导体层,其中通过调整工艺参数可获得对应掺杂比的半导体薄膜,即制成有源层。

60.本技术实施例的所述顶栅型(top gate)、esl、bce架构的阵列基板工艺流程分别如图下。

61.在一些实施例中,本技术实施例的顶栅型(top gate)架构的阵列基板工艺流程可以采用本领域常规的制备工艺制成。例如,请参见图3,顶栅型阵列基板的制备工艺包括:

衬底基板301:cvd(chemicalvapordeposition,化学气相沉积);金属层302:pvd(physical vapor deposition,物理气相沉积)

→

ph

→

wet(湿法刻蚀)

→

str(灰化);绝缘层303:cvd

→

ph

→

det(干法刻蚀)

→

str;有源层304:pvd

→

ph

→

det

→

str

→

anneal(退火);栅绝缘层305:cvd

→

ph

→

det

→

str

→

anneal;栅极306:pvd

→

ph

→

wet

→

str;第一钝化层307:cvd

→

ph

→

det

→

str;源极3081和漏极3082:pvd

→

ph

→

wet

→

str;第二钝化层309:cvd

→

ph

→

det

→

str。

62.在一些实施例中,本技术实施例的esl结构的阵列基板工艺流程可以采用本领域常规的制备工艺制成。例如,请参见图2,esl结构的阵列基板的制备工艺可以包括如下工艺流程:衬底基板201:cvd(化学气相沉积);栅极202:pvd(物理气相沉积)

→

ph

→

wet(湿法刻蚀)

→

str(灰化);栅绝缘层203:cvd

→

ph

→

det(干法刻蚀)

→

str;有源层204:pvd

→

ph

→

det

→

str

→

anneal;刻蚀阻挡层205:cvd

→

ph

→

det

→

str

→

anneal;源极2081和漏极2082:pvd

→

ph

→

wet

→

str;钝化层207:cvd

→

ph

→

det

→

str。

63.在一些实施例中,本技术实施例的bce结构的阵列基板工艺流程可以采用本领域常规的制备工艺制成。例如,请参见图1,bce结构的阵列基板的制备工艺可以包括如下工艺流程:衬底基板101:cvd(chemicalvapordeposition,化学气相沉积);栅极102:pvd(physical vapor deposition,物理气相沉积)

→

ph

→

wet(湿法刻蚀)

→

str(灰化);栅绝缘层103:cvd

→

ph

→

det(干法刻蚀)

→

str;有源层104:pvd

→

ph

→

det

→

str

→

anneal(退火);源极1081和漏极1082:pvd

→

ph

→

wet

→

str;钝化层107:cvd

→

ph

→

det

→

str

→

anneal。

64.本技术实施例还提供一种显示面板,该显示面板包括上述的阵列基板。显示面板还包括触控结构、封装结构等常规结构。合适显示面板的示例包括但不限于:lcd、oled、micro led。

65.本技术先后进行过多次试验,现举一部分试验结果作为参考对发明进行进一步详细描述,下面结合具体实施例进行详细说明。

66.实施例1~4实施例1~4提供一种top-gate架构的阵列基板,请参考图3,包括:设置在衬底基板301上的有源层304、栅绝缘层305、栅极306、源极3081、漏极3082、钝化层。有源层304包括层叠设置的第一有源层3041和第二有源层3042。第一有源层、第二有源层分别包括氧化物半

导体(氧化铟锌)和稀土金属氧化物。第一有源层的迁移率高于第二有源层的迁移率。

67.实施例1~4中,第一有源层、第二有源层中的稀土金属氧化物采用同元素不同比例掺杂。

68.具体地,第一有源层、第二有源层采用相同稀土元素且以不同比例掺杂时,稀土元素及掺杂摩尔比请详见图4所示。本实施例1~4采用图4中的参数获得的top-gate架构的阵列基板进行器件特性检测,如阈值电压、迁移率、亚阈值摆幅、开关电流比、pbts、nbtis,检测结果详见图4所示。

69.实施例5~8实施例5~8提供一种top-gate架构的阵列基板,请参考图3,包括:设置在衬底基板301上的有源层304、栅绝缘层305、栅极306、源极3081、漏极3082、钝化层。有源层304包括层叠设置的第一有源层3041和第二有源层3042。第一有源层、第二有源层分别包括氧化物半导体(氧化铟锌)和稀土金属氧化物。第一有源层的迁移率高于第二有源层的迁移率。

70.实施例5~8中,第一有源层、第二有源层中的稀土金属氧化物为不同元素不同比例掺杂。

71.具体地,第一有源层、第二有源层采用不同稀土元素且以不同比例掺杂(相对高迁掺杂+相对低迁元素掺杂)时,稀土元素及掺杂摩尔比请详见图7所示,其中,第一有源层中是相对高迁移率元素掺杂,第二有源层中是相对低迁移率元素掺杂。本实施例5~8采用图7参数获得的top-gate架构的阵列基板进行器件特性检测,如阈值电压、迁移率、亚阈值摆幅、开关电流比、pbts、nbtis,检测结果详见图7所示。

72.实施例9~12实施例9~12提供一种esl架构的阵列基板,请参考图2,包括:设置在衬底基板201上的栅极202、栅绝缘层203、有源层204、刻蚀阻挡层205、源极2081、漏极2082、钝化层207。有源层204包括层叠设置的第一有源层2041和第二有源层2042。第一有源层、第二有源层分别包括氧化物半导体(氧化铟锌)和稀土金属氧化物。

73.实施例9~12中,第一有源层、第二有源层中的稀土金属氧化物为同元素不同比例掺杂。

74.具体地,第一有源层、第二有源层采用相同稀土元素且以不同比例掺杂时,稀土元素及掺杂摩尔比请详见图5所示。本实施例9~12采用图5参数获得的esl架构的阵列基板进行器件特性检测,如阈值电压、迁移率、亚阈值摆幅、开关电流比、pbts、nbtis,检测结果详见图5所示。

75.实施例13~16实施例13~16提供一种esl架构的阵列基板,请参考图2,包括:设置在衬底基板201上的栅极202、栅绝缘层203、有源层204、刻蚀阻挡层205、源极2081、漏极2082、钝化层207。有源层204包括层叠设置的第一有源层2041和第二有源层2042。第一有源层、第二有源层分别包括氧化物半导体(氧化铟锌)和稀土金属氧化物。

76.实施例13~16中,第一有源层、第二有源层中的稀土金属氧化物为不同元素不同比例掺杂。

77.具体地,第一有源层、第二有源层采用不同稀土元素且以不同比例掺杂时,稀土元素及掺杂摩尔比请详见图8所示,其中,第一有源层中是相对高迁移率元素掺杂,第二有源

层中是相对低迁移率元素掺杂。本实施例13~16采用图8参数获得的esl架构的阵列基板进行器件特性检测,如阈值电压、迁移率、亚阈值摆幅、开关电流比、pbts、nbtis,检测结果详见图8所示。

78.实施例17~20实施例17~20提供一种bce架构的阵列基板,请参考图1,包括:设置在衬底基板101上的栅极102、栅绝缘层103、有源层104、源极1081、漏极1082、钝化层107。有源层104包括层叠设置的第一有源层1041和第二有源层1042。第一有源层、第二有源层分别包括氧化物半导体(氧化铟锌)和稀土金属氧化物。

79.实施例17~20中,第一有源层、第二有源层中的稀土金属氧化物为同元素不同比例掺杂。

80.具体地,第一有源层、第二有源层采用相同稀土元素且以不同比例掺杂时,稀土元素及掺杂摩尔比请详见图6所示。对实施例17~20采用图6参数获得的bce架构的阵列基板进行器件特性检测,如阈值电压、迁移率、亚阈值摆幅、开关电流比、pbts、nbtis,检测结果详见图6所示。

81.实施例21~24实施例21~24提供一种bce架构的阵列基板,请参考图1,包括:设置在衬底基板101上的栅极102、栅绝缘层103、有源层104、源极1081、漏极1082、钝化层107。有源层104包括层叠设置的第一有源层1041和第二有源层1042。第一有源层、第二有源层分别包括氧化物半导体(氧化铟锌)和稀土金属氧化物。

82.实施例21~24中,第一有源层、第二有源层中的稀土金属氧化物为不同元素不同比例掺杂。

83.具体地,第一有源层、第二有源层采用不同稀土元素且以不同比例掺杂时,稀土元素及掺杂摩尔比请详见图9所示,其中,第一有源层中是相对高迁移率元素掺杂,第二有源层中是相对低迁移率元素掺杂。对实施例21~24采用图9参数获得的bce架构的阵列基板进行器件特性检测,如阈值电压、迁移率、亚阈值摆幅、开关电流比、pbts、nbtis,检测结果详见图9所示。

84.综上,根据图4、图5、图6可知,本技术实施例1~4、9~12、17~20中的阵列基板,其中的第一有源层、第二有源层采用相同元素(铽)以及结合第一有源层更小的掺杂摩尔来实现迁移率差别。

85.根据图7、图8、图9可知,本技术实施例5~8、13~16、21~24中的阵列基板,其中的第一有源层、第二有源层采用不同元素(第一有源层掺杂铽元素,第二有源层掺杂镱元素),以及结合掺杂摩尔使得第一有源层的相对迁移率高。

86.结合图4~6和图7~9,本技术实施例的阵列基板的器件特性优异。例如,实施例1中,阈值电压可以达到-0.5v,迁移率μ可以达到32.9cm2v-1

s-1

,亚阈值摆幅可以为0.3 v/decade,开关电流比约为8

×

106,pbts可以达到0.42v,nbtis可以达到-1.21v;例如,实施例5,阈值电压可以达到0v,迁移率μ可以达到30.7cm2v-1

s-1

,亚阈值摆幅可以为0.3v/decade,开关电流比约在5

×

106,pbts可以达到0.55v,nbtis可以达到-1.03v,等。由此可见,本技术实施例得到的阵列基板具有优异的器件特性,进而可以增加其应用的显示面板的性能。

87.综上所述,本技术通过共掺杂的特定摩尔比的氧化物半导体叠层薄膜,前沟道侧

形成迁移率相对较高、开态电流相对较高的薄膜,可以提高开态电流;在背沟道侧形成迁移率较低和关态电流相对较低的薄膜,可以降低关态电流。

88.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

89.以上对本技术实施例所提供的一种阵列基板和显示面板进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1