CIS的深沟槽隔离结构及其制造方法与流程

cis的深沟槽隔离结构及其制造方法

技术领域

1.本发明涉及半导体集成电路制造领域,特别涉及一种图像传感器(cmos image sensor,cis的深沟槽隔离(deep trench isolation,dti)结构;本发明还涉及一种cis的深沟槽隔离结构的制造方法。

背景技术:

2.在背照式(backside illumination,bsi)cis中,深沟槽隔离结构对改善相邻像素间串扰起到重要作用,而dti的深沟槽刻蚀(et)过程中等离子体(plasma)会在深沟槽表面产生很多缺陷,这些缺陷会成为光电子捕获中心,产生暗电流和白像素,从而影响图像质量。

3.现有改进的技术方案主要包括:

4.1.减薄后离子注入退火;

5.2.引入高介电常数(high-k)薄膜(film),依靠场效应抑制暗电流和白像素。

6.上述技术方案的产品均已量产化,产品性能取决于工艺条件,制备完成后则无法调整。而工艺波动造成品质差异也无法补偿。

技术实现要素:

7.本发明所要解决的技术问题是提供一种cis的深沟槽隔离结构,能对深沟槽隔离结构和半导体衬底之间的界面处的界面态进行调控,能优化界面态并从而减少暗电流和白像素。为此,本发明还提供一种cis的深沟槽隔离结构的制造方法。

8.为解决上述技术问题,本发明提供的cis的深沟槽隔离结构中,第一半导体衬底上包括像素区和外围区;所述外围区环绕在所述像素区的周侧。

9.深沟槽隔离结构形成于所述像素区中,各所述深沟槽隔离结构之间的区域为一个像素单元的形成区域;所述深沟槽隔离结构包括:

10.通过对所述第一半导体衬底的第一表面进行等离子体刻蚀形成于所述第一半导体衬底中的深沟槽,所述深沟槽的顶部表面和所述第一半导体衬底的第一表面相平,所述深沟槽的内侧表面具有由所述等离子体刻蚀产生界面缺陷;各所述深沟槽相连通。

11.形成于所述深沟槽内侧表面的第一半导体外延层。

12.形成于所述深沟槽中的所述第一半导体外延层表面的第二介质层。

13.将所述深沟槽完全填充的第三导电材料层,各所述第三导电材料层的顶部表面和所述第三导电材料层的顶部表面相平。

14.在最靠近所述外围区的所述深沟槽的部分区域中还形成有第四导电材料层,所述第四导电材料层形成于所述第三导电材料层的顶部表面上并延伸到所述深沟槽外部的所述第一半导体衬底的第一表面上;所述第四导电材料层和所述深沟槽外的所述第一半导体衬底的第一表面之间间隔有第五介质层。

15.所述第四导电材料层和外部电极连接。

16.所述外部电极连接到外部控制模块,所述外部控制模块提供外部电压到各所述第三导电材料层上以对所述深沟槽的内侧表面的界面态进行调控,以消除所述界面缺陷对所述界面态的不利影响。

17.进一步的改进是,所述第一半导体衬底包括硅衬底。

18.所述第一半导体外延层包括硅外延层。

19.进一步的改进是,所述第二介质层的材料包括高介电常数层。

20.进一步的改进是,所述第四导电材料层由所述第三导电材料层延伸而成,所述第五介质层由延伸到所述深沟槽外的所述第一半导体外延层和所述第二介质层的叠加而成。

21.进一步的改进是,cis为背照式cis,所述第一半导体衬底的第一表面为背面,所述第一半导体衬底的第二表面为正面。

22.进一步的改进是,所述cis为堆栈式cis。

23.所述第一半导体衬底的第二表面和第二半导体衬底的正面键合。

24.所述第二半导体衬底上形成有逻辑电路。

25.硅通孔从所述第一半导体衬底的背面穿过所述第一半导体衬底的正面并进入到所述第二半导体衬底中,所述第一半导体衬底的正面金属层、所述第二半导体衬底的正面金属层通过所述硅通孔连接。

26.在所述第一半导体衬底的背面还形成有背面介质层和背栅网格层,所述背栅网格层由背面金属图形化形成,所述硅通孔和顶部对应的所述背栅网格层的金属连接,所述第四导电材料层和顶部对应的所述背栅网格层的金属连接。

27.所述第四导电材料层的形成区域外的各所述深沟槽中的所述第三导电材料层和所述背栅网格层的金属之间间隔有所述背面介质层。

28.进一步的改进是,所述深沟槽的深宽比为1~50。

29.为解决上述技术问题,本发明提供的cis的深沟槽隔离结构的制造方法包括如下步骤:

30.步骤一、提供第一半导体衬底,所述第一半导体衬底上包括像素区和外围区;所述外围区环绕在所述像素区的周侧。

31.光刻定义深沟槽的形成区域,对所述第一半导体衬底的第一表面进行等离子体刻蚀在所述第一半导体衬底中的多个所述深沟槽;所述深沟槽位于所述像素区中,各所述深沟槽之间的区域为一个像素单元的形成区域;各所述深沟槽相连通。

32.步骤二、进行外延生长工艺在所述深沟槽内侧表面的第一半导体外延层。

33.步骤三、在所述第一半导体外延层表面形成第二介质层。

34.步骤四、形成第三导电材料层;所述第三导电材料层将所述深沟槽完全填充,各所述第三导电材料层的顶部表面和所述第三导电材料层的顶部表面相平。

35.步骤五、形成第五介质层和第四导电材料层,所述第四导电材料层位于最靠近所述外围区的所述深沟槽的部分区域中,所述第四导电材料层形成于所述第三导电材料层的顶部表面上并延伸到所述深沟槽外部的所述第一半导体衬底的第一表面上;所述第四导电材料层和所述深沟槽外的所述第一半导体衬底的第一表面之间间隔有所述第五介质层。

36.所述第四导电材料层用于和外部电极连接。

37.所述外部电极连接到外部控制模块,所述外部控制模块提供外部电压到各所述第

三导电材料层上以对所述深沟槽的内侧表面的界面态进行调控,以消除所述界面缺陷对所述界面态的不利影响。

38.进一步的改进是,所述第一半导体衬底包括硅衬底。

39.所述第一半导体外延层包括硅外延层。

40.进一步的改进是,所述第二介质层的材料包括高介电常数层。

41.进一步的改进是,步骤二中,所述第一半导体外延层还延伸到所述深沟槽外侧的所述第一半导体衬底的第一表面。

42.步骤五中,所述第五介质层由延伸到所述深沟槽外的所述第一半导体外延层和所述第二介质层的叠加而成。

43.所述第四导电材料层由所述第三导电材料层延伸而成且步骤五整合到步骤四中,步骤四中包括如下分步骤:

44.形成所述第三导电材料层,所述第三导电材料层将所述深沟槽完全填充并延伸到所述深沟槽外部的所述第二介质层的表面上。

45.光刻定义出所述第四导电材料层的形成区域之后对所述第三导电材料层进行刻蚀;刻蚀后,在所述第四导电材料层的形成区域外部,所述第三导电材料层将所述深沟槽完全填充且各所述第三导电材料层的顶部表面和所述第三导电材料层的顶部表面相平;在所述第四导电材料层的形成区域中由保留的所述第三导电材料层将所述深沟槽完全填充以及组成所述第四导电材料层。

46.进一步的改进是,cis为背照式cis,所述第一半导体衬底的第一表面为背面,所述第一半导体衬底的第二表面为正面。

47.进一步的改进是,所述cis为堆栈式cis;步骤五之后还包括:

48.采用键合工艺将所述第一半导体衬底的第二表面和第二半导体衬底的正面键合;所述第二半导体衬底上形成有逻辑电路。

49.形成硅通孔,所述硅通孔从所述第一半导体衬底的背面穿过所述第一半导体衬底的正面并进入到所述第二半导体衬底中,所述第一半导体衬底的正面金属层、所述第二半导体衬底的正面金属层通过所述硅通孔连接。

50.在所述第一半导体衬底的背面还形成背面介质层和背栅网格层,所述背栅网格层由背面金属图形化形成,所述硅通孔和顶部对应的所述背栅网格层的金属连接,所述第四导电材料层和顶部对应的所述背栅网格层的金属连接;所述第四导电材料层的形成区域外的各所述深沟槽中的所述第三导电材料层和所述背栅网格层的金属之间间隔有所述背面介质层。

51.进一步的改进是,所述键合工艺包括混合键合。

52.进一步的改进是,所述深沟槽的深宽比为1~50。

53.本发明对深沟槽隔离结构的填充结构做了特别设置,将填充结构设置为第一半导体外延层、第二介质层和第三导电材料层的叠加结构,这样,第三导电材料层加上电压后就能实现对深沟槽内侧表面的由界面缺陷形成的界面态进行调控,这种调控是在器件形成之后进行的,能消除器件形成过程中的工艺波动对器件的界面态产生的波动影响,所以,本发明能对深沟槽隔离结构和半导体衬底之间的界面处的界面态进行调控,从而能优化界面态并从而减少暗电流和白像素。

54.另外,由于本发明的各深沟槽都互相连通,故各第三导电材料层也都互相电连接,本发明能通过在最靠近外围区的深沟槽的部分区域的第三导电材料层的顶部形成第四导电材料层并通过第四导电材料层和外部电极连接,所以,本发明的深沟槽隔离结构的电极引出结构并不会对像素区的性能带来不利影响。

55.本发明深沟槽隔离结构特别适用于bsi cis以及在bsi cis的基础上形成的stack cis,本发明的深沟槽隔离结构的第四导电材料层顶部的电极引出结构能通过背栅网格层的金属实现,所述本发明的深沟槽隔离结构的电极引出结构容易实现且并不会带来额外的工艺成本。

附图说明

56.下面结合附图和具体实施方式对本发明作进一步详细的说明:

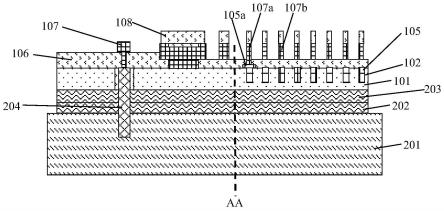

57.图1是本发明实施例cis的深沟槽隔离结构的整体结构示意图;

58.图2a是图1中在最靠近外围区的设置有第四导电材料层的深沟槽隔离结构的放大图;

59.图2b是图1中未设置有第四导电材料层的深沟槽隔离结构的放大图。

具体实施方式

60.如图1所示,是本发明实施例cis的深沟槽隔离结构的整体结构示意图;图2a是图1中在最靠近外围区的设置有第四导电材料层105a的深沟槽隔离结构的放大图;

61.图2b是图1中未设置有第四导电材料层105a的深沟槽隔离结构的放大图。本发明实施例cis的深沟槽隔离结构中,第一半导体衬底101上包括像素区和外围区;所述外围区环绕在所述像素区的周侧。图1中虚线aa左侧为所述外围区,右侧为所述像素区。

62.深沟槽隔离结构形成于所述像素区中,各所述深沟槽隔离结构之间的区域为一个像素单元的形成区域;所述深沟槽隔离结构包括:

63.通过对所述第一半导体衬底101的第一表面进行等离子体刻蚀形成于所述第一半导体衬底101中的深沟槽102,所述深沟槽102的顶部表面和所述第一半导体衬底101的第一表面相平,所述深沟槽102的内侧表面具有由所述等离子体刻蚀产生界面缺陷;各所述深沟槽102相连通。

64.本发明实施例中,所述深沟槽102的深宽比为1~50。

65.形成于所述深沟槽102内侧表面的第一半导体外延层103。

66.本发明实施例中,所述第一半导体衬底101包括硅衬底。

67.所述第一半导体外延层103包括硅外延层。

68.形成于所述深沟槽102中的所述第一半导体外延层103表面的第二介质层104。

69.本发明实施例中,所述第二介质层104的材料包括高介电常数层。

70.将所述深沟槽102完全填充的第三导电材料层105,各所述第三导电材料层105的顶部表面和所述第三导电材料层105的顶部表面相平。

71.在最靠近所述外围区的所述深沟槽102的部分区域中还形成有第四导电材料层105a,所述第四导电材料层105a形成于所述第三导电材料层105的顶部表面上并延伸到所述深沟槽102外部的所述第一半导体衬底101的第一表面上;所述第四导电材料层105a和所

述深沟槽102外的所述第一半导体衬底101的第一表面之间间隔有第五介质层。

72.本发明实施例中,所述第四导电材料层105a由所述第三导电材料层105延伸而成。

73.所述第一半导体外延层103和所述第二介质层104还分别延伸到所述深沟槽102外部。所述第五介质层由延伸到所述深沟槽102外的所述第一半导体外延层103和所述第二介质层104的叠加而成。

74.所述第四导电材料层105a和外部电极连接。

75.所述外部电极连接到外部控制模块,所述外部控制模块提供外部电压到各所述第三导电材料层105上以对所述深沟槽102的内侧表面的界面态进行调控,以消除所述界面缺陷对所述界面态的不利影响。

76.本发明实施例中,cis为背照式cis,所述第一半导体衬底101的第一表面为背面,所述第一半导体衬底101的第二表面为正面。

77.本发明实施例中,在背照式cis的基础上,所述cis为堆栈式cis,图1显示了所述堆栈式cis的结构。

78.所述第一半导体衬底101的第二表面和第二半导体衬底201的正面键合。图1中,所述第一半导体衬底101的第二表面形成有键合层203,所述第二半导体衬底201的正面形成有键合层202,通过键合层202和203实现所述第一半导体衬底101和所述第二半导体衬底201之间的键合。

79.所述第二半导体衬底201上形成有逻辑电路。和背照式cis的区别之处为,背照式cis的逻辑电路也同时形成在所述第一半导体衬底101中。堆栈式cis则将逻辑电路单独用所述第二半导体衬底201形成。

80.硅通孔204从所述第一半导体衬底101的背面穿过所述第一半导体衬底101的正面并进入到所述第二半导体衬底201中,所述第一半导体衬底101的正面金属层(未显示)、所述第二半导体衬底201的正面金属层(未显示)通过所述硅通孔204连接。

81.在所述第一半导体衬底101的背面还形成有背面介质层106和背栅网格层107,所述背栅网格层107由背面金属图形化形成,所述硅通孔204和顶部对应的所述背栅网格层107的金属连接,所述第四导电材料层105a和顶部对应的所述背栅网格层107的金属连接。图1中,单独将所述第四导电材料层105a顶部对应的所述背栅网格层107的金属标记为107a以及单独将所述像素区中未设置所述第四导电材料层105a的所述深沟槽102顶部对应的所述背栅网格层107的金属标记为107b。

82.所述第四导电材料层105a的形成区域外的各所述深沟槽102中的所述第三导电材料层105和所述背栅网格层107的金属之间间隔有所述背面介质层106。

83.图1中还显示了在所述背栅网格层107顶部形成的介质层108。

84.通常,所述像素区中的所述背栅网格层107的金属107a和107b会作为反光格栅即反光条,金属107a和107b设置在对应的所述深沟槽隔离结构的顶部,也即对应于感光单元即像素单元的周围区域设置,也就是说,反光条围成的区域对应于感光单元的区域,使得感光单元周围区域对应于反光条,这样,可以防止相邻的感光单元之间光的串扰。

85.在外围区域中,所述背栅网格层107的金属还组成屏蔽层,以对外围区域的光电信号进行隔离,以使外围区的的cmos器件不被光照射并从而避免产生额外的漏电流。

86.本发明实施例对深沟槽隔离结构的填充结构做了特别设置,将填充结构设置为第

一半导体外延层103、第二介质层104和第三导电材料层105的叠加结构,这样,第三导电材料层105加上电压后就能实现对深沟槽102内侧表面的由界面缺陷形成的界面态进行调控,所以,本发明实施例能对深沟槽隔离结构和半导体衬底之间的界面处的界面态进行调控,从而能优化界面态并从而减少暗电流和白像素。

87.另外,由于本发明实施例的各深沟槽102都互相连通,故各第三导电材料层105也都互相电连接,本发明实施例能通过在最靠近外围区的深沟槽102的部分区域的第三导电材料层105的顶部形成第四导电材料层105a并通过第四导电材料层105a和外部电极连接,所以,本发明实施例的深沟槽隔离结构的电极引出结构并不会对像素区的性能带来不利影响。

88.本发明实施例深沟槽隔离结构特别适用于bsi cis以及在bsi cis的基础上形成的stack cis,本发明的深沟槽隔离结构的第四导电材料层105a顶部的电极引出结构能通过背栅网格层107的金属实现,所述本发明实施例的深沟槽隔离结构的电极引出结构容易实现且并不会带来额外的工艺成本。

89.本发明实施例cis的深沟槽隔离结构的制造方法包括如下步骤:

90.步骤一、提供第一半导体衬底101,所述第一半导体衬底101上包括像素区和外围区;所述外围区环绕在所述像素区的周侧。

91.光刻定义深沟槽102的形成区域,对所述第一半导体衬底101的第一表面进行等离子体刻蚀在所述第一半导体衬底101中的多个所述深沟槽102;所述深沟槽102位于所述像素区中,各所述深沟槽102之间的区域为一个像素单元的形成区域;各所述深沟槽102相连通。

92.本发明实施例方法中,所述第一半导体衬底101包括硅衬底。

93.所述深沟槽102的深宽比为1~50。

94.步骤二、进行外延生长工艺在所述深沟槽102内侧表面的第一半导体外延层103。

95.本发明实施例方法中,所述第一半导体外延层103包括硅外延层。

96.所述第一半导体外延层103还延伸到所述深沟槽102外侧的所述第一半导体衬底101的第一表面。

97.步骤三、在所述第一半导体外延层103表面形成第二介质层104。

98.本发明实施例方法中,所述第二介质层104的材料包括高介电常数层。

99.步骤四、形成第三导电材料层105;所述第三导电材料层105将所述深沟槽102完全填充,各所述第三导电材料层105的顶部表面和所述第三导电材料层105的顶部表面相平。

100.步骤五、形成第五介质层和第四导电材料层105a,所述第四导电材料层105a位于最靠近所述外围区的所述深沟槽102的部分区域中,所述第四导电材料层105a形成于所述第三导电材料层105的顶部表面上并延伸到所述深沟槽102外部的所述第一半导体衬底101的第一表面上;所述第四导电材料层105a和所述深沟槽102外的所述第一半导体衬底101的第一表面之间间隔有所述第五介质层。

101.所述第四导电材料层105a用于和外部电极连接。

102.所述外部电极连接到外部控制模块,所述外部控制模块提供外部电压到各所述第三导电材料层105上以对所述深沟槽102的内侧表面的界面态进行调控,以消除所述界面缺陷对所述界面态的不利影响。

103.本发明实施例方法中,步骤五中,所述第五介质层由延伸到所述深沟槽102外的所述第一半导体外延层103和所述第二介质层104的叠加而成。

104.所述第四导电材料层105a由所述第三导电材料层105延伸而成且步骤五整合到步骤四中,步骤四中包括如下分步骤:

105.形成所述第三导电材料层105,所述第三导电材料层105将所述深沟槽102完全填充并延伸到所述深沟槽102外部的所述第二介质层104的表面上。

106.光刻定义出所述第四导电材料层105a的形成区域之后对所述第三导电材料层105进行刻蚀;刻蚀后,在所述第四导电材料层105a的形成区域外部,所述第三导电材料层105将所述深沟槽102完全填充且各所述第三导电材料层105的顶部表面和所述第三导电材料层105的顶部表面相平;在所述第四导电材料层105a的形成区域中由保留的所述第三导电材料层105将所述深沟槽102完全填充以及组成所述第四导电材料层105a。

107.本发明实施例方法中,cis为背照式cis,所述第一半导体衬底101的第一表面为背面,所述第一半导体衬底101的第二表面为正面。

108.在背照式cis的基础上,所述cis为堆栈式cis;步骤五之后还包括:

109.采用键合工艺将所述第一半导体衬底101的第二表面和第二半导体衬底201的正面键合;所述第二半导体衬底201上形成有逻辑电路。

110.所述键合工艺包括混合键合。

111.所述键合工艺的步骤包括:如图1所示,在所述第一半导体衬底101的第二表面形成键合层203,所述第二半导体衬底201的正面形成键合层202,通过键合层202和203实现所述第一半导体衬底101和所述第二半导体衬底201之间的键合。

112.形成硅通孔204,所述硅通孔204从所述第一半导体衬底101的背面穿过所述第一半导体衬底101的正面并进入到所述第二半导体衬底201中,所述第一半导体衬底101的正面金属层、所述第二半导体衬底201的正面金属层通过所述硅通孔204连接。

113.在所述第一半导体衬底101的背面还形成背面介质层106和背栅网格层107,所述背栅网格层107由背面金属图形化形成,所述硅通孔204和顶部对应的所述背栅网格层107的金属连接,所述第四导电材料层105a和顶部对应的所述背栅网格层107的金属连接;所述第四导电材料层105a的形成区域外的各所述深沟槽102中的所述第三导电材料层105和所述背栅网格层107的金属之间间隔有所述背面介质层106。

114.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1