包括无铜过孔的集成电路互连结构的制作方法

背景技术:

1、电子设备应用中对更高性能的集成电路(ic)的需求推动了晶体管架构的日益密集。随着互连金属化结构的密度与晶体管密度保持同步,互连寄生成为更大的挑战。例如,与ic的互连相关联的电阻-电容(rc)延迟随着互连的密度而增加。

2、图1a示出了在第一互连级内包括金属线101的传统互连结构。金属线101的横向宽度具有一些横向临界尺寸cd1。电介质材料102在金属线101上方,并且通过电介质材料102在z维度上减材地图案化出过孔开口103,以暴露金属线101的一部分。过孔103具有与电介质材料102的厚度相关联的深度dv。过孔103的直径具有一些横向临界尺寸cd2。通常,cd2被制成为比cd1小足以确保过孔103将着陆在金属线101上的量。深度dv与cd2的比率被称为过孔103的纵横比。随着金属线密度随晶体管密度增加而增加,金属线宽度cd1按比例缩小,因此cd2也必须按比例缩小,并且过孔103的纵横比增加。

3、如图1b进一步所示,用一种或多种金属填充过孔103和沟槽106,以形成金属线108,金属线108在x-y维度上延伸,以与过孔103中的导电材料相交,使得两个互连级电连接。在这个双镶嵌示例中,衬层105在沟槽106和过孔103的表面上。衬层105可以包括阻挡材料,以防止填充材料107扩散/迁移出互连结构,因为填充材料107的任何损失通常对集成电路来说都是灾难性的。衬层材料105还可以包括粘合材料,而不是阻挡材料,或者作为阻挡材料的补充。无论包括阻挡材料层、粘合材料层还是两者,衬层材料105通常具有比填充材料107(其通常是铜)显著更高的电阻。随着结构尺寸的缩小,衬层材料105有成为互连结构的更大部分的危险,从而导致更高的互连电阻。

4、采用双镶嵌互连技术,填充金属107同时沉积(例如,电镀)到沟槽106和/或过孔103中,并且因此衬层材料105只需在填充过孔103和沟槽106两者之前沉积一次。然而,由于互连特征不断缩小,双镶嵌处理变得更具挑战性。为了应对这一挑战,ic制造工艺开始更加高度依赖于单镶嵌互连技术。在单镶嵌互连技术中,过孔和线的形成是分开的。例如,可以在电介质材料中限定过孔开口,并且然后用金属化填充过孔开口,以形成过孔。随后,在过孔上方沉积另一电介质层,并且然后在该电介质层中限定沟槽,并且用线金属化填充沟槽。由于沟槽暴露过孔,因此另一衬层材料可以延伸跨过过孔的顶部界面。由于具有过孔的衬层材料界面可以显著增加互连结构的电阻,因此根据单镶嵌技术制造的互连结构会遭受高电阻。

5、因此,允许制造具有较低电阻的互连结构的单镶嵌互连技术在集成电路工业中具有商业优势。

技术实现思路

技术特征:

1.一种集成电路(ic)互连结构,包括:

2.根据权利要求1所述的ic互连结构,其中,所述过孔包括主要处于所述第一相中的过孔金属。

3.根据权利要求2所述的ic互连结构,其中,所述过孔金属具有超过20nm的平均晶粒直径。

4.根据权利要求1-3中任一项所述的ic互连结构,其中,所述阻挡材料的在所述填充金属与下层电介质材料之间的第二部分主要处于具有四方晶体结构的第二相中。

5.根据权利要求2-3中任一项所述的ic互连结构,其中:

6.根据权利要求5所述的ic互连结构,其中,所述过孔金属包括:

7.根据权利要求6所述的ic互连结构,其中,所述衬层包括至少50at.%的w。

8.根据权利要求6所述的ic互连结构,其中,所述衬层包括w、c和n。

9.根据权利要求6所述的ic互连结构,其中,所述填充金属还包括f,并且其中,所述衬层包括基本上纯w并且不含f。

10.根据权利要求2-3中任一项所述的ic互连结构,其中,所述过孔金属包括与电介质材料的侧壁接触的绝大部分的mo。

11.一种计算机平台,包括:

12.根据权利要求11所述的计算机平台,其中,所述ic包括微处理器。

13.一种制造集成电路(ic)互连结构的方法,所述方法包括:

14.根据权利要求13所述的方法,其中,沉积所述第二层的过孔金属包括w或mo的物理气相沉积(pvd)、化学气相沉积(cvd)或原子层沉积(ald)。

15.根据权利要求14所述的方法,其中,沉积所述第二层的过孔金属包括cvd或ald,并且其中,所述cvd或所述ald包括将所述ic互连结构加热至不超过325℃。

16.根据权利要求15所述的方法,其中,所述cvd或所述ald还包括提供h2作为第一前体。

17.根据权利要求16所述的方法,其中,所述cvd或所述ald还包括提供wf6作为第二前体。

18.根据权利要求17所述的方法,其中,所述cvd或所述ald还包括提供包括mo的无机前体或金属有机前体作为第二前体。

19.根据权利要求13-16中任一项所述的方法,其中,沉积所述第一层的过孔金属包括:mo的原子层沉积(ald);w或mo的物理气相沉积(pvd);或者mo的等离子体增强化学气相沉积(pecvd)或还包括c和n的w化合物的等离子体增强化学气相沉积。

20.根据权利要求19所述的方法,其中,沉积所述第一层的过孔金属包括w、c和n的pecvd,并且其中,所述pecvd包括将所述ic互连结构加热至不超过325℃。

21.根据权利要求13-16中任一项所述的方法,其中:

技术总结

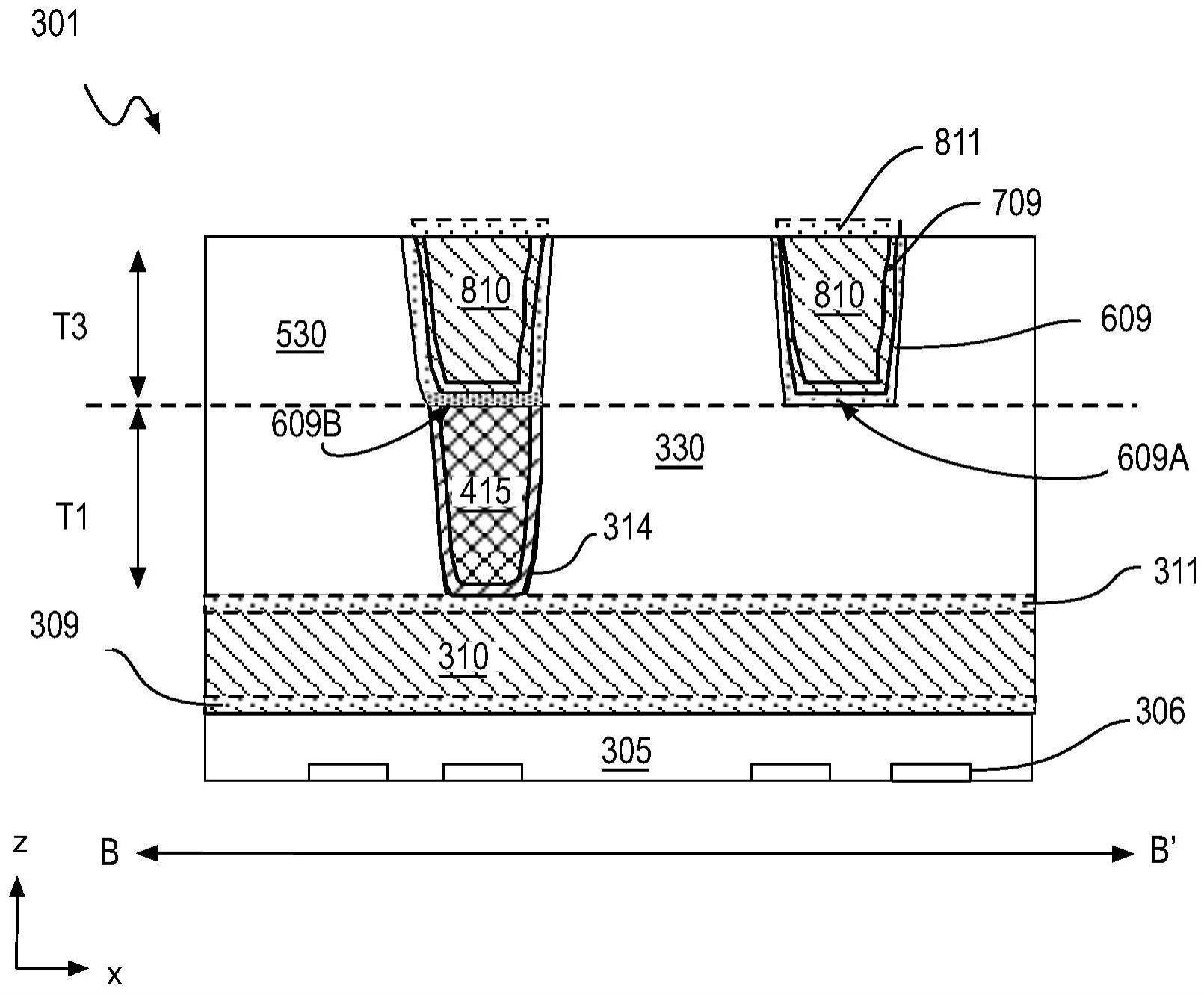

一种集成电路互连结构,与单镶嵌技术兼容,并且包括非铜过孔,该过孔包括低电阻率的(一种或多种)金属,该金属可以在低温下以同样确保良好粘合的方式沉积。适用于非铜过孔的(一种或多种)金属可以具有BCC结晶度,其可以有利地在上级互连特征的扩散阻挡层内模板化出有利的结晶度,从而进一步降低互连结构的电阻。

技术研发人员:D·B·奥布莱恩,J·S·莱布,J·Y·银,C-H·简,P·白,S·安,P·S·普列汉诺夫,D·巴苏

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!