接地屏蔽结构和半导体器件的制作方法

本发明涉及半导体制造领域,特别涉及一种接地屏蔽结构和半导体器件。

背景技术:

1、在现有集成电路,电感是一种重要的半导体器件。电感被广泛应用于低噪声放大器(low noise amplifier,lna)、压控振荡器(voltage-controlled oscillation,vco)等射频电路中。电感的性能参数直接影响了集成电路的性能。

2、集成电路中的电感大多为平面电感,如平面螺旋电感。与传统的线绕电感相比,平面电感具有成本低、易集成、噪声小和功耗低的优点,更重要的是它还能与现有集成电路工艺兼容。

3、衡量电感性能好坏的一个重要指标是品质因数q。品质因数q越高,代表电感的性能越好。电感品质因数q的定义为:存储于电感中的能量和每一个振荡周期损耗能量的比值。

4、但是现有的电感的品质因数往往不甚理想。

技术实现思路

1、本发明解决的问题是如何进一步提高电感的品质因数。

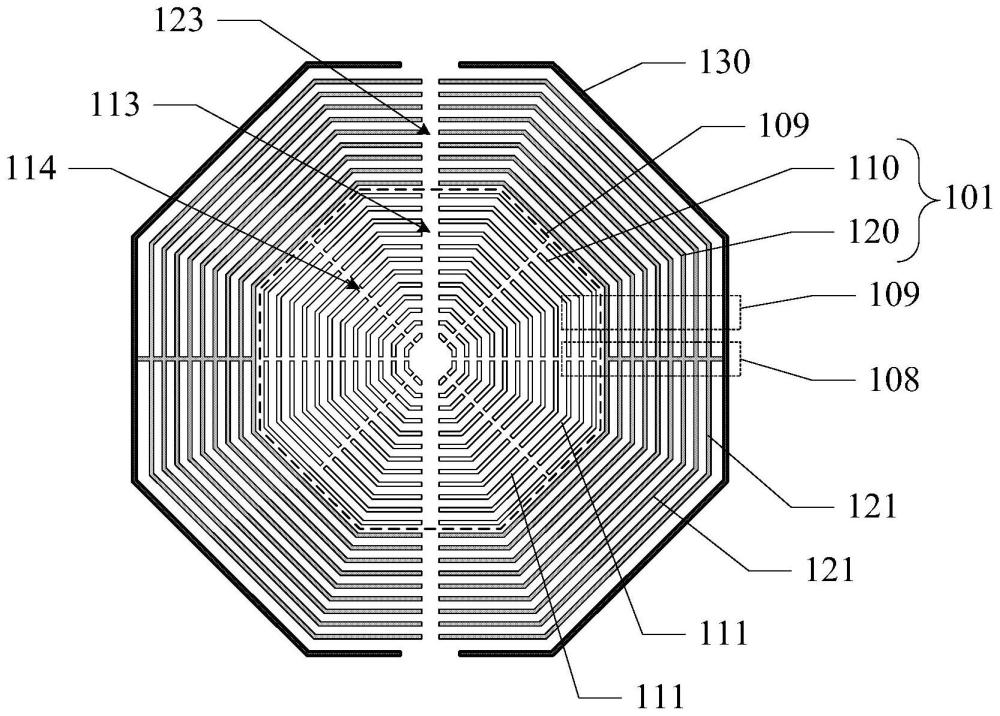

2、为解决上述问题,本发明提供一种接地屏蔽结构,包括:

3、基底;至少1个屏蔽层,所述屏蔽层位于所述基底上,所述屏蔽层包括:第一导电结构和第二导电结构,其中平行基底表面的平面内,所述第二导电结构包围所述第一导电结构,且所述第二导电结构与所述第一导电结构电隔离;接地环,所述接地环位于所述基底上,平行基底表面的平面内,所述接地环包围所述至少1个屏蔽层。

4、可选的,所述第一导电结构包括多个第一导电线段,任意2个所述第一导电线段之间电隔离。

5、可选的,平行所述基底表面的平面内,所述多个第一导电线段围成至少1个第一导电环。

6、可选的,平行所述基底表面的平面内,所述多个第一导电线段围成多个第一导电环,多个所述第一导电环同心设置。

7、可选的,所述第一导电环为开口环。

8、可选的,所述第一导电环的开口数量大于2。

9、可选的,所述第二导电结构包括:多个第二导电线段,所述多个第二导电线段相互电连接;平行所述基底表面的平面内,所述多个第二导电线段围成至少1个第二导电环;所述第二导电环与所述第一导电环同心设置。

10、可选的,所述第一导电环的至少1个开口为第一开口;所述第二导电环为开口环,所述第二导电环的开口与所述第一开口位置对应。

11、可选的,所述接地环与所述第二导电结构电连接。

12、可选的,所述第二导电结构还包括:第二连接段,所述第二连接段连接相邻第二导电线段。

13、可选的,所述接地屏蔽结构具有多个所述屏蔽层,多个所述屏蔽层沿垂直所述基底表面的方向层叠设置;相邻屏蔽层的第二导电结构之间具有插塞;所述插塞的位置与所述第二连接段的位置对应。

14、可选的,所述接地屏蔽结构具有多个所述屏蔽层,多个所述屏蔽层沿垂直所述基底表面的方向层叠设置;相邻屏蔽层的第一导电结构电隔离。

15、相应的,本发明还提供一种半导体器件,包括:

16、接地屏蔽结构,所述接地屏蔽结构为本发明的接地屏蔽结构;感应元件,所述感应元件位于所述接地屏蔽结构上。

17、可选的,在所述基底表面,所述接地环的投影包围所述感应元件的投影。

18、可选的,所述感应元件包括:线圈,在所述基底表面,所述线圈的投影包围所述第一导电结构的投影。

19、可选的,所述线圈的投影位于所述第二导电结构的投影范围内。

20、可选的,所述感应器元件为电感或变压器。

21、与现有技术相比,本发明的技术方案具有以下优点:

22、本发明技术方案中,屏蔽层中,与接地环相连的第二导电结构与第一导电结构电隔离,而且其中第二导电结构包围第一导电结构的。仅有第二导电结构接地,位于感应磁场更强的中心的第一导电结构并未接地,浮置的第一导电结构能够有效增大接地屏蔽结构的电阻,有效抑制衬底损耗,有利于品质因数q值的提高。

23、本发明可选方案中,第一导电环为开口环,第一导电环的开口数量大于2,也就会说,位于中心的第一导电环被截断为更多的部分,每一部分的长度更短,能够有效抑制涡流,有利于品质因数q值的提高。

技术特征:

1.一种接地屏蔽结构,其特征在于,包括:

2.如权利要求1所述的接地屏蔽结构,其特征在于,所述第一导电结构包括多个第一导电线段,任意2个所述第一导电线段之间电隔离。

3.如权利要求2所述的接地屏蔽结构,其特征在于,平行所述基底表面的平面内,所述多个第一导电线段围成至少1个第一导电环。

4.如权利要求3所述的接地屏蔽结构,其特征在于,平行所述基底表面的平面内,所述多个第一导电线段围成多个第一导电环,多个所述第一导电环同心设置。

5.如权利要求3所述的接地屏蔽结构,其特征在于,所述第一导电环为开口环。

6.如权利要求5所述的接地屏蔽结构,其特征在于,所述第一导电环的开口数量大于2。

7.如权利要求5所述的接地屏蔽结构,其特征在于,所述第二导电结构包括:多个第二导电线段,所述多个第二导电线段相互电连接;平行所述基底表面的平面内,所述多个第二导电线段围成至少1个第二导电环;

8.如权利要求7所述的接地屏蔽结构,其特征在于,所述第一导电环的至少1个开口为第一开口;

9.如权利要求1所述的接地屏蔽结构,其特征在于,所述接地环与所述第二导电结构电连接。

10.如权利要求9所述的接地屏蔽结构,其特征在于,所述第二导电结构还包括:第二连接段,所述第二连接段连接相邻第二导电线段。

11.如权利要求10所述的接地屏蔽结构,其特征在于,所述接地屏蔽结构具有多个所述屏蔽层,多个所述屏蔽层沿垂直所述基底表面的方向层叠设置;

12.如权利要求1所述的接地屏蔽结构,其特征在于,所述接地屏蔽结构具有多个所述屏蔽层,多个所述屏蔽层沿垂直所述基底表面的方向层叠设置;相邻屏蔽层的第一导电结构电隔离。

13.一种半导体器件,其特征在于,包括:

14.如权利要求13所述的半导体器件,其特征在于,在所述基底表面,所述接地环的投影包围所述感应元件的投影。

15.如权利要求13所述的半导体器件,其特征在于,所述感应元件包括:线圈,在所述基底表面,所述线圈的投影包围所述第一导电结构的投影。

16.如权利要求15所述的半导体器件,其特征在于,所述线圈的投影位于所述第二导电结构的投影范围内。

17.如权利要求13所述的半导体器件,其特征在于,所述感应器元件为电感或变压器。

技术总结

一种接地屏蔽结构和半导体器件,所述接地屏蔽结构包括:基底;至少1个屏蔽层,屏蔽层位于基底上,屏蔽层包括:第一导电结构和第二导电结构,其中平行基底表面的平面内,第二导电结构包围第一导电结构,且第二导电结构与第一导电结构电隔离;接地环,接地环位于基底上,平行基底表面的平面内,接地环包围至少1个屏蔽层。仅有第二导电结构接地,位于感应磁场更强的中心的第一导电结构并未接地,浮置的第一导电结构能够有效增大接地屏蔽结构的电阻,有效抑制衬底损耗,有利于品质因数Q值的提高。

技术研发人员:王晓东,王西宁,钱蔚宏,刘慕义

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/4/22

- 还没有人留言评论。精彩留言会获得点赞!