半导体器件表面钝化结构及其制备方法与流程

本申请涉及半导体,尤其是涉及一种半导体器件表面钝化结构及其制备方法。

背景技术:

1、对于高性能高可靠性集成电路来说,表面钝化已成为不可缺少的工艺措施之一。钝化工艺是在半导体器件表面覆盖保护介质膜,以防止表面污染的工艺。

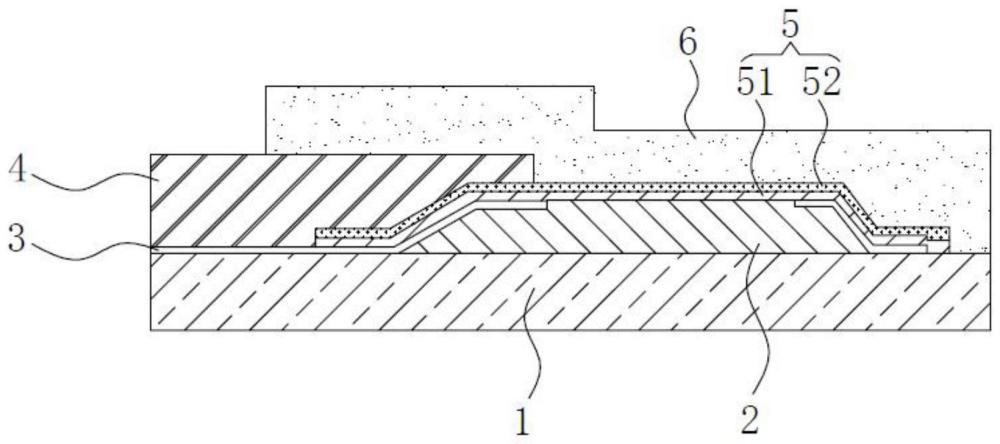

2、如图1所示,为一种半导体器件表面钝化结构,包括外延薄膜,且在外延薄膜表面自下而上依次覆盖有场板介质、势垒金属、焊接金属、介质层和钝化层。从图中可以看出,焊接金属上面的介质层为二氧化硅或二氧化硅与氮化硅结合的结构。

3、在上述结构中,器件通过温度冲击或者温度循环实验后,介质层由于应力原因容易出现裂纹,增加器件失效风险。

技术实现思路

1、为了改善目前半导体器件表面钝化结构经过温度冲击或者温度循环试验后出现裂纹的问题,本申请提供一种半导体器件表面钝化结构及其制备方法。

2、第一方面,本申请提供的一种半导体器件表面钝化结构采用如下的技术方案:

3、一种半导体器件表面钝化结构,包括外延基片、场板介质和势垒层,势垒层位于场板介质周围的外延基片上,势垒层靠近场板介质的一端覆盖于场板介质上,钝化结构还包括焊接层、复合介质层和外涂层,复合介质层覆盖于场板介质和势垒层上,焊接层位于一侧的势垒层和复合介质层上,外涂层位于复合介质层上,外涂层的一端延伸至焊接层上和另一端覆盖在外延基片上;

4、复合介质层包括自下而上设置的第一介质层和第二介质层;第一介质层为二氧化硅层,第二介质层为氮化硅层。

5、通过采用上述技术方案,半导体器件表面钝化结构在经过温度循环试验后,产生裂纹可能性极低甚至不会出现裂纹,本申请提供的制备工艺能够制作出具有良好抗裂性能的半导体器件表面钝化结构,并能够提高防水性能,可靠性高。

6、第二方面,本申请提供的一种半导体器件表面钝化结构的制备方法采用如下的技术方案:

7、一种半导体器件表面钝化结构的制备方法,包括以下步骤:

8、s1,在外延基片上沉积场板介质,并在氧气环境下退火增密,对场板介质进行光刻,再图形化处理;

9、s2,沉积势垒层,光刻并图形化处理;

10、s3,对势垒层退火处理;

11、s4,沉积复合介质层,光刻,然后干法刻蚀;

12、s5,沉积焊接层,光刻并图形化处理;

13、s6,外涂层涂敷,图形化处理后固化。

14、通过采用上述技术方案,能够制造出可靠性高的半导体器件表面钝化结构,在经过温度循环试验后,产生裂纹可能性极低甚至不会出现裂纹。

15、综上,本申请包括以下至少一种有益技术效果:

16、1、提供一种新的半导体器件表面钝化结构,复合介质层伸入至焊接层与势垒层之间,这样在经过温度循环试验后,产生裂纹可能性极低甚至不会出现裂纹;

17、2、提供一种制作上述钝化结构的方法,制作出的钝化结构抗裂性提升,并具有高防水性能。

技术特征:

1.一种半导体器件表面钝化结构,包括外延基片(1)、场板介质(2)和势垒层(3),势垒层(3)位于场板介质(2)周围的外延基片(1)上,势垒层(3)靠近场板介质(2)的一端覆盖于场板介质(2)上,其特征在于:钝化结构还包括焊接层(4)、复合介质层(5)和外涂层(6),复合介质层(5)覆盖于场板介质(2)和势垒层(3)上,焊接层(4)位于一侧的势垒层(3)和复合介质层(5)上,外涂层(6)位于复合介质层(5)上,外涂层(6)的一端延伸至焊接层(4)上和另一端覆盖在外延基片(1)上;

2.根据权利要求1所述的半导体器件表面钝化结构,其特征在于:外延基片(1)材料为硅或碳化硅;场板介质(2)为0.1-5um的二氧化硅层;势垒层(3)与焊接层(4)均为ti、ni、al、cu、au、ag、mo、w、tiw、tic、fe、cr中的单层薄膜或多种复合薄膜组成,薄膜厚度均为0.001um~10um。

3.一种半导体器件表面钝化结构的制备方法,其特征在于:包括以下步骤:

4.根据权利要求3所述的半导体器件表面钝化结构的制备方法,其特征在于:步骤s3中势垒层(3)的退火处理方式为rta或la,处理过程中气体氛围为真空或惰性气体氛围。

5.根据权利要求4所述的半导体器件表面钝化结构的制备方法,其特征在于:步骤s4中先进行二氧化硅淀积形成第一介质层(51),再进行氮化硅淀积形成第二介质层(52)。

6.根据权利要求3-5任一所述的半导体器件表面钝化结构的制备方法,其特征在于:步骤s6中,外涂层(6)的固化温度为300-400℃,时间为0.5-18h。

7.根据权利要求3-5任一所述的半导体器件表面钝化结构的制备方法,其特征在于:步骤s1中,场板介质(2)采用pecvd淀积0.1-5um,退火增密条件为:温度800-1300℃,时间10-200min。

8.根据权利要求3-5任一所述的半导体器件表面钝化结构的制备方法,其特征在于:步骤s1中,场板介质(2)采用lpteos淀积0.1-5um,退火增密条件为:温度800-1300℃,时间10-200min。

9.根据权利要求3-5任一所述的半导体器件表面钝化结构的制备方法,其特征在于:步骤s1中,场板介质(2)采用淀积二氧化硅淀积0.1-5um,退火增密条件为:温度700-1100℃,时间10-200min。

10.根据权利要求3-5任一所述的半导体器件表面钝化结构的制备方法,其特征在于:场板介质(2)采用boe腐蚀液刻蚀,刻蚀温度为20℃-60℃,刻蚀时间为1-20min;boe刻蚀液为氢氟酸与水或氟化铵与水混合而成,氢氟酸或氟化铵与水的配比为1:(1~8)。

技术总结

本申请涉及一种半导体器件表面钝化结构及其制备方法,涉及半导体技术领域,半导体器件表面钝化结构包括外延基片、场板介质和势垒层,还包括焊接层、复合介质层和外涂层,复合介质层覆盖于场板介质和势垒层上,焊接层位于一侧的势垒层和复合介质层上,外涂层位于复合介质层上,外涂层的一端延伸至焊接层上和另一端覆盖在外延基片上;其制备方法包括:S1,在外延基片上沉积场板介质,对场板介质进行光刻,再图形化处理;S2,沉积势垒层,光刻并图形化处理;S3,对势垒层退火处理;S4,沉积复合介质层,光刻,然后干法刻蚀;S5,沉积焊接层,光刻并图形化处理;S6,外涂层涂敷,图形化处理后固化。该申请具有提高半导体器件可靠性的优点。

技术研发人员:郑柳

受保护的技术使用者:重庆伟特森电子科技有限公司

技术研发日:

技术公布日:2024/5/20

- 还没有人留言评论。精彩留言会获得点赞!