逆导型IGBT器件及其形成方法与流程

逆导型igbt器件及其形成方法

技术领域

1.本技术涉及半导体集成电路制造技术领域,具体涉及一种逆导型igbt器件及其形成方法。

背景技术:

2.绝缘栅双极型晶体管(insulated gate bipolar transistor,igbt)器件是电力电子系统能量控制和转换的重要开关元器件之一,其性能直接影响着电力电子系统的转换效率、体积和重量。

3.逆导igbt器件是指在igbt器件的背面形成局部重掺杂区来实现在igbt器件中集成快恢复二极管(fast recovery diode,frd),由于其具有更好的性能,更低的成本,目前已经越来越广泛地应用于市场中。

4.通常,应用于电力电子系统的逆导型igbt器件基于双重扩散金属氧化物半导体(double-diffused metal oxide semiconductor,dmos),其具有垂直的器件结构(例如,其可以是垂直的n(negative)型-p(positive)型-n型双栅极晶体管)。

5.然而,基于dmos的逆导型igbt器件的漂移区电场分布沿垂直方向呈现为单峰值曲线,且其衬底较厚,电阻率较大。鉴于此,亟待提供一种漂移区电场分布较为均匀且电阻率较小的逆导型igbt器件。

技术实现要素:

6.本技术提供了一种逆导型igbt器件及其形成方法,可以解决相关技术中提供的的基于dmos的逆导型igbt器件的电学性能较差的问题。

7.一方面,本技术实施例提供了一种逆导型igbt器件的形成方法,包括:

8.提供一衬底,所述衬底中形成有第一沟槽和第二沟槽,所述衬底、所述第一沟槽和所述第二沟槽的表面形成有栅介质层,所述第一沟槽中填充有第一栅极,所述第二沟槽中填充有第二栅极,所述衬底的正面至第一深度形成有第一掺杂区,所述衬底的正面至第二深度形成有第一重掺杂区,所述衬底的正面是所述第一沟槽和所述第二沟槽的开口指向的衬底的表面,所述第二深度小于所述第一深度;

9.进行离子注入,在所述第一栅极和所述第二栅极之间形成柱形掺杂区,所述柱形掺杂区的底部低于所述第一栅极和所述第二栅极的底部,所述柱形掺杂区的顶部低于所述第一栅极和所述第二栅极的顶部;

10.在所述衬底的正面形成第一金属层,所述第一金属层用于引出第一重掺杂区和第一掺杂区;

11.对所述衬底的背面进行减薄处理,所述衬底的背面是所述第一沟槽和所述第二沟槽的底部指向的衬底的表面;

12.进行离子注入,在所述衬底的背面至第三深度形成第二掺杂区;

13.进行离子注入,在所述衬底的背面至第四深度形成第二重掺杂区,所述第四深度

小于所述第三深度;

14.进行离子注入,在所述第二重掺杂区中形成第三重掺杂区和第四重掺杂区,所述第三重掺杂区和所述第四重掺杂区不接触;

15.在所述衬底的背面形成第二金属层。

16.在一些实施例中,所述第一掺杂区、所述柱形掺杂区、所述第二重掺杂区掺杂有第一类型的杂质,所述第一重掺杂区、所述第二掺杂区、所述第三重掺杂区和所述第四重掺杂区掺杂有第二类型的杂质。

17.在一些实施例中,所述第三重掺杂区、所述第四重掺杂区和所述第二重掺杂区的深度相同。

18.在一些实施例中,所述第一掺杂区为所述igbt器件的阱区,所述第二掺杂区为所述igbt器件的场截止区。

19.在一些实施例中,所述在所述衬底的正面形成第一金属层,包括:

20.在所述栅介质层、所述第一栅极和所述第二栅极上形成缓冲层;

21.在所述第一栅极和所述第二栅极之间形成第三沟槽,所述第三沟槽的底部低于所述第一重掺杂区的底部且高于所述第一掺杂区的底部;

22.在所述缓冲层上形成第一金属层,所述第一金属层填充所述第三沟槽。

23.另一方面,本技术实施例提供了一种逆导型igbt器件,包括:

24.衬底,所述衬底中形成有第一沟槽和第二沟槽,所述衬底、所述第一沟槽和所述第二沟槽的表面形成有栅介质层,所述第一沟槽中填充有第一栅极,所述第二沟槽中填充有第二栅极;

25.所述衬底的正面至第一深度形成有第一掺杂区,所述衬底的正面至第二深度形成有第一重掺杂区,所述衬底的背面至第三深度形成有第二掺杂区,所述衬底的背面至第四深度形成有第二重掺杂区,所述第二重掺杂区中形成第三重掺杂区和第四重掺杂区,所述第三重掺杂区和所述第四重掺杂区不接触,所述衬底的正面是所述第一沟槽和所述第二沟槽的开口指向的衬底的表面,所述衬底的背面是所述第一沟槽和所述第二沟槽的底部指向的衬底的表面,所述第二深度小于所述第一深度,所述第四深度小于所述第三深度;

26.所述第一栅极和所述第二栅极之间形成柱形掺杂区,所述柱形掺杂区的底部低于所述第一栅极和所述第二栅极的底部,所述柱形掺杂区的顶部低于所述第一栅极和所述第二栅极的顶部。

27.在一些实施例中,所述栅介质层、所述第一栅极和所述第二栅极上形成有缓冲层;

28.所述第一栅极和所述第二栅极之间形成有第三沟槽,所述第三沟槽的底部低于所述第一重掺杂区的底部且高于所述第一掺杂区的底部;

29.所述缓冲层上形成有第一金属层,所述第一金属层填充所述第三沟槽。

30.在一些实施例中,所述第一掺杂区、所述柱形掺杂区、所述第二重掺杂区掺杂有第一类型的杂质,所述第一重掺杂区、所述第二掺杂区、所述第三重掺杂区和所述第四重掺杂区掺杂有第二类型的杂质。

31.在一些实施例中,所述第三重掺杂区、所述第四重掺杂区和所述第二重掺杂区的深度相同。

32.在一些实施例中,所述第一掺杂区为所述igbt器件的阱区,所述第二掺杂区为所

述igbt器件的场截止区。

33.本技术技术方案,至少包括如下优点:

34.本技术通过在逆导型igbt器件的第一栅极和第二栅极之间下方的台面区域形成柱形掺杂区,从而将漂移区电场转变为沿垂直方向的近均匀分布,提高了器件的击穿电压;同时,通过对衬底的背面进行减薄处理,降低了衬底的厚度和电阻率,进而提高了器件的电学性能。

附图说明

35.为了更清楚地说明本技术具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

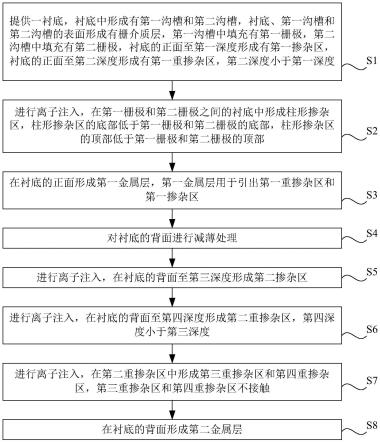

36.图1是本技术一个示例性实施例提供的逆导型igbt器件的形成方法的流程图;

37.图2至图9是本技术一个示例性实施例提供的逆导型igbt器件的形成示意图。

具体实施方式

38.下面将结合附图,对本技术中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本技术的一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在不做出创造性劳动的前提下所获得的所有其它实施例,都属于本技术保护的范围。

39.在本技术的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

40.在本技术的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电气连接;可以是直接相连,也可以通过中间媒介间接相连,还可以是两个元件内部的连通,可以是无线连接,也可以是有线连接。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本技术中的具体含义。

41.此外,下面所描述的本技术不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

42.参考图1,其示出了本技术一个示例性实施例提供的逆导型igbt器件的形成方法的流程图,如图1所示,该方法包括:

43.步骤s1,提供一衬底,衬底中形成有第一沟槽和第二沟槽,衬底、第一沟槽和第二沟槽的表面形成有栅介质层,第一沟槽中填充有第一栅极,第二沟槽中填充有第二栅极,衬底的正面至第一深度形成有第一掺杂区,衬底的正面至第二深度形成有第一重掺杂区,第二深度小于第一深度。

44.参考图2,其示出了在形成柱形掺杂区之前的剖面示意图。示例性的,如图2所示,

衬底210中形成有第一沟槽301和第二沟槽302,衬底210、第一沟槽301和第二沟槽302的表面形成有栅介质层220,第一沟槽301中填充有第一栅极231,第二沟槽302中填充有第二栅极232,衬底210的正面至第一深度形成有第一掺杂区201,衬底的正面至第二深度形成有第一重掺杂区202,第二深度小于第一深度。

45.其中,衬底210的正面是第一沟槽301和第二沟槽302的开口指向的衬底210的表面,相对应的,衬底210的背面是第一沟槽301和第二沟槽302的底部指向的衬底210的表面,衬底210的厚度为h1;第一掺杂区201可作为逆导型igbt器件的阱(well)区,第一沟槽301和第二沟槽302的尺寸(深度和宽度)相同,其(第一沟槽301或第二沟槽302)深度和宽度的比值大于3。

46.步骤s2,进行离子注入,在第一栅极和第二栅极之间的衬底中形成柱形掺杂区,柱形掺杂区的底部低于第一栅极和第二栅极的底部,柱形掺杂区的顶部低于第一栅极和第二栅极的顶部。

47.参考图3,其示出了形成柱形掺杂区后的剖面示意图。示例性的,可通过光刻工艺覆盖光阻,打开柱形掺杂区203上方的区域,进行离子注入,在第一栅极231和第二栅极232之间的衬底210中形成柱形掺杂区203,去除光阻。其中,柱形掺杂区203的高度和宽度的比值大于2。

48.步骤s3,在衬底的正面形成第一金属层,第一金属层用于引出第一重掺杂区和第一掺杂区。

49.示例性的,步骤s3包括但不限于:在栅介质层、第一栅极和第二栅极上形成缓冲层;在第一栅极和第二栅极之间形成第三沟槽;在缓冲层上形成第一金属层,第一金属层填充第三沟槽。

50.参考图4,其示出了形成缓冲层后的剖面示意图;参考图5,其示出了形成第三沟槽后的剖面示意图;参考图6,其示出了形成第一金属层后的剖面示意图。

51.示例性的,如图4至图6所示,可通过化学气相沉积(chemical vapor deposition,cvd)工艺在栅介质层220、第一栅极231和第二栅极232上沉积氧化层(例如,二氧化硅(sio2)层)或氮化层(例如,氮化硅(sin)层)形成缓冲层240;可通过光刻工艺在缓冲层240上覆盖光阻,暴露出第三沟槽303上方的区域,进行刻蚀,在第一栅极231和第二栅极232之间形成第三沟槽303,去除光阻;在缓冲层240上形成第一金属层251。

52.其中,第三沟槽303的底部高于第一掺杂区201的底部,第三沟槽303的底部低于第一重掺杂区202的底部;若第一金属层251包含铜(cu),可通过电镀铜层的方式形成第一金属层251,若第一金属层251包含钨(w),可通过cvd工艺沉积钨层的方式形成第一金属层251,若第一金属层251包含铝(al),可通过物理气相沉积(physical vapor deposition,pvd)工艺沉积铝层的方式形成第一金属层251。

53.步骤s4,对衬底的背面进行减薄处理。

54.参考图7,其示出了对衬底的背面进行减薄后的剖面示意图。示例性的,如图7所示,衬底210的厚度由h1降低为h2,h2<h1。

55.步骤s5,进行离子注入,在衬底的背面至第三深度形成第二掺杂区。

56.步骤s6,进行离子注入,在衬底的背面至第四深度形成第二重掺杂区,第四深度小于第三深度。

57.参考图8,其示出了形成第二掺杂区和第二重掺杂区后的剖面示意图。示例性的,如图8所示,衬底210的底部形成有第二掺杂区204和第二重掺杂区205,其中第二重掺杂区205的深度小于第二掺杂区204的深度。其中,第二掺杂区204可作为逆导型igbt器件的场截止(field stop,fs)区。

58.步骤s7,进行离子注入,在第二重掺杂区中形成第三重掺杂区和第四重掺杂区,第三重掺杂区和第四重掺杂区不接触。

59.步骤s8,在衬底的背面形成第二金属层。

60.参考图9,其示出了形成第三重掺杂区、第四重掺杂区和第二金属层后的剖面示意图。示例性的,如图9所示,可通过光刻工艺覆盖光阻,暴露出第三重掺杂区206和第四重掺杂区207上方的区域,进行离子注入,在第二重掺杂区205中形成第三重掺杂区206和第四重掺杂区207,进而去除光阻,在衬底210的背面形成第二金属层252。其中,第三重掺杂区206和第四重掺杂区207的深度和第二重掺杂区205的深度相同且与第二掺杂区204接触。第二掺杂区204和第一掺杂区201之间的区域即为器件的漂移区。

61.若第二金属层252包含铜,可通过电镀铜层的方式形成第二金属层252,若第二金属层252包含钨,可通过cvd工艺沉积钨层的方式形成第二金属层252,若第二金属层252包含铝,可通过pvd工艺沉积铝层的方式形成第二金属层252。

62.本技术实施例中,第一重掺杂区202、第二重掺杂区205、第三重掺杂区206和第四重掺杂区207的杂质浓度大于第一掺杂区201、柱形掺杂区203和第二掺杂区205的杂质浓度;第一掺杂区201、柱形掺杂区203、第二重掺杂区205掺杂有第一类型的杂质,第一重掺杂区202、第二掺杂区204、第三重掺杂区206和第四重掺杂区207掺杂有第二类型的杂质。

63.本技术实施例中,若第一类型的杂质为n(negative)型杂质,则第二类型的杂质为p(positive)型杂质;若第一类型的杂质为p型杂质,则第二类型的杂质为n型杂质。

64.综上所述,本技术实施例中,通过在逆导型igbt器件的第一栅极和第二栅极之间下方的台面区域形成柱形掺杂区,从而将漂移区电场转变为沿垂直方向的近均匀分布,提高了器件的击穿电压;同时,通过对衬底的背面进行减薄处理,降低了衬底的厚度和电阻率,进而提高了器件的电学性能。

65.参考图9,其示出了本技术一个示例性实施例提供的逆导型igbt器件的剖面示意图,该器件可通过上述实施例进行制作得到,如图9所示,该器件包括:

66.衬底210,其中形成有第一沟槽和第二沟槽,衬底210、第一沟槽和第二沟槽的表面形成有栅介质层220,第一沟槽中填充有第一栅极231,第二沟槽中填充有第二栅极232,衬底210的背面在制作完正面后经过了减薄处理。在一些实施例中,第一沟槽和第二沟槽的尺寸(深度和宽度)相同,其(第一沟槽或第二沟槽)深度和宽度的比值大于3。

67.衬底210的正面至第一深度形成有第一掺杂区201(其可作为igbt器件的阱区),衬底210的正面至第二深度形成有第一重掺杂区202(第二深度小于第一深度),衬底210的背面至第三深度形成有第二掺杂区204(其可作为igbt器件的场截止区),衬底210的背面至第四深度形成有第二重掺杂区205(第四深度小于第三深度),第二重掺杂区205中形成第三重掺杂区206和第四重掺杂区207,第三重掺杂区206和第四重掺杂区207不接触,且第三重掺杂区206、第四重掺杂区207和第二重掺杂区205的深度相同,衬底210的背面形成有第二金属层252,第三重掺杂区206和第四重掺杂区207的两端分别与第二掺杂区204和第二金属层

252接触。

68.第一栅极231和第二栅极232之间的衬底中形成有柱形掺杂区203,柱形掺杂区203的底部低于第一栅极231和第二栅极232的底部,柱形掺杂区203的顶部低于第一栅极231和第二栅极232的顶部,且柱形掺杂区203的底部低于第一掺杂区201的底部。在一些实施例中,柱形掺杂区203的高度和宽度的比值大于2。

69.栅介质层220、第一栅极231和第二栅极232上形成有缓冲层240;第一栅极231和第二栅极232之间形成有第三沟槽,第三沟槽的底部低于第一重掺杂区202的底部且高于第一掺杂区201的底部;缓冲层240上形成有第一金属层251,第一金属层251填充第三沟槽。第一金属层251和第二金属层252可包括铜、钨或铝;缓冲层240可以是氧化层或氮化层。

70.第一重掺杂区202、第二重掺杂区205、第三重掺杂区206和第四重掺杂区207的杂质浓度大于第一掺杂区201、柱形掺杂区203和第二掺杂区205的杂质浓度;第一掺杂区201、柱形掺杂区203、第二重掺杂区205掺杂有第一类型的杂质,第一重掺杂区202、第二掺杂区204、第三重掺杂区206和第四重掺杂区207掺杂有第二类型的杂质。

71.显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本技术创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1