具有本征氢化非晶硅层的量产线异质结电池的制作方法

1.本发明涉及异质结电池,特别是涉及具有本征氢化非晶硅层的异质结电池。

背景技术:

2.晶硅异质结太阳能电池(hjt)因其具有高转换效率、低温度系数、无光致衰减和电致衰减,且具有工艺步骤简单、制程温度低的诸多优势,引起了国内光伏行业人员极大的兴趣。但因其核心技术及专利都为国外所有,导致国内异质结电池技术进展缓慢。随着专利保护期结束、技术壁垒消除,异质结电池技术迎来了大力发展和推广的大好时机,国内开始掀起了研究和发展异质结电池技术的广泛潮流。

3.异质结电池的核心技术是通过在硅片表面处沉积一层高质量的本征非晶硅层,与硅片表面的悬挂键和缺陷结合,使形成的异质结界面悬挂键少、缺陷态密度低,从而获得良好的钝化效果。但本征非晶硅层相比于掺杂非晶硅层,薄膜的电导率比较低,本征非晶硅层较厚会导致异质结电池转换效率下降,目前异质结电池的最高效率为26.7%。

4.国内学者对本征非晶硅薄膜研究较多。有通过采用afors-het模拟软件对发射层、本征层、背场进行数值模拟与优化,理论计算表明双面异质结电池转换效率可以高达29.17%。还有研究氢注入对本征非晶硅薄膜的影响,发现适当的氢注入可以提高非晶硅薄膜的氢含量,降低了微结构因子,显著提高了异质结界面的钝化质量。也有研究了硼掺杂层厚度和硼掺杂比对电池开路电压的影响,发现voc随着p层厚度增加迅速增加,当厚度为25nm时开路电压趋于饱和,voc随着硼掺杂的增加而减小。但是,上述的大部分研究均使用的是实验设备,关于优化量产线本征非晶硅薄膜的厚度,提高异质结电池钝化性能和光电性能方面的研究较少。

技术实现要素:

5.发明目的:本发明的目的是提供一种具有本征氢化非晶硅层的异质结电池,针对量产线的应用进行技术优化,改善本征非晶硅薄膜层钝化效果差而导致的电池转换效率低的问题。

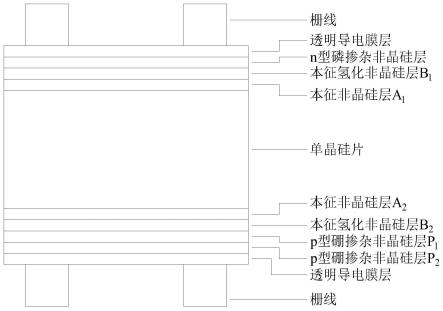

6.技术方案:一种具有本征氢化非晶硅层的量产线异质结电池,包括单晶硅片,单晶硅片的上表面上由内向外依次设有本征非晶硅层a1、n型磷掺杂非晶硅层、透明导电膜层、栅线,构成电池正面,单晶硅片的下表面上由内向外依次设有本征非晶硅层a2、p型硼掺杂非晶硅层、透明导电膜层、栅线,构成电池背面,本征非晶硅层a1与n型磷掺杂非晶硅层之间还设有本征氢化非晶硅层b1,本征非晶硅层a2与p型硼掺杂非晶硅层之间还设有本征氢化非晶硅层b2。

7.进一步的,本征氢化非晶硅层b1为使用硅烷和氢气沉积的本征氢化非晶硅薄膜,本征氢化非晶硅层b2为使用硅烷和氢气沉积的本征氢化非晶硅薄膜。

8.进一步的,本征非晶硅层a1为使用硅烷沉积的本征非晶硅薄膜,本征非晶硅层a2为使用硅烷沉积的本征非晶硅薄膜。

9.进一步的,n型磷掺杂非晶硅层为使用硅烷、氢气和2%磷烷/氢气混合气体沉积的磷掺杂非晶硅薄膜。

10.进一步的,p型硼掺杂非晶硅层包括两层结构,p型硼掺杂非晶硅层p1的内侧与本征氢化非晶硅层b2邻接,p型硼掺杂非晶硅层p2的内侧与p型硼掺杂非晶硅层p1的外侧邻接;p型硼掺杂非晶硅层p1为使用硅烷、氢气和2%硼烷/氢气混合气体沉积的低掺硼非晶硅薄膜,p型硼掺杂非晶硅层p2为使用硅烷、氢气和2%硼烷/氢气混合气体沉积的高掺硼非晶硅薄膜。

11.以上的具有本征氢化非晶硅层的量产线异质结电池,本征氢化非晶硅层b1的厚度为2~6nm,本征氢化非晶硅层b2的厚度为7~11nm。

12.以上的具有本征氢化非晶硅层的量产线异质结电池,本征非晶硅层a1的厚度为4nm,本征氢化非晶硅层b1的厚度为2~6nm,n型磷掺杂非晶硅层的厚度为4nm、掺杂浓度为4%,本征非晶硅层a2的厚度为4nm,本征氢化非晶硅层b2的厚度为7~11nm,p型硼掺杂非晶硅层p1的厚度为2nm、掺杂浓度为1%,p型硼掺杂非晶硅层p2的厚度为7nm、掺杂浓度为4%。

13.最佳的,本征非晶硅层a1的厚度为4nm,本征氢化非晶硅层b1的厚度为5nm,n型磷掺杂非晶硅层的厚度为4nm、掺杂浓度为4%,本征非晶硅层a2的厚度为4nm,本征氢化非晶硅层b2的厚度为9nm,p型硼掺杂非晶硅层p1的厚度为2nm、掺杂浓度为1%,p型硼掺杂非晶硅层p2的厚度为7nm、掺杂浓度为4%。

14.有益效果:本发明的优点是:以量产线异质结电池为基础,优化设计入光侧和背光侧本征氢化非晶硅层的膜厚及两者的匹配,提高异质结电池在钝化效果、透过率、电池转换效率上的性能。

附图说明

15.图1为本发明的异质结电池结构示意图;

16.图2为本征氢化非晶硅层b1的膜厚与透过率的变化曲线图;

17.图3为本征氢化非晶硅层b1的膜厚与少子寿命的变化曲线图;

18.图4为本征氢化非晶硅层b2的膜厚与透过率的变化曲线图;

19.图5为本征氢化非晶硅层b2的膜厚与少子寿命的变化曲线图;

20.图6为本征氢化非晶硅层b1和本征氢化非晶硅层b2不同膜厚匹配方案制作的9组异质结电池,电性能数据测试短路电流isc图;

21.图7为本征氢化非晶硅层b1和本征氢化非晶硅层b2不同膜厚匹配方案制作的9组异质结电池,电性能数据测试开路电压voc图;

22.图8为本征氢化非晶硅层b1和本征氢化非晶硅层b2不同膜厚匹配方案制作的9组异质结电池,电性能数据测试填充因子ff图;

23.图9为本征氢化非晶硅层b1和本征氢化非晶硅层b2不同膜厚匹配方案制作的9组异质结电池,电性能数据测试光电转换效率eta图。

具体实施方式

24.下面结合附图和具体实施例,进一步阐明本发明。

25.一种具有本征氢化非晶硅层的量产线异质结电池,其结构如附图1所示,包括单晶

硅片,单晶硅片的上表面上由内向外依次设有本征非晶硅层a1、本征氢化非晶硅层b1、n型磷掺杂非晶硅层、透明导电膜层、栅线,构成电池正面,电池正面为入光侧,单晶硅片的下表面上由内向外依次设有本征非晶硅层a2、本征氢化非晶硅层b2、p型硼掺杂非晶硅层p1、p型硼掺杂非晶硅层p2、透明导电膜层、栅线,构成电池背面,电池背面为背光侧。

26.本征非晶硅层a1为使用硅烷沉积的本征非晶硅薄膜,厚度为4nm。本征氢化非晶硅层b1为使用硅烷和氢气沉积的本征氢化非晶硅薄膜,厚度为2~6nm。n型磷掺杂非晶硅层为使用硅烷、氢气和2%磷烷/氢气混合气体沉积的磷掺杂非晶硅薄膜,厚度为4nm、掺杂浓度为4%。本征非晶硅层a2为使用硅烷沉积的本征非晶硅薄膜,厚度为4nm。本征氢化非晶硅层b2为使用硅烷和氢气沉积的本征氢化非晶硅薄膜,厚度为7~11nm。p型硼掺杂非晶硅层p1为使用硅烷、氢气和2%硼烷/氢气混合气体沉积的低掺硼非晶硅薄膜,厚度为2nm、掺杂浓度为1%。p型硼掺杂非晶硅层p2为使用硅烷、氢气和2%硼烷/氢气混合气体沉积的高掺硼非晶硅薄膜,厚度为7nm、掺杂浓度为4%。

27.本技术的异质结电池以n面为入光侧,p面为背光侧。n面为磷掺杂层,因磷掺杂会增加非晶硅的无序性,制备磷掺杂层不会破坏本征层的钝化性能,因此在满足钝化性能的前提下n面本征层可以做的薄一些;p面为硼掺杂层,因硼会使非晶硅由无序状态向纳米晶及微晶状态转变,即硼会使非晶硅晶化导致钝化效果下降,沉积硼掺杂层时硼会向本征层扩散导致本征层钝化效果下降,因此在满足钝化性能的前提下,p面本征层需要做的厚一些。这样把n面做为入光侧一面,n面非晶硅层厚度薄,光透过非晶硅层进入晶硅层的比例高,制得的异质结电池的光的有效吸收率高,光电转换效率高。

28.对于本技术的异质结电池,在本征非晶硅层a1、n型磷掺杂非晶硅层、本征非晶硅层a2、p型硼掺杂非晶硅层p1、p型硼掺杂非晶硅层p2保持不变的前提下,改变本征氢化非晶硅层b1、本征氢化非晶硅层b2的沉积时间,分析比较制得的厚度2~6nm的本征氢化非晶硅层b1、厚度7~11nm的本征氢化非晶硅层b2,对异质结电池钝化性能和光电性能的影响。

29.1、量产实验

30.选用同一批次的金刚线切割的n型单晶硅片,尺寸为166

×

166mm,厚度为150~155μm,电阻率为2.5~3.5ω

·

cm,少子寿命为8000~10000μs;普通载玻片。

31.本征氢化非晶硅薄膜沉积速率计算:以上述的普通载玻片作为基体,设置沉积时间t为200s,温度为200℃,功率为330w,极板间距为21mm,压力为190pa,sih4流量为0.35l/min,h2流量为7.5l/min。沉积结束后采用美国j.a.woollam m-2000椭偏仪测试普通载玻片上沉积的本征氢化非晶硅薄膜厚度d。

[0032][0033]

膜厚d测试结果为12.5nm,通过公式(1)计算得出在上述沉积条件下沉积速率v=12.5nm/200s=0.0625nm/s。

[0034]

以下每种实验样的数量为10000片。

[0035]

实验1.1:本征氢化非晶硅层b1膜厚实验。

[0036]

通过改变本征氢化非晶硅层b1的沉积时间,设置沉积时间分别为32s、48s、64s、80s、96s,以制绒后的硅片和普通载玻片为基体,制备出5组厚度分别为2nm、3nm、4nm、5nm、6nm的本征氢化非晶硅薄膜,本征非晶硅层a1、n型磷掺杂非晶硅层、本征非晶硅层a2、本征氢化非晶硅层b2、p型硼掺杂非晶硅层p1、p型硼掺杂非晶硅层p2保持相同,其中,本征氢化非晶

硅层b2厚度为12nm以确保p面钝化效果,具体实验方案如表1所示,普通载玻片上只沉积本征非晶硅层a1、本征氢化非晶硅层b1、n型磷掺杂非晶硅层。实验结束测试普通载玻片上非晶硅薄膜的膜厚和透过率,硅片的少子寿命。

[0037]

表1

[0038][0039][0040]

实验1.2:本征氢化非晶硅层b2膜厚实验。

[0041]

通过改变本征氢化非晶硅层b2的沉积时间,设置沉积时间分别为112s、128s、144s、160s、176s,以制绒后的硅片和普通载玻片为基体,制备出5组厚度分别为7nm、8nm、9nm、10nm、11nm的本征氢化非晶硅薄膜,本征非晶硅层a1、本征氢化非晶硅层b1、n型磷掺杂非晶硅层、本征非晶硅层a2、p型硼掺杂非晶硅层p1、p型硼掺杂非晶硅层p2保持相同,其中,本征氢化非晶硅层b1厚度为7nm以确保n面钝化效果,具体实验方案如表2所示,普通载玻片上只沉积本征非晶硅层a2、本征氢化非晶硅层b2。实验结束测试普通载玻片上非晶硅薄膜的膜厚和透过率,硅片的少子寿命。

[0042]

表2

[0043][0044]

实验1.3:本征氢化非晶硅层b1膜厚与本征氢化非晶硅层b2膜厚匹配实验。

[0045]

通过改变本征氢化非晶硅层b1的沉积时间,设置沉积时间分别为64s、80s、96s,设计膜厚分别为4nm、5nm、6nm三种方案,通过改变本征氢化非晶硅层b2的沉积时间,设置沉积时间分别为144s、160s、176s,设计膜厚分别为9nm、10nm、11nm三种方案,本征氢化非晶硅层b1的三种膜厚方案和本征氢化非晶硅层b2的三种膜厚方案,进行正交实验,共得到9组膜厚

匹配方案,具体膜厚匹配方案如表3所示,本征非晶硅层a1、n型磷掺杂非晶硅层、本征非晶硅层a2、p型硼掺杂非晶硅层p1、p型硼掺杂非晶硅层p2保持相同。据此制作9组异质结电池,并进行电性能数据测试。

[0046]

表3

[0047][0048][0049]

2、实验分析和结果

[0050]

采用美国j.a.woollam m-2000椭偏仪测试非晶硅薄膜厚度;采用hitachi公司的uh4150太阳能紫外光谱仪测试透过率数据;采用sinton公司的wct-120少子寿命测试仪检测硅片的少子寿命;采用halm电学性能测试仪测试异质结电池的光电转换效率eta、填充因子ff、开路电压voc、短路电流isc、串联电阻rs和并联电阻rsh等电性能数据。

[0051]

2.1本征氢化非晶硅层b1膜厚与透过率的变化曲线如附图2所示,其中的n面非晶硅层为本征非晶硅层a1、本征氢化非晶硅层b1、n型磷掺杂非晶硅层的总厚度。由附图2可见,随着本征氢化非晶硅层b1厚度增加,n面非晶硅层透过率逐渐降低,这是因为非晶硅的带隙宽度在1.7ev左右,光子能量大于1.7ev的紫外光和可见光可能会被吸收,非晶硅层越厚,被吸收的光越多,透过非晶硅层的光子数量就会减少。

[0052]

2.2本征氢化非晶硅层b1膜厚与少子寿命的变化曲线如附图3所示。由附图3可见,随着本征氢化非晶硅层b1厚度增加,测试硅片的少子寿命逐渐增加,当n面非晶硅层厚度达到13.1nm时,少子寿命达到3684μs趋于稳定,这是因为随着本征氢化非晶硅层b1厚度的增加使得界面钝化更加充分,且在后续的退火过程中提供更多的氢,扩散到本征非晶硅层a1薄膜中,有效地钝化了非晶硅中和单晶硅表面的悬挂键,改善了非晶硅/硅片的界面质量。

[0053]

2.3本征氢化非晶硅层b2膜厚与透过率的变化曲线如附图4所示,其中的p面本征非晶硅层为本征非晶硅层a2、本征氢化非晶硅层b2的总厚度。由附图4可见,随着本征氢化非晶硅层b2厚度增加,p面本征非晶硅层透过率逐渐下降,这是因为随着非晶硅层变厚,被吸收的光越多,透过非晶硅层的光子数量就会减少。

[0054]

2.4本征氢化非晶硅层b2膜厚与少子寿命的变化曲线如附图5所示。由附图5可见,随着本征氢化非晶硅层b2厚度增加,测试硅片的少子寿命先快速增加然后趋于稳定。这是因为当本征层较薄时,随着膜厚增加,钝化效果快速增强,随着膜厚变厚,钝化效果趋于饱和。

[0055]

2.5本征氢化非晶硅层b1和本征氢化非晶硅层b2不同膜厚匹配方案制作的9组异质结电池,进行的电性能数据测试如附图6~附图9所示。

[0056]

isc的大小是异质结电池光有效吸收率的直观体现。由附图6可见:膜厚匹配方案1的isc最高,达到10.5786a,膜厚匹配方案9的isc最低,为10.5080a,分析为n面的本征氢化非晶硅层b1厚度薄,光的透过率高,电池的有效光吸收率高,其isc就高,但isc也受到p面的本征氢化非晶硅层b2厚度影响,本征非晶硅层电阻率较高,当本征氢化非晶硅层b2厚度为9nm时,其isc为最高,p面的本征氢化非晶硅层b2高于9nm,载流子的输运难度增加,串联电阻增大,isc降低。

[0057]

voc的大小受电池形成的内建电场强度和复合速率影响,在硼掺杂层和磷掺杂层的掺杂浓度和厚度不变情况下,影响voc的大小取决于钝化层的钝化效果。在一定厚度范围内,n面作为电子传输层,本征氢化非晶硅层b1厚度越厚,钝化效果越好,p面作为空穴传输层,本征氢化非晶硅层b2厚度越厚,钝化效果越好。由附图7可见:本征氢化非晶硅层b1厚度低于5nm,则voc急剧下降,表明本征氢化非晶硅层b1没有对晶硅表面全覆盖,存在一定的缺陷复合,只有高于5nm才能达到表面全覆盖,钝化基本达到饱和。另外,本征氢化非晶硅层b2厚度达到9nm已基本达到钝化要求,增加厚度可进一步提高钝化效果但增加幅度不大。

[0058]

ff的大小受电池材料的接触性能影响较大,异质结界面处的复合对其也会产生一定影响。由附图8可见:ff受本征氢化非晶硅层b2厚度影响极大,无论本征氢化非晶硅层b1薄还是厚,p面的本征非晶硅层厚度增加,ff急剧下降,这是由于本征非晶硅层电阻率较高,厚度增加导致串联电阻增大带来的,因此,本征氢化非晶硅层b2厚度高于9nm,对电池的串联电阻产生一定影响,当厚度在9~11nm范围内,填充逐渐下降。本征氢化非晶硅层b1厚度为5nm最合适,厚度为4nm以下则表面钝化不足,仍然存在一定的缺陷复合使ff低,厚度为6nm以上则载流子的输运难度大,串联电阻增大则ff也降低。

[0059]

eta的大小受电池的isc、voc、ff综合影响。由附图9可见:膜厚匹配方案4的eta最高,这是因为本征氢化非晶硅层b1膜厚在5nm左右钝化效果较好,且透过率处于中间水平保证了较好的isc,本征氢化非晶硅层b2膜厚在9nm左右时钝化效果较好,复合较低,且p面本征非晶硅层最薄电阻率最低,载流子的输运难度最低,综合效率最高,制作的异质结电池isc为10.5667a,voc为0.7512v,ff为84.92%,eta为24.59%。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1