多路同频合路器的制作方法

1.本技术涉及移动通信技术领域,特别是涉及一种多路同频合路器。

背景技术:

2.移动通信覆盖工程在进行共建共享时,通常需要使用合路器将输入的多频段信号组合在一起后进行输出,以共用天线和馈线系统。传统技术中的合路器的功率容量较低。

技术实现要素:

3.基于此,有必要针对上述技术问题,提供一种能够提高功率容量的多路同频合路器。

4.本技术提供了一种多路同频合路器,包括:

5.两个第一合路模块,每一所述第一合路模块用于将输入信号进行合路,得到第一合路信号,并将所述第一合路信号从第一输出端口输出;其中,所述第一合路模块包括至少一个gysel合路单元;

6.一个第二合路模块,所述第二合路模块分别连接两个所述第一合路模块,所述第二合路模块用于对两个所述第一合路信号进行合路,得到第二合路信号并将所述第二合路信号从第二输出端口输出。

7.在其中一个实施例中,所述第一合路模块包括:两个第一gysel合路单元和一个第二gysel合路单元,每一所述第一gysel合路单元用于对输入信号进行合路,得到中间信号,所述第二gysel合路单元分别连接两个所述第一gysel合路单元,并对两个所述中间信号进行合路,得到所述第一合路信号。

8.在其中一个实施例中,所述第一gysel合路单元包括:第一线路、第二线路、第三线路、第四线路和第五线路,所述第一线路、第二线路、第三线路、第四线路和第五线路依次首尾连接并形成闭合的回路;

9.所述第一线路的一端用于接收所述输入信号,所述第二线路的一端用于接收所述输入信号,所述第一线路和所述第二线路的连接处用于输出所述中间信号,所述第四线路和所述第五线路的连接处用于连接第一负载,所述第三线路和所述第四线路的连接处用于连接第二负载;

10.所述第一线路、所述第二线路、所述第三线路和所述第五线路的电长度相等,且均为所述输入信号波长的1/4,所述第四线路的电长度为所述输入信号波长的1/2。

11.在其中一个实施例中,所述第一gysel合路单元还包括:第六线路、第七线路和第八线路,所述第六线路的一端连接所述第五线路,所述第六线路的另一端连接所述第七线路的一端和所述第一负载,所述第八线路的一端连接所述第三线路,所述第八线路的另一端连接所述第七线路的另一端和所述第二负载;

12.所述第六线路和所述第八线路的电长度相等,且均为所述输入信号波长的1/4,所述第七线路的电长度为所述输入信号波长的1/2。

13.在其中一个实施例中,所述第三线路的阻抗、所述第五线路的阻抗、所述第六线路的阻抗和所述第八线路的阻抗相等且均为输入信号阻抗,所述第一线路和所述第二线路的总阻抗为倍的输入信号阻抗。

14.在其中一个实施例中,所述第二gysel合路单元包括:第九线路、第十线路、第十一线路、第十二线路和第十三线路,所述第九线路、第十线路、第十一线路、第十二线路和第十三线路依次首尾连接并形成闭合的回路;

15.所述第九线路的一端用于接收所述中间信号,所述第十线路的一端用于接收所述中间信号,所述第九线路和所述第十线路的连接处用于输出所述第一合路信号,所述第十二线路和所述第十三线路的连接处用于连接第三负载,所述第十一线路和所述第十二线路的连接处用于连接第四负载;

16.所述第九线路、所述第十线路、所述第十一线路和所述第十三线路的电长度相等,且均为所述输入信号波长的1/4,所述第十二线路的电长度为所述输入信号波长的1/2。

17.在其中一个实施例中,所述第二gysel合路单元还包括:第十四线路、第十五线路和第十六线路,所述第十四线路的一端连接所述第十三线路,所述第十四线路的另一端连接所述第十五线路的一端和所述第三负载,所述第十六线路的一端连接所述第十一线路,所述第十六线路的另一端连接所述第十五线路的另一端和所述第四负载;

18.所述第十四线路和所述第十六线路的电长度相等,且均为所述输入信号波长的1/4,所述第十五线路的电长度为所述输入信号波长的1/2。

19.在其中一个实施例中,所述第十一线路的阻抗、所述第十三线路的阻抗、所述第十四线路的阻抗和所述第十六线路的阻抗相等且均为输入信号阻抗,所述第九线路和所述第十线路的总阻抗为倍的输入信号阻抗。

20.在其中一个实施例中,所述第二合路模块包括:两个信号耦合单元和一个第三gysel合路单元,每一所述信号耦合单元用于对所述第一合路信号进行耦合,得到耦合信号,所述第三gysel合路单元用于对两个所述耦合信号进行合路,得到所述第二合路信号。

21.在其中一个实施例中,所述第三gysel合路单元包括:第十七线路、第十八线路、第十九线路、第二十线路和第二十一线路,所述第十七线路、第十八线路、第十九线路、第二十线路和第二十一线路依次首尾连接并形成闭合的回路;

22.所述第十七线路的一端用于接收所述耦合信号,所述第十八线路的一端用于接收所述耦合信号,所述第十七线路和所述第十八线路的连接处用于输出所述第二合路信号,所述第二十线路和所述第二十一线路的连接处用于连接第五负载,所述第十九线路和所述第二十线路的连接处用于连接第六负载;

23.所述第十七线路、所述第十八线路、所述第十九线路和所述第二十一线路的电长度相等,且均为所述输入信号波长的1/4,所述第二十线路的电长度为所述输入信号波长的1/2。

24.在其中一个实施例中,所述第三gysel合路单元还包括:第二十二线路、第二十三线路和第二十四线路,所述第二十二线路的一端连接所述第二十一线路,所述第二十二线路的另一端连接所述第二十三线路的一端和所述第五负载,所述第二十四线路的一端连接所述第十九线路,所述第二十四线路的另一端连接所述第二十三线路的另一端和所述第六

负载;

25.所述第二十二线路和所述第二十四线路的电长度相等,且均为所述输入信号波长的1/4,所述第二十三线路的电长度为所述输入信号波长的1/2。

26.在其中一个实施例中,所述第十九线路的阻抗、所述第二十一线路的阻抗、所述第二十二线路的阻抗和所述第二十四线路的阻抗相等且均为输入信号阻抗,所述第十七线路和所述第十八线路的总阻抗为倍的输入信号阻抗。

27.上述多路同频合路器,通过在第一合路模块中设置至少一个gysel合路单元,可以将输入的多路输入信号合成为一路,得到第一合路信号,并从第一输出端口输出。再通过设置第二合路模块,将两路第一合路信号合路为第二合路信号,并从第二输出端口输出。从而可以使输入的多路输入信号,合成为三路信号进行输出。通过在第一合路模块中设置级联结构,可以提高合路器的相对带宽,且gysel合路单元通过自身的两个负载,可以提高合路器的功率容量。

附图说明

28.为了更清楚地说明本技术实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

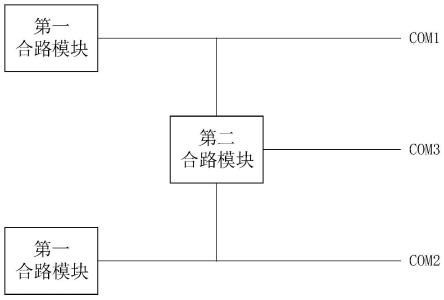

29.图1为一个实施例中多路同频合路器的模块示意图;

30.图2为另一个实施例中多路同频合路器的模块示意图;

31.图3为一个实施例中多路同频合路器的印制板电路图;

32.图4为又一个实施例中多路同频合路器的模块示意图;

33.图5为一个实施例中回波损耗仿真示意图;

34.图6为一个实施例中隔离度仿真示意图;

35.图7为一个实施例中耦合度仿真示意图;

36.图8为一个实施例中相位差仿真示意图;

37.图9为一个实施例中插损仿真示意图。

具体实施方式

38.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使本技术的公开内容更加透彻全面。

39.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

40.可以理解,本技术所使用的术语“第一”、“第二”等可在本文中用于描述各种元件,但这些元件不受这些术语限制。这些术语仅用于将第一个元件与另一个元件区分。

41.需要说明的是,当一个元件被认为是“连接”另一个元件时,它可以是直接连接到另一个元件,或者通过居中元件连接另一个元件。此外,以下实施例中的“连接”,如果被连

接的对象之间具有电信号或数据的传递,则应理解为“电连接”、“通信连接”等。

42.在此使用时,单数形式的“一”、“一个”和“所述/该”也可以包括复数形式,除非上下文清楚指出另外的方式。还应当理解的是,术语“包括/包含”或“具有”等指定所陈述的特征、整体、步骤、操作、组件、部分或它们的组合的存在,但是不排除存在或添加一个或更多个其他特征、整体、步骤、操作、组件、部分或它们的组合的可能性。同时,在本说明书中使用的术语“和/或”包括相关所列项目的任何及所有组合。

43.在一个实施例中,如图1所示,提供了一种多路同频合路器,包括:两个第一合路模块,每一第一合路模块用于将输入信号进行合路,得到第一合路信号,并将第一合路信号从第一输出端口输出;其中,第一合路模块包括至少一个gysel合路单元;一个第二合路模块,第二合路模块分别连接两个第一合路模块,第二合路模块用于对两个第一合路信号进行合路,得到第二合路信号并将第二合路信号从第二输出端口输出。

44.具体的,本技术实施例的第一合路模块为包括至少一个gysel合路单元的合路模块,其中,gysel合路单元为采用gysel同相合成网络制成的两路合成器,其可以将两路输入信号合成为一路信号,且在所有输入功率正常和在理想工作条件下,可以将全部功率加到输出端。第一合路模块可以通过设置多个gysel合路单元来构成级联结构,从而对多路输入信号进行合路。例如,可以仅设置一个gysel合路单元来将两路输入信号进行合路,或者通过设置三个gysel合路单元来将四路输入信号进行合路,还可以通过设置七个gysel合路单元来将八路输入信号进行合路。从而使第一合路模块可以为2合1同频合路器、4合1同频合路器或8合1同频合路器等。可以理解的是,gysel合路单元可以和其他网络结构的2合1合路单元进行级联,从而组成第一合路模块。

45.第二合路模块用于将耦合的两路第一合路信号进行合路,得到第二合路信号,第二合路模块为2合1合路单元。图1中的com1和com2为第一输出端口,用于输出经过合路的第一合路信号,com3为第二输出端口,用于输出经过合路的第二合路信号。可以理解的是,第一合路模块和第二合路模块的信号输入端口中输入的信号为同步信号。

46.上述多路同频合路器,通过在第一合路模块中设置至少一个gysel合路单元,可以将输入的多路输入信号合成为一路,得到第一合路信号,并从第一输出端口输出。再通过设置第二合路模块,将两路第一合路信号合路为第二合路信号,并从第二输出端口输出。从而可以使输入的多路输入信号,合成为三路信号进行输出。通过在第一合路模块中设置级联结构,可以提高合路器的相对带宽,且gysel合路单元通过自身设置的两个负载,可以提高合路器的功率容量。

47.在一个实施例中,如图2所示,第一合路模块包括:两个第一gysel合路单元和一个第二gysel合路单元,每一第一gysel合路单元用于对输入信号进行合路,得到中间信号,第二gysel合路单元分别连接两个第一gysel合路单元,并对两个中间信号进行合路,得到第一合路信号。

48.具体的,本技术实施例的第一合路模块通过设置三个gysel合路单元组成级联结构,使第一合路模块可以将四路输入信号合路为第一合路信号,第一合路模块即为4合1同频合路器。图2中的in1至in8均为信号输入端口,用于接收输入信号。通过本技术实施例的多路同频合路器,可以使输入的八路输入信号,合成为三路信号进行输出。第一合路模块通过设置的三个gysel合路单元,提高了合路器的相对带宽和功率容量,在通过天线进行信号

发射时,可以使信号覆盖范围更广。

49.在一个实施例中,如图3所示,第一gysel合路单元包括:第一线路、第二线路、第三线路、第四线路和第五线路,第一线路、第二线路、第三线路、第四线路和第五线路依次首尾连接并形成闭合的回路;第一线路的一端用于接收输入信号,第二线路的一端用于接收输入信号,第一线路和第二线路的连接处用于输出中间信号,第四线路和第五线路的连接处用于连接第一负载,第三线路和第四线路的连接处用于连接第二负载;第一线路、第二线路、第三线路和第五线路的电长度相等,且均为输入信号波长的1/4,第四线路的电长度为输入信号波长的1/2。

50.具体的,本技术实施例的第一线路为ab段,第二线路为bc段,第三线路为cd段,第四线路为de段,第五线路为ae段,通过首尾相接形成闭合的“口”字型结构。第一线路的端口a和第二线路的端口c用于接收输入信号,端口b用于输出中间信号,节点e和节点d用于分别连接第一负载和第二负载。可以理解的是,在本实施例中,第一gysel合路单元为“口”字型结构,节点e和节点d直接与第一负载和第二负载连接。在第一gysel合路单元为“日”字型等结构时,节点e和节点d则是间接与第一负载和第二负载连接。第一gysel合路单元可以为微带线形式或空气带状线等形式制成。

51.在一个实施例中,如图3所示,第一gysel合路单元还包括:第六线路、第七线路和第八线路,第六线路的一端连接第五线路,第六线路的另一端连接第七线路的一端和第一负载,第八线路的一端连接第三线路,第八线路的另一端连接第七线路的另一端和第二负载;第六线路和第八线路的电长度相等,且均为输入信号波长的1/4,第七线路的电长度为输入信号波长的1/2。

52.具体的,本技术实施例的第六线路为ef段、第七线路为fg段、第八线路为dg段,节点f和节点g直接分别连接第一负载和第二负载。在本实施例中,第一gysel合路单元为“日”字型结构,在一些其他实施例中,第一gysel合路单元还可以设置为“目”字型结构等类似结构。

53.在一个实施例中,第三线路的阻抗、第五线路的阻抗、第六线路的阻抗和第八线路的阻抗相等且均为输入信号阻抗,第一线路和第二线路的总阻抗为倍的输入信号阻抗。具体示例,在一些实施例中,输入信号阻抗为50ω,zcd=zae=zef=zdg=50ω,zab=zbc=70.7ω,第四线路的阻抗zde和第七线路的阻抗zfg则可以根据所要求的隔离度和带宽灵活调整。

54.具体的,下面对第一gysel合路单元的工作原理进行说明。其中,电长度ab=bc=cd=ae=ef=dg=λ/4,ac=de=fg=λ/2,对应的相位偏移θab=θbc=θcd=θae=90

°

,θac=180

°

。设port1和port2的阻抗分别为zp=zo,则zae=zcd=zef=zdg=zo,zde和zfg则可根据所需带宽灵活调整。当port1输入信号,其他端口匹配时,port1到port3有两条路径ab和aedcb,此时θab=90

°

,θaedcb=90

°

+180

°

+90

°

+90

°–

360

°

=90

°

,相位差为0,信号在port3叠加。port1到port2的路径为abc和aedc,θabc=90

°

+90

°

=180

°

,θaedc=90

°

+180

°

+90

°

=360

°

,相位差为180

°

,信号在port2抵消。通过上述分析,当port1输入信号,其他端口匹配时,此时第一gysel合路单元具有一定的分支线定向耦合器特性,有3db功率通过port3输出,有3db功率被第一负载和第二负载吸收,且两负载吸收的功率相同,即两

负载分别吸收了6db的功率。同理可得,当port2输入信号,其他端口匹配时,则有3db功率通过port3输出,有3db功率被第一负载和第二负载吸收。当port1和port2输入同步信号时,通过以上方法分析可知,信号全部从port3输出,第一负载和第二负载不吸收功率。因此,在正常的工作状态下,通过信号的相互叠加和抵消,port1和port2为隔离口,中间信号可以无损耗地输出,提高信号的功率。

55.在一个实施例中,第二gysel合路单元包括:第九线路、第十线路、第十一线路、第十二线路和第十三线路,第九线路、第十线路、第十一线路、第十二线路和第十三线路依次首尾连接并形成闭合的回路;第九线路的一端用于接收中间信号,第十线路的一端用于接收中间信号,第九线路和第十线路的连接处用于输出第一合路信号,第十二线路和第十三线路的连接处用于连接第三负载,第十一线路和第十二线路的连接处用于连接第四负载;第九线路、第十线路、第十一线路和第十三线路的电长度相等,且均为输入信号波长的1/4,第十二线路的电长度为输入信号波长的1/2。

56.具体的,本技术实施例的第九线路为hi段,第十线路为ij段,第十一线路为jk段,第十二线路为kl段,第十三线路为hl段,通过首尾相接形成闭合的“口”字型结构。第九线路的端口h和第十线路的端口j用于接收中间信号,端口i用于输出第一合路信号,节点l和节点k用于分别连接第三负载和第四负载。可以理解的是,在本实施例中,第二gysel合路单元为“口”字型结构,节点l和节点k直接与第三负载和第四负载连接。在第二gysel合路单元为“日”字型等结构时,节点l和节点k则是间接与第三负载和第四负载连接。第二gysel合路单元可以为微带线形式或空气带状线等形式制成。

57.在一个实施例中,第二gysel合路单元还包括:第十四线路、第十五线路和第十六线路,第十四线路的一端连接第十三线路,第十四线路的另一端连接第十五线路的一端和第三负载,第十六线路的一端连接第十一线路,第十六线路的另一端连接第十五线路的另一端和第四负载;第十四线路和第十六线路的电长度相等,且均为输入信号波长的1/4,第十五线路的电长度为输入信号波长的1/2。

58.具体的,本技术实施例的第十四线路为lm段、第十五线路为mn段、第十六线路为kn段,节点m和节点n直接分别连接第三负载和第四负载。在本实施例中,第二gysel合路单元为“日”字型结构,在一些其他实施例中,第二gysel合路单元还可以设置为“目”字型结构等类似结构。

59.在一个实施例中,第十一线路的阻抗、第十三线路的阻抗、第十四线路的阻抗和第十六线路的阻抗相等且均为输入信号阻抗,第九线路和第十线路的总阻抗为倍的输入信号阻抗。具体示例,在一些实施例中,输入信号阻抗为50ω,zjk=zhl=zlm=zkn=50ω,zhi=zij=70.7ω,第十二线路的阻抗zkl和第十五线路的阻抗zmn则可以根据所要求的隔离度和带宽灵活调整。

60.具体的,本技术实施例的第二gysel合路单元的结构设置和工作原理与第一gysel合路单元相同,此处不再一一赘述。可以理解的是,两个第一gysel合路单元输出的两个中间信号为同步信号,第三负载和第四负载不吸收功率,第二gysel合路单元在正常的工作状态下,通过信号的相互叠加和抵消,第一合路信号可以无损耗的输出,提高了第一合路信号的功率。

61.在一个实施例中,第二合路模块包括:两个信号耦合单元和一个第三gysel合路单

元,每一信号耦合单元用于对第一合路信号进行耦合,得到耦合信号,第三gysel合路单元用于对两个耦合信号进行合路,得到第二合路信号。

62.具体的,本技术实施例通过两个信号耦合单元,分别从信号主干通道中提取一部分信号,即对第一合路信号进行提取,得到对应的耦合信号。例如,如图3所示,信号耦合单元为耦合微带线,耦合微带线由两条平行放置、彼此靠近的微带线构成,可以将第一合路信号进行耦合,得到对应的耦合信号。

63.在一个实施例中,第三gysel合路单元包括:第十七线路、第十八线路、第十九线路、第二十线路和第二十一线路,第十七线路、第十八线路、第十九线路、第二十线路和第二十一线路依次首尾连接并形成闭合的回路;第十七线路的一端用于接收耦合信号,第十八线路的一端用于接收耦合信号,第十七线路和第十八线路的连接处用于输出第二合路信号,第二十线路和第二十一线路的连接处用于连接第五负载,第十九线路和第二十线路的连接处用于连接第六负载;第十七线路、第十八线路、第十九线路和第二十一线路的电长度相等,且均为输入信号波长的1/4,第二十线路的电长度为输入信号波长的1/2。

64.具体的,本技术实施例的第十七线路为op段,第十八线路为pq段,第十九线路为qr段,第二十线路为rs段,第二十一线路为os段,通过首尾相接形成闭合的“口”字型结构。第十七线路的端口o和第十八线路的端口q用于接收耦合信号,端口p用于输出第二合路信号,节点s和节点r用于分别连接第五负载和第六负载。可以理解的是,在本实施例中,第三gysel合路单元为“口”字型结构,节点s和节点r直接与第五负载和第六负载连接。在第三gysel合路单元为“日”字型等结构时,节点s和节点r则是间接与第五负载和第六负载连接。第三gysel合路单元可以为微带线形式或空气带状线等形式制成。

65.在一个实施例中,第三gysel合路单元还包括:第二十二线路、第二十三线路和第二十四线路,第二十二线路的一端连接第二十一线路,第二十二线路的另一端连接第二十三线路的一端和第五负载,第二十四线路的一端连接第十九线路,第二十四线路的另一端连接第二十三线路的另一端和第六负载;第二十二线路和第二十四线路的电长度相等,且均为输入信号波长的1/4,第二十三线路的电长度为输入信号波长的1/2。

66.具体的,本技术实施例的第二十二线路为st段、第二十三线路为tu段、第二十四线路为ru段,节点t和节点u直接分别连接第五负载和第六负载。在本实施例中,第三gysel合路单元为“日”字型结构,在一些其他实施例中,第三gysel合路单元还可以设置为“目”字型结构等类似结构。

67.在一个实施例中,第十九线路的阻抗、第二十一线路的阻抗、第二十二线路的阻抗和第二十四线路的阻抗相等且均为输入信号阻抗,第十七线路和第十八线路的总阻抗为倍的输入信号阻抗。具体示例,在一些实施例中,输入信号阻抗为50ω,zqr=zos=zst=zru=50ω,zop=zpq=70.7ω,第二十线路的阻抗zrs和第二十三线路的阻抗ztu则可以根据所要求的隔离度和带宽灵活调整。

68.具体的,本技术实施例的第三gysel合路单元的结构设置和工作原理与第一gysel合路单元相同,此处不再一一赘述。可以理解的是,两个第二gysel合路单元输出的两个第一合路信号为同步信号,对应得到的两个耦合信号也为同步信号,第五负载和第六负载不吸收功率,第三gysel合路单元在正常的工作状态下,通过信号的相互叠加和抵消,第二合路信号可以无损耗的输出,提高了第二合路信号的功率。且在将合路单元全部设置为gysel

合路单元的情况下,本技术实施例的多路同频合路器为对称结构,因此相位差也较小。

69.下面以一个具体实施例,详细描述本技术实施例的多路同频合路器。多路同频合路器的结构设置如图3所示,由七个结构相同的gysel网络和两个信号耦合单元组成,且均设置为微带线形式,印制板的厚度为1.5毫米,介电常数为2.65。通过此设置得到的多路同频合路器的技术规格为:通带:2200-3000mhz,插入损耗:≤6.5db,隔离度≥24db,输出口耦合度:26

±

0.5db,相位差≤1

°

,回波损耗≥21db。

70.其中,图5为回波损耗仿真示意图,在2200至3000mhz范围内的回波损耗大于等于21db,说明端口的匹配程度好;图6为隔离度仿真示意图,在2200至3000mhz范围内的隔离度大于等于24db,说明信号输入端口之间的相互影响较小;图7为耦合度的仿真示意图,在2200至3000mhz范围内,耦合度为26

±

0.5db,说明耦合度的波动较小;图8为相位差仿真示意图,在2200至3000mhz范围内的相位差均小于1

°

,说明各个输入端口的相位差较小;图9为插损仿真示意图,在2200至3000mhz范围内的插损均小于等于6.5db,说明元件插入对功率的损耗较小。与现有的使用环形电桥制作的同频合路器相比,本技术实施例的多路同频合路器的相对带宽从6.1%提高到了30.7%,功率容量提升了2倍,相位差从≤5

°

降低到了≤1

°

,从而实现了通带宽,功率容量高,幅相一致性好的八进三出同频合路器结构。

71.在本说明书的描述中,参考术语“一些实施例”、“其他实施例”、“具体实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特征包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性描述不一定指的是相同的实施例或示例。

72.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

73.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1