一种封装基板及电子封装的制作方法

本申请涉及集成电路,尤其涉及一种封装基板及电子封装。

背景技术:

1、目前,随着中央处理器(cpu)、图像处理器(gpu)等高端高性能芯片核数持续增加,导致芯片越来越大,导致良率逐渐降低;为提高芯片良率,目前业界针对高端高性能芯片,已普遍转向小芯片(chip let),降低单个芯片面积。转向小芯片后,小芯片晶粒(die)间需要高带宽互联进行通讯,为此需要先进封装进行高密度互联满足这一需求。

2、高密度互联的基板对电源质量要求较高,这样,需要在基板外设置去耦电容,而在基板外设置去耦电容距离电源较远,去耦效果差,导致电源质量较差。

技术实现思路

1、有鉴于此,本申请实施例提供一种封装基板及电子封装,能够有效提高电源质量。

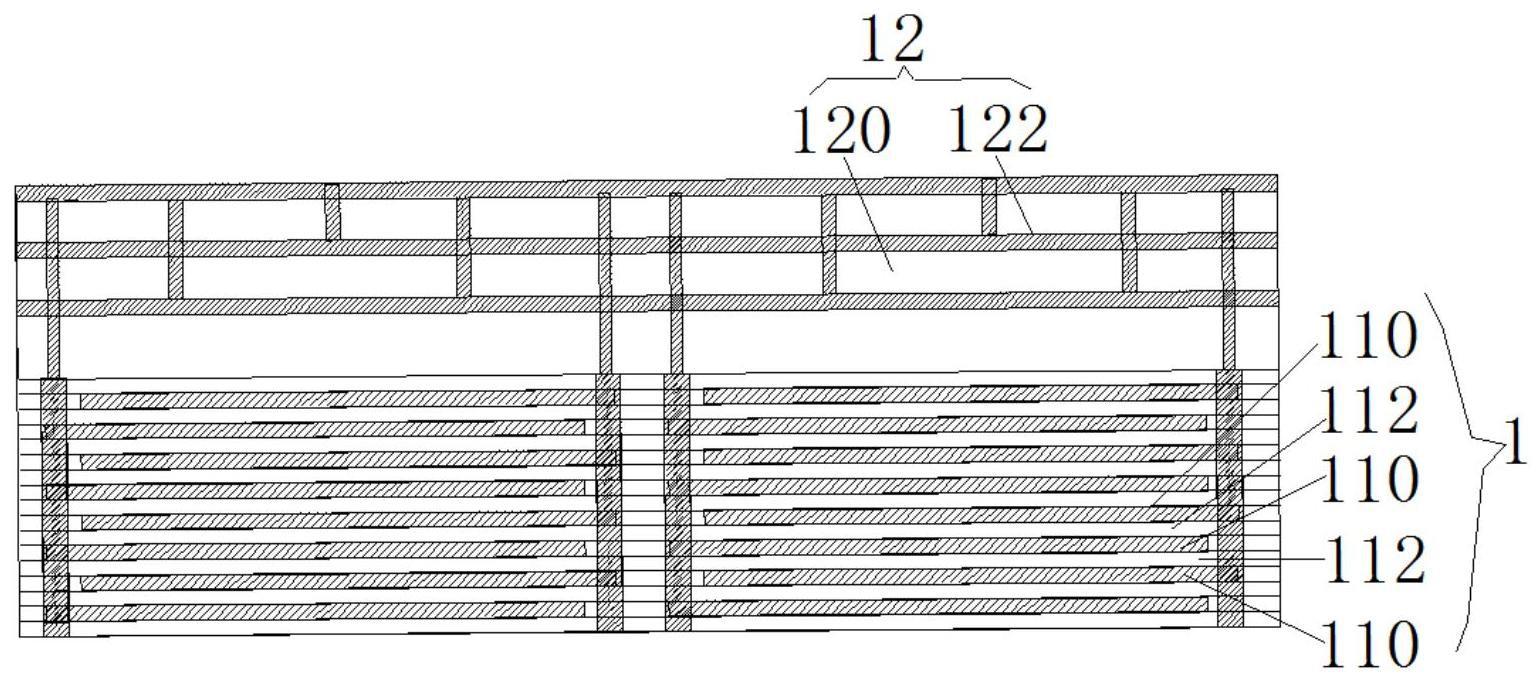

2、第一方面,本申请实施例提供一种封装基板,所述封装基板包括:衬底和互连层;其中,所述互连层设于所述衬底上,所述互连层包括交替堆叠的第一介质层和第一金属层,所述第一金属层包括金属连接线;所述衬底包括交替排列的第二金属层和第二介质层,其中,每两个相邻的所述第二金属层,与二者之间所夹的一个所述第二介质层,形成一个电容单元,每个所述电容单元中的一个第二金属层用于连接电源,另一个第二金属层用于连接地。

3、可选地,所述第二金属层和所述第二介质层分别与所述互连层平行;或者,所述第二金属层和所述第二介质层分别与所述互连层垂直。

4、可选地,所述第二金属层和所述第二介质层分别与所述互连层垂直;所述衬底中设置有凹槽,所述第二金属层和所述第二介质层,沿所述凹槽的侧壁向所述凹槽的中心的方向交替排列,填充在所述凹槽中。

5、可选地,所述第二金属层和所述第二介质层为平面或曲面。

6、可选地,所述衬底中设置有第一连接结构和第二连接结构;所述第一连接结构用于耦合各所述电容单元中处于第一极性的第二金属层,所述第二连接结构用于耦合各所述电容单元中处于第二极性的第二金属层,其中,所述第一极性与所述第二极性相反。

7、可选地,所述互连层中设置有第三连接结构和第四连接结构;所述第三连接结构一端与所述衬底中的所述第一连接结构连接,另一端暴露在所述互连层远离所述衬底的表面;所述第四连接结构一端与所述衬底中的所述第二连接结构连接,另一端暴露在所述互连层远离所述衬底的表面。

8、可选地,所述第一连接结构和所述第二连接结构穿过所述衬底,且所述第一连接结构和所述第二连接结构的末端暴露在所述衬底的、远离所述互连层的表面。

9、可选地,所述第一介质层的材料为聚酰亚胺。

10、可选地,所述第二介质层的材料为陶瓷。

11、第二方面,本申请实施例提供一种电子封装,包括:第一基板、第二基板、第一晶粒和第二晶粒;其中,所述第二基板设于所述第一基板的具有向上开口的腔体内;所述第二基板为前述任一项实施方式所述的封装基板;所述第一基板的上表面和所述第二基板的上表面均设置有凸块;所述第一晶粒的一部分引脚与所述第一基板上的凸块相连,另一部分引脚与所述第二基板上的凸块相连;所述第二晶粒的一部分引脚与所述第一基板上的凸块相连,另一部分引脚与所述第二基板上的凸块相连;所述第二基板上的至少一部分凸块与所述第二基板的互联层中的第一金属连接线相连,以使所述第一晶粒和所述第二晶粒,通过所述第一金属连接线互连。

12、可选地,所述第一基板上、与所述第一晶粒相连的凸块的宽度,大于所述第二基板上、与所述第一晶粒相连的凸块的宽度;所述第一基板上、所述第二晶粒相连的凸块的宽度,大于所述第二基板上、与所述第二晶粒相连的凸块的宽度。

13、可选地,所述第一基板上、与所述第一晶粒相连的凸块之间的节距,大于所述第二基板上、与所述第一晶粒相连的凸块之间的节距;所述第一基板上、与所述第二晶粒相连的凸块之间的节距,大于所述第二基板上、与所述第二晶粒相连的凸块之间的节距。

14、可选地,所述第二基板的衬底中设置有第一连接结构和第二连接结构;所述第一连接结构用于耦合各所述电容单元中处于第一极性的第二金属层,所述第二连接结构用于耦合各所述电容单元中处于第二极性的第二金属层,其中,所述第一极性与所述第二极性相反;所述第二基板的所述互连层中设置有第三连接结构和第四连接结构;所述第三连接结构一端与所述衬底中的所述第一连接结构连接,另一端暴露在所述互连层远离所述衬底的表面,用于与电源或地中的一种相连;所述第四连接结构一端与所述衬底中的所述第二连接结构连接,另一端暴露在所述互连层远离所述衬底的表面,用于与电源或地中的另一种相连。

15、可选地,所述第二基板的衬底中设置有第一连接结构和第二连接结构;所述第一连接结构用于耦合各所述电容单元中处于第一极性的第二金属层,所述第二连接结构用于耦合各所述电容单元中处于第二极性的第二金属层,其中,所述第一极性与所述第二极性相反;所述第一连接结构和所述第二连接结构穿过所述第二基板的衬底,且所述第一连接结构和所述第二连接结构的末端暴露在所述衬底的、远离所述互连层的表面,用于分别与所述第一基板中的电源或地相连。

16、本发明的实施例提供的封装基板及电子封装,互连层设于所述衬底上,所述互连层包括交替堆叠的第一介质层和第一金属层,所述第一金属层包括金属连接线;所述衬底包括交替排列的第二金属层和第二介质层,其中,每两个相邻的所述第二金属层,与二者之间所夹的一个所述第二介质层,形成一个电容单元,每个所述电容单元中的一个第二金属层用于连接电源,另一个第二金属层用于连接地。

技术特征:

1.一种封装基板,其特征在于,所述封装基板包括:衬底和互连层;其中,所述互连层设于所述衬底上,所述互连层包括交替堆叠的第一介质层和第一金属层,所述第一金属层包括金属连接线;

2.根据权利要求1所述的封装基板,其特征在于,所述第二金属层和所述第二介质层分别与所述互连层平行;或者,所述第二金属层和所述第二介质层分别与所述互连层垂直。

3.根据权利要求2所述的封装基板,其特征在于,所述第二金属层和所述第二介质层分别与所述互连层垂直;所述衬底中设置有凹槽,所述第二金属层和所述第二介质层,沿所述凹槽的侧壁向所述凹槽的中心的方向交替排列,填充在所述凹槽中。

4.根据权利要求1所述的封装基板,其特征在于,所述第二金属层和所述第二介质层为平面或曲面。

5.根据权利要求1至4中任一项所述的封装基板,其特征在于,所述衬底中设置有第一连接结构和第二连接结构;所述第一连接结构用于耦合各所述电容单元中处于第一极性的第二金属层,所述第二连接结构用于耦合各所述电容单元中处于第二极性的第二金属层,其中,所述第一极性与所述第二极性相反。

6.根据权利要求5所述的封装基板,其特征在于,所述互连层中设置有第三连接结构和第四连接结构;

7.根据权利要求5所述的封装基板,其特征在于,所述第一连接结构和所述第二连接结构穿过所述衬底,且所述第一连接结构和所述第二连接结构的末端暴露在所述衬底的、远离所述互连层的表面。

8.根据权利要求1至4中任一项所述的封装基板,其特征在于,所述第一介质层的材料为聚酰亚胺。

9.根据权利要求1至4中任一项所述的封装基板,其特征在于,所述第二介5质层的材料为陶瓷。

10.一种电子封装,其特征在于,包括:第一基板、第二基板、第一晶粒和第二晶粒;其中,所述第二基板设于所述第一基板的具有向上开口的腔体内;

11.根据权利要求10所述的电子封装,其特征在于,所述第一基板上、与所述第一晶粒相连的凸块的宽度,大于所述第二基板上、与所述第一晶粒相连的凸块的宽度;

12.根据权利要求10所述的电子封装,其特征在于,所述第一基板上、与所述第一晶粒相连的凸块之间的节距,大于所述第二基板上、与所述第一晶粒相连的凸块之间的节距;

13.根据权利要求10至12中任一项所述的电子封装,其特征在于,所述第二基板的衬底中设置有第一连接结构和第二连接结构;所述第一连接结构用于耦合各所述电容单元中处于第一极性的第二金属层,所述第二连接结构用于耦合各所述电容单元中处于第二极性的第二金属层,其中,所述第一极性与所述第二极性相反;

14.根据权利要求10至12中任一项所述的电子封装,其特征在于,所述第二基板的衬底中设置有第一连接结构和第二连接结构;所述第一连接结构用于耦合各所述电容单元中处于第一极性的第二金属层,所述第二连接结构用于耦合各所述电容单元中处于第二极性的第二金属层,其中,所述第一极性与所述第二极性相反;

技术总结

本申请的实施例公开了一种封装基板及电子封装,涉及集成电路技术领域,为能够有效提高电源质量而发明。所述封装基板包括:衬底和互连层;其中,所述互连层设于所述衬底上,所述互连层包括交替堆叠的第一介质层和第一金属层,所述第一金属层包括金属连接线;所述衬底包括交替排列的第二金属层和第二介质层,其中,每两个相邻的所述第二金属层,与二者之间所夹的一个所述第二介质层,形成一个电容单元,每个所述电容单元中的一个第二金属层用于连接电源,另一个第二金属层用于连接地。本申请适用于传递信号。

技术研发人员:杜树安,钱晓峰,杨晓君,孟凡晓,马龙

受保护的技术使用者:成都海光集成电路设计有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!