一种多芯片TO-LL封装结构与工艺的制作方法

本发明涉及芯片封装,尤其涉及一种多芯片to-ll封装结构与工艺。

背景技术:

1、芯片封装技术就是将内存芯片包裹起来,以避免芯片与外界接触,防止外界对芯片的损害的一种工艺技术。传统to-ll封装的塑封体外型长边处二侧,为了防止芯片下金属基岛与金属模具内模穴之间发生溢料,而在金属模具内模穴中的长边二侧位置,各设计了一个长型的加压顶杆或凸块,如图6和图7所示,也因为如此金属引线框中的芯片下金属基岛却需要保留塑封膜具的加压顶杆或凸块所需要的面积,所以半导体芯片下的金属基岛所剩下能承载半导体mosfet功率芯片的面积就大大的缩小,直接阻碍了大半导体mosfet功率芯片的面积、大容量半导体mosfet功率芯片及大功率半导体mosfet功率芯片的安装,从而造成传统to-ll封装体无法应用在需要更高功率或更高容量的终端产品上。

2、公开号为cn113161242a的中国专利,公开了一种芯片封装工艺,该专利利用具有导电胶层和非导电胶层胶膜实现芯片与基板之间的互联,简化了封装工序,提高生产效率。与本发明相比存在以下不足:

3、仅通过导电胶层和非导电胶层胶膜实现芯片与基板之间的互联,无法解决金属基岛承载半导体mosfet功率芯片的面积小,无法安装更高功率更大半导体mosfet功率芯片,无法放置多个芯片下的多金属基岛。

技术实现思路

1、本发明的目的是为了解决现有技术中仅通过导电胶层和非导电胶层胶膜实现芯片与基板之间的互联,无法解决金属基岛承载半导体mosfet功率芯片的面积小,无法安装更高功率更大半导体mosfet功率芯片,无法放置多个芯片下的多金属基岛的问题,而提出的一种多芯片to-ll封装结构与工艺。

2、为达到上述目的,本发明采用了下列技术方案:

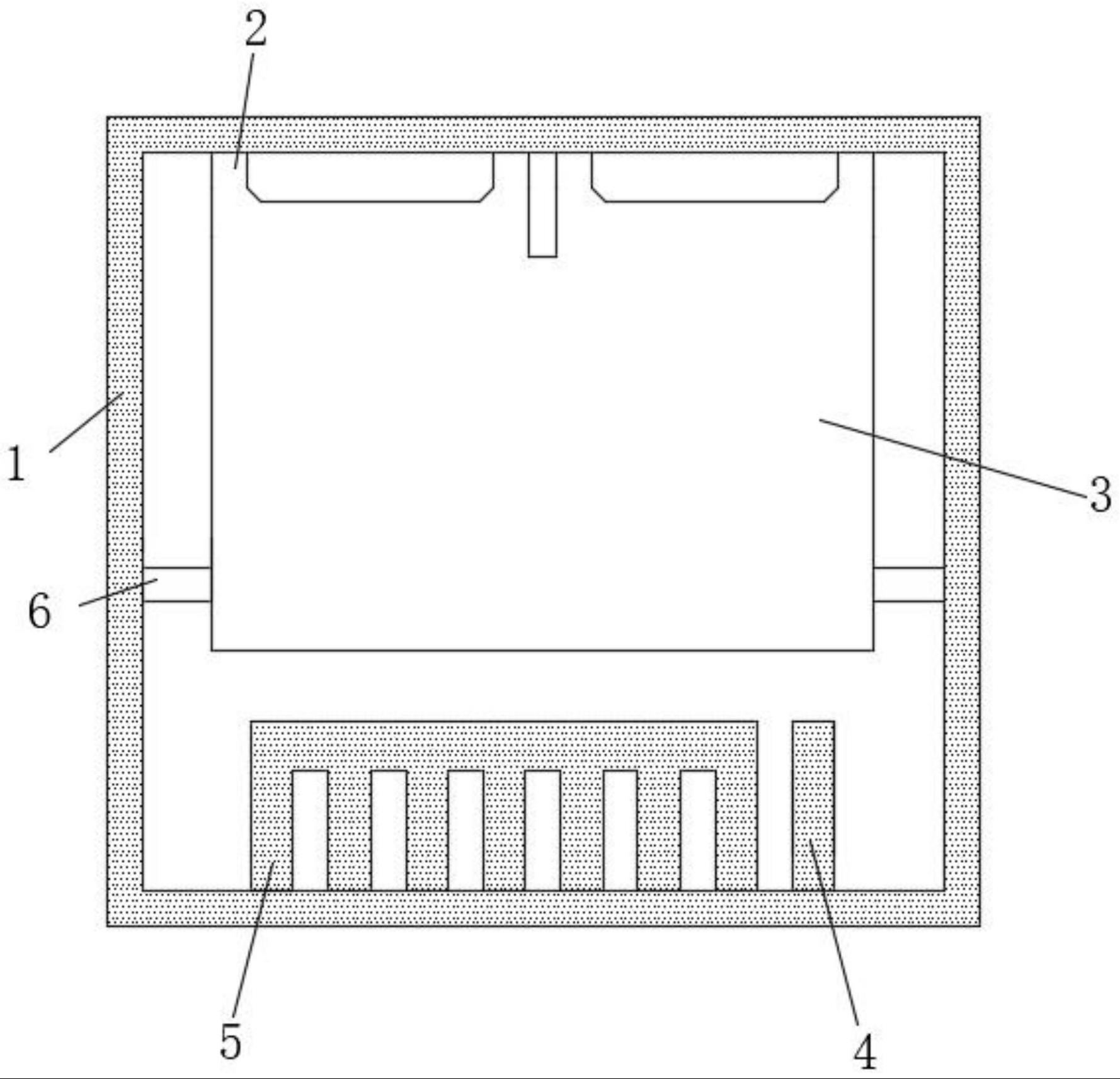

3、一种多芯片to-ll封装结构,包括基岛、塑封体以及mosfet功率芯片,所述塑封体的内部设置有基岛,所述基岛的中部位置设置有mosfet功率芯片,基岛的一端两侧位置分别设置有漏极引脚,所述基岛的两侧外壁上分别固定有连筋,且连筋的端部贯穿塑封体伸出到塑封体外侧;

4、位于所述基岛一侧的塑封体的内部还设置有闸极引脚和源极引脚,所述闸极引脚和源极引脚的一端分别贯穿塑封体伸出到塑封体外侧,且闸极引脚和源极引脚分别通过键合线与mosfet功率芯片连接。

5、一种多芯片to-ll封装工艺,包括将两个mosfet功率芯片封装至同一封装体的封装步骤。

6、作为本发明的进一步技术方案,所述封装步骤包括:

7、将mosfet功率芯片晶圆切割划片;

8、在基岛上方涂布金属导电粘结物质,安装多个mosfet功率芯片;

9、多个mosfet功率芯片的源极利用金属丝、金属带或金属铜片进行键合;

10、再通过塑料塑封、表面处理、激光打印、切筋分离、电性测试、密封包装;制得多芯片to-ll封装结构。

11、作为本发明的进一步技术方案,所述封装步骤包括:

12、将第一个mosfet功率芯片的源极引脚与第二mosfet功率芯片的漏极引脚通过金属丝、金属带或金属铜片相互键合连接;

13、第二个mosfet功率芯片的源极引脚与源极内引脚以及闸极金属内引脚相互键合,形成双mosfet功率芯片串联的结构;再将第二个mosfet功率芯片的漏极引脚与金属引线框的漏极金属内引脚相连。

14、作为本发明的进一步技术方案,所述封装步骤包括:

15、由塑封体下的印刷线路板中的信号线或电源线路与塑封体外印刷线路相互串联,而印刷线路板遵循第一个mosfet功率芯片的源极引脚在印刷线路板上的线路与第二个mosfet功率芯片的漏极印刷线路相互连接,再将第二个mosfet功率芯片的源极印刷线路板上的线路与第二个mosfet功率芯片的源极印刷线路相互连接及第二个mosfet功率芯片的闸极引脚与第二个mosfet功率芯片的闸极印刷线路相互连接,形成利用塑封体下方印刷线路板的各极实施达成串联方法。

16、作为本发明的进一步技术方案,所述封装步骤包括:

17、将第一个mosfet功率芯片的源极引脚与第二个mosfet功率芯片的源极引脚连接;第一个mosfet功率芯片的闸极引脚与第二个mosfet功率芯片的闸极引脚连接;第一个mosfet功率芯片的漏极引脚与第二个mosfet功率芯片的漏极引脚连接。

18、本发明的有益效果:

19、1、本发明可以充分的扩大金属引线框内芯片下金属基岛面积不足的问题,从而可创造单芯片安装最大化、多变化的机会、储备了更大的导热容积与散热面积。

20、2、本发明可以在同一个塑封体内,创造多芯片下各自芯片独立运作各自芯片的功能,如此可以节省更多印刷线路板的使用面积,亦可以减少塑封体使用的数量与成本。

21、3、本发明可以创造多芯片相互串联键合封装,除了可以达到电压需求提升的能力之外;还可以节省更多印刷线路板的使用面积,亦可以减少塑封体使用的数量与成本。

22、4、本发明可以创造多芯片封装的能力,所以直接的减少了多个单芯片封装提数量,也因为如此印刷线路板所使用的面积也是大幅度的减少,从而降低了数个塑封体和引刷线路板的制作、材料、人工、设备、质量与时间等成本。除了减少了诸多塑封体各项的制作,也直接的减少了大量因生产所造成的污染以及使用的能源。

23、5、本发明金属引脚与印刷线路板相互焊接之后,俯视时可以直观的使用肉眼、放大镜或是显微镜轻松直接的观察焊接情况,尤其是金属引脚断面爬锡状况与印刷线路板焊盘锁固金属引脚的情况,无形中增加了生产过程监控的方便性,从而保证焊接质量。

技术特征:

1.一种多芯片to-ll封装结构,包括基岛(3)、塑封体(7)以及mosfet功率芯片(9),所述塑封体(7)的内部设置有基岛(3),所述基岛(3)的中部位置设置有mosfet功率芯片(9),基岛(3)的一端两侧位置分别设置有漏极引脚(2),其特征在于,所述基岛(3)的两侧外壁上分别固定有连筋(6),且连筋(6)的端部贯穿塑封体(7)伸出到塑封体(7)外侧;

2.一种多芯片to-ll封装工艺,应用于权利要求1所述的一种多芯片to-ll封装结构,其特征在于,包括将两个mosfet功率芯片(9)封装至同一封装体的封装步骤。

3.根据权利要求2所述的一种多芯片to-ll封装工艺,其特征在于,所述封装步骤包括:

4.根据权利要求2所述的一种多芯片to-ll封装工艺,其特征在于,所述封装步骤包括:

5.根据权利要求2所述的一种多芯片to-ll封装工艺,其特征在于,所述封装步骤包括:

6.根据权利要求2所述的一种多芯片to-ll封装工艺,其特征在于,所述封装步骤包括:

技术总结

本发明公开了一种多芯片TO‑LL封装结构与工艺,涉及芯片封装技术领域,包括基岛、塑封体以及MOSFET功率芯片,所述基岛的两侧外壁上分别固定有连筋,且连筋的端部贯穿塑封体伸出到塑封体外侧;通过连筋的设置,不需要预留现有技术中在基岛上开设的边框固定位,直接通过边框压住连筋即可实现芯片固定,不影响半导体芯片下的金属基岛所剩下能承载半导体MOSFET功率芯片的面积,不会阻碍了大半导体MOSFET功率芯片的面积、大容量半导体MOSFET功率芯片及大功率半导体MOSFET功率芯片的安装,节省基岛空间。

技术研发人员:李明芬,陈育锋,梁志忠,李尚哲,吕娟娟

受保护的技术使用者:安徽积芯微电子科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!