集成电路晶体管器件的制作方法

1.本文的实施例大体上涉及金属氧化物半导体场效应晶体管(mosfet)器件,具体地涉及用于具有分离栅极配置的沟槽型功率mosfet的栅极触点结构,该分离栅极配置包括通过多氧化物区域横向间隔开并且通过多晶硅栅桥电耦合的一对多晶硅栅极凸角。

背景技术:

2.参照图1,图1示出了功率金属氧化物半导体场效应晶体管(mosfet)器件10的横截面。在该示例中,mosfet是在掺杂有n型掺杂剂的半导体衬底12中和半导体衬底12上形成的n沟道(nmos)型器件,其提供晶体管10的漏极。衬底12具有正面14和背面16。多个沟槽18从正面14沿着深度延伸到衬底12中。沟槽18沿着垂直于横截面的方向(即,进出图示页面)沿长度方向向(即,纵向地)彼此平行地延伸,并且形成条带(这种类型的晶体管器件通常在本领域中被称为条形fet型晶体管)。

3.掺杂有p型掺杂剂的区域24被掩埋在衬底12中从正面14偏移(即,下方)的深度处,并且被定位在每个沟槽18的相对侧平行于正面14延伸。掺杂区域24形成晶体管的主体(沟道)区域,其中沟槽18完全穿过掺杂主体区域24并且进入掺杂主体区域24下方的衬底12。重掺杂有n型掺杂剂的表面注入区域26被提供在衬底12的正面14,并且被定位在每个沟槽18的相对侧平行于正面14延伸,并且与掺杂主体区域24的顶部接触。掺杂区域26形成晶体管的源极,其中沟槽18完全穿过掺杂源极区域26,并且如上面提到的,完全穿过掺杂主体区域24进一步延伸到掺杂主体区域24下方的衬底12中。

4.每个沟槽18的侧壁和底部衬套有绝缘层20。例如,绝缘层20可以包括氧化物层(在实施例中,其在每个沟槽18中从衬底12的暴露表面热生长)。每个沟槽18由多晶硅材料22填充,绝缘层20使多晶硅材料22与衬底12绝缘。多晶硅材料22形成晶体管10的栅极(称为多栅),并且绝缘层20是栅极氧化物层。

5.层的堆叠30被形成在衬底的上表面上方。堆叠30包括未掺杂的氧化物(例如原硅酸四乙酯(teos))层32和玻璃(例如硼磷硅玻璃(bpsg))层34。如果需要,堆叠30还可以包括附加的绝缘层和/或势垒层。

6.参照图1的左侧,源极金属触点40延伸穿过堆叠30的层,被定位于相邻沟槽18的位置之间,以与掺杂源极区域26电接触。每个源极金属触点40沿着深度延伸到衬底中,以穿过掺杂源极区域26并且部分进入掺杂主体区域24(从而为被绑定至源极的晶体管10提供主体触点)。源极金属层42在堆叠30和源极金属触点40两者上方延伸,以提供到所有源极金属触点40以及在所有源极金属触点40之间的电连接。堆叠30的层使源极金属层42和源极金属触点40两者与多栅(多晶硅区域22)绝缘。

7.现在参照图1的右侧,栅极金属触点46延伸穿过堆叠层30,被定位为与沟槽18的位置对准,以与每个沟槽18中的多晶硅区域22电接触。尽管未明确图示,但要理解的是,栅极金属触点46可以至少部分地沿着深度延伸到多晶硅区域22中。栅极金属层48在堆叠30和栅极金属触点46二者上方延伸,以提供到所有栅极金属触点46以及在所有源极金属触点46之

间的电连接。堆叠层30将栅极金属层48和栅极金属触点46二者与源极金属触点和源极区域绝缘。

8.在实践中,图1的左侧和右侧的横截面实际上在垂直于横截面的方向上(即,进出图示页面)纵向地彼此偏移。在该配置中,绝缘分离被提供在源极金属层42和栅极金属层48之间。

9.漏极金属层44在衬底12的背面16上方延伸以提供到漏极的金属连接。

10.晶体管10可以替代地是pmos型晶体管,其中衬底12和掺杂源极区域16二者都是p型掺杂的并且主体区域14是n型掺杂的。

11.现在参照图2,图2示出了功率金属氧化物半导体场效应晶体管(mosfet)器件50的横截面。在该示例中,mosfet是在掺杂有n型掺杂剂的半导体衬底52中和半导体衬底52上形成的n沟道(nmos)型器件,其提供晶体管50的漏极。衬底52具有正面54和背面56。多个沟槽58从正面54沿着深度延伸到衬底52中。沟槽58沿着垂直于横截面的方向(即,进出图示页面)纵向(即,纵向地)彼此平行地延伸,并且形成条带(这种类型的晶体管器件通常在本领域中被称为条形fet型晶体管)。

12.掺杂有p型掺杂剂的区域64被掩埋在衬底52中与正面54偏移(即,下方)的深度处,并且被定位在每个沟槽58的相对侧平行于正面54延伸。掺杂区域64形成晶体管的主体(沟道)区域,沟槽58完全穿过掺杂主体区域64并且进入掺杂主体区域64下方的衬底52。掺杂有n型掺杂剂的区域66被提供在衬底52的正面54,并且被定位在每个沟槽58的相对侧平行于正面54延伸,并且与掺杂主体区域64的顶部接触。掺杂区域66形成晶体管的源极,其中沟槽58完全穿过掺杂源极区域66,并且如上面提到的,完全通过掺杂主体区域64进一步延伸到掺杂主体区域64下方的衬底52中。

13.每个沟槽58的侧壁和底部衬有第一(厚)绝缘层60a。例如,绝缘层60a可以包括厚氧化物层。沟槽58然后由第一多晶硅材料62a填充,其中绝缘层60a使第一多晶硅材料62a与衬底52绝缘。多晶硅材料62a是重n型掺杂的多晶硅材料(例如磷掺杂的,掺杂浓度为5x10

20

at/cm3)。在用于制造晶体管50的过程期间,绝缘层60a的上部(其将与掺杂主体区域64和掺杂区域66都相邻)从沟槽58去除,以暴露多晶硅材料62a的对应上部61(参见图3a)。多晶硅材料62a的该暴露的上部61然后被转换(例如使用热氧化过程)以形成多氧化物区域68,该多氧化物区域68在沟槽58中与多晶硅材料62a的剩余(下部)部分63竖直对准(参见图3b)。多晶硅材料62a的这个剩余的下部63形成晶体管50的场板电极(也称为多源极区域,因为它通常与源极区域66电短路-该电连接未在附图中明确示出)。然后每个沟槽58的上部的侧壁和底部衬有第二(薄)绝缘层60b(参见图3c)。例如,绝缘层60b可以包括热生长的薄氧化物层。每个沟槽58的上部然后由第二多晶硅材料62b填充,其中绝缘层60b使第二多晶硅材料62b与衬底52(包括区域64和66)绝缘。第二多晶硅材料62b形成晶体管50的栅极(也称为多栅区域),并且包括在多氧化物区域68的相对侧延伸的第一(例如左侧)栅极凸角621和第二(例如右侧)栅极凸角622。第一栅极凸角和第二栅极凸角通过在多氧化物区域68上方延伸的栅桥部分623电耦合。绝缘层60b形成栅极氧化物层。

14.层的堆叠70在衬底的上表面上方形成。堆叠70包括未掺杂的氧化物(例如原硅酸四乙酯(teos))层72和玻璃(例如硼磷硅玻璃(bpsg))层74。如果需要,堆叠70还可以包括附加的绝缘层和/或势垒层。

15.参照图2的左侧,源极金属触点80延伸穿过堆叠70的层,被定位于相邻沟槽58的位置之间,以与掺杂源极区域66电接触。每个源极金属触点80沿着深度延伸到衬底中,以穿过掺杂源极区域66并且部分进入掺杂主体区域64(从而为被绑定至源极的晶体管50提供主体触点)。源极金属层82在堆叠70和源极金属触点80两者上方延伸,以提供到所有源极金属触点80以及在所有源极金属触点80之间的电连接。堆叠70的层使源极金属层82和源极金属触点80两者与多栅(第二多晶硅区域62b)绝缘。

16.现在参照图2的右侧,栅极金属触点86延伸穿过堆叠70的层,被定位为与沟槽58的位置对准,以与每个沟槽58中的第二多晶硅区域62b形成电接触(例如通过在桥接部分623的位置处接触)。要注意的是,栅极金属触点86优选地沿着深度至少部分地延伸到填充沟槽中,例如延伸到桥接部分623的至少上部中(并且可能完全延伸穿过桥接部分)。栅极金属层88在堆叠70和栅极金属触点86两者上方延伸,以提供到所有栅极金属触点86以及在所有栅极金属触点86之间的电连接。堆叠70的层使栅极金属层88和栅极金属触点86两者与源极金属触点和源极区域绝缘。多氧化物区域68使多源极区域62a与栅极金属触点86绝缘。

17.在实践中,图2的左侧和右侧的横截面实际上在垂直于横截面的方向上(即,进出图示页面)纵向地彼此偏移。在该配置中,绝缘分离在源极金属层82和栅极金属层88之间提供。

18.漏极金属层84在衬底52的背面56上方延伸以提供到漏极的金属连接。

19.晶体管50可以替代地是pmos型晶体管,其中衬底52和掺杂源极区域56二者都是p型掺杂的并且主体区域54是n型掺杂的。

20.图4a示出了对应于图2左侧的晶体管50的单个单元的扫描电子显微照片(sem)横截面图像。

21.在多氧化物区域68(参见图3b)的形成期间,随着多晶硅材料62a被转换为多氧化物区域68,存在横向和竖直材料膨胀。这种膨胀引起了可以在多氧化物材料内产生空隙(或接缝或空腔)的张力。多氧化物区域68中的这种空隙的存在和位置是不可预测的。图4b示出了聚焦在沟槽58所在区域的扫描电子显微照片(sem)横截面图像,以通过示例图示这种空隙的存在(也参见图3b)。取决于沟槽58的宽度和由凸角621、622和桥623形成的多栅的大小,多氧化物区域68中的空隙可以延伸到靠近多栅的内表面(参见图3c),并且这可能对栅极触点86的形成有影响,并且如下面将要讨论的,增加了通过多源极区域62a对源极形成短路的风险。

22.用于形成栅极触点86的过程使用具有与沟槽58的中心对准的掩模开口的掩模。使用该掩模执行的蚀刻产生栅极开口,其延伸穿过堆叠70并且至少部分地进入(如果未完全通过)形成多栅的第二多晶硅区域62b的桥623。该蚀刻可以包括多个离散的蚀刻步骤,包括去除堆叠70的层的第一蚀刻和延伸到桥623中期望深度的第二蚀刻。掩模开口和对应的栅极开口的大小通常被设计为大约(更优选地小于)沟槽58的大小(宽度)的二分之一,并且一般来说优选地与沟槽的中心对准。然后由钛-氮化钛(ti-tin)材料形成的势垒层92被共形地沉积到蚀刻的栅极开口中,然后栅极开口用由导电材料(诸如例如钨)制成的插塞填充以形成栅极触点86。图4c示出了聚焦在栅极触点86上的扫描电子显微照片(sem)横截面图像,并且图示栅极开口已完全穿过栅桥623以到达多氧化物区域68。

23.对第二蚀刻的深度上的控制难以确保,并且多氧化物区域68中的空隙的可能存在

和位置难以预测。因此存在不可忽略的风险,即,第二蚀刻将完全穿过桥623,其中栅极开口部分地延伸到多氧化物区域68中以到达空隙。共形沉积的ti-tin势垒层可能无法充分覆盖该位置,因为空隙与栅极开口组合所呈现的拓扑困难,因此被沉积在栅极开口中的用于插塞的导电材料可能会侵入空隙,并且可能将多栅短路到由场板提供的多源极(如上面提到的,其被电连接至源极区域)。

24.需要解决功率mosfet器件中的前述问题,并且提供一种更好的解决方案,用于与包括多晶硅栅极凸角对的分离栅极配置进行电接触,该多晶硅栅极凸角对由多晶硅区域横向间隔开并且由多晶硅栅桥电耦合。

技术实现要素:

25.本公开的目的是提供集成电路晶体管器件,以至少部分地解决现有技术中存在的上述问题。

26.一种集成电路晶体管器件,包括:半导体衬底,提供漏极;第一掺杂区域,被掩埋在所述半导体衬底中提供主体;第二掺杂区域,在所述半导体衬底中提供源极,其中所述第二掺杂区域与所述第一掺杂区域相邻;沟槽,延伸到所述半导体衬底中并且穿过所述第一掺杂区域和所述第二掺杂区域;多氧化物区域,在所述沟槽内;多栅区域,在所述沟槽内,所述多栅区域包括:所述多氧化物区域的第一侧上的第一栅极凸角以及所述多氧化物区域的与所述第一侧相对的第二侧上的第二栅极凸角;绝缘层,在所述第一掺杂区域和沟槽上方延伸;以及用于所述沟槽的栅极触点对,所述栅极触点对包括:第一栅极触点,延伸穿过所述绝缘层并且到所述第一栅极凸角中;以及第二栅极触点,延伸穿过所述绝缘层并且到所述第二栅极凸角中。

27.根据一个或多个实施例,其中所述第一栅极触点和所述第二栅极触点处于横向并排布置。

28.根据一个或多个实施例,其中所述第一栅极触点和所述第二栅极触点在所述沟槽的纵向方向上彼此偏移。

29.根据一个或多个实施例,其中没有在垂直于所述沟槽的所述纵向方向的平面中的所述沟槽的横截面穿过所述第一栅极触点和所述第二栅极触点二者。

30.根据一个或多个实施例,其中所述多栅区域还包括在所述多氧化物区域上方延伸并且将所述第一栅极凸角电耦合至所述第二栅极凸角的桥接区域。

31.根据一个或多个实施例,其中所述桥接区域的一部分在所述第一栅极触点和所述第二栅极触点之间横向地延伸。

32.根据一个或多个实施例,其中所述多氧化物区域包括空隙,并且其中所述第一栅极触点和所述第二栅极触点中的每个栅极触点在所述沟槽的横向方向上相对于所述空隙偏移。

33.根据一个或多个实施例,其中所述多氧化物区域与所述沟槽的中心对准,并且其中所述第一栅极触点和所述第二栅极触点中的每个栅极触点的中心位于对应的所述第一栅极凸角和所述第二栅极凸角的中心与所述沟槽的中心之间。

34.根据一个或多个实施例,集成电路晶体管器件还包括:金属层,在所述绝缘层上方延伸并且电连接所述第一栅极触点和所述第二栅极触点。

35.根据一个或多个实施例,集成电路晶体管器件还包括:栅极绝缘体层,沿着所述沟槽的壁并且被定位于所述第一栅极凸角和所述第二栅极凸角中的每个栅极凸角与所述半导体衬底之间。

36.根据一个或多个实施例,集成电路晶体管器件还包括:在所述沟槽内的多源极区域,其中所述多源极区域与所述多氧化物区域纵向地对准。

37.根据一个或多个实施例,其中所述多氧化物区域是所述多源极区域的氧化部分。

38.根据一个或多个实施例,其中所述第一栅极触点和所述第二栅极触点中的每个栅极触点包括钛-氮化钛势垒层和钨塞。

39.本公开的另一方面提供了一种集成电路晶体管器件,包括:半导体衬底,提供漏极;第一掺杂区域,被掩埋在所述半导体衬底中提供主体;第二掺杂区域,在所述半导体衬底中提供源极,其中所述第二掺杂区域与所述第一掺杂区域相邻;沟槽,延伸到所述半导体衬底中并且穿过所述第一掺杂区域和所述第二掺杂区域;绝缘多源极区域,在所述沟槽内;多氧化物区域,在所述沟槽内并且与所述绝缘多源极区域对准,其中所述多氧化物区域包括空隙;第一绝缘栅极凸角,在所述多氧化物区域的第一侧上;第二绝缘栅极凸角,在所述多氧化物区域的与所述第一侧相对的第二侧上;第一栅极触点,延伸到所述第一栅极凸角中,所述第一栅极触点相对于所述沟槽的纵向中心横向地偏移,使得所述第一栅极触点的深度未到达所述空隙;以及第二栅极触点,延伸到所述第二栅极凸角中,所述第二栅极触点相对于所述沟槽的所述纵向中心横向地偏移,使得所述第二栅极触点的深度未到达所述空隙。

40.根据一个或多个实施例,集成电路晶体管器件还包括:绝缘层,在所述第一掺杂区域和沟槽上方延伸,其中所述第一栅极触点和所述第二栅极触点延伸穿过所述绝缘层,并且通过所述绝缘层的一部分在所述绝缘层的级别彼此横向地绝缘。

41.根据一个或多个实施例,其中所述第一栅极触点和所述第二栅极触点处于横向并排布置。

42.根据一个或多个实施例,其中所述第一栅极触点和所述第二栅极触点在所述沟槽的纵向方向上彼此偏移。

43.根据一个或多个实施例,集成电路晶体管器件还包括:桥接区域,在所述多氧化物区域上方延伸并且将所述第一绝缘栅极凸角电耦合至所述第二绝缘栅极凸角。

44.根据一个或多个实施例,其中所述桥接区域在所述第一栅极触点和所述第二栅极触点之间横向地延伸。

45.根据一个或多个实施例,其中所述多氧化物区域是所述绝缘多源极区域的氧化部分。

46.本公开的另一方面提供了一种集成电路晶体管器件,包括:半导体衬底,提供漏极;第一掺杂区域,被掩埋在所述半导体衬底中提供主体;第二掺杂区域,在所述半导体衬底中提供源极,其中所述第二掺杂区域与所述第一掺杂区域相邻;沟槽,延伸到所述半导体衬底中并且穿过所述第一掺杂区域和所述第二掺杂区域;多氧化物区域,在所述沟槽内;多栅区域,在所述沟槽内,所述多栅区域包括:所述多氧化物区域的第一侧上的第一栅极凸角、所述多氧化物区域的与所述第一侧相对的第二侧上的第二栅极凸角以及在所述多氧化物区域上方延伸并且将所述第一绝缘栅极凸角电耦合至所述第二绝缘栅极凸角的桥接区

域;绝缘层,在所述第一掺杂区域和所述沟槽上方延伸;以及栅极触点,延伸穿过所述绝缘层并且到所述沟槽的所述第一栅极凸角中,并且其中所述桥接区域横向地延伸远离所述栅极触点。

47.根据一个或多个实施例,其中所述多氧化物区域包括空隙,并且其中所述栅极触点在所述沟槽的横向方向上相对于所述空隙偏移。

48.利用本公开的实施例,有利地使触点的放置不会有跨过栅极氧化物的桥接并且使多栅与掺杂源极区域短路的风险。

附图说明

49.为了更好地理解实施例,现在将仅通过示例参照附图,其中:

50.图1是功率金属氧化物半导体场效应晶体管(mosfet)器件的横截面;

51.图2是功率mosfet器件的横截面;

52.图3a至图3c示出了图2的功率mosfet器件的制造中的过程步骤;

53.图4a至图4c是图2的功率mosfet器件的横截面的扫描电子显微图片图像;

54.图5是功率mosfet器件的横截面;

55.图6a和图6b分别图示了图2和图5的功率mosfet器件的栅极触点布局配置;

56.图7是功率mosfet器件的横截面;

57.图8a至图8b是图7的功率mosfet器件的横截面的扫描电子显微图片图像;以及

58.图9a和图9b分别图示了图5和图7的功率mosfet器件的栅极触点布局配置。

具体实施方式

59.针对本文的讨论,要注意的是,术语“纵向”是指例如沿着沟槽的长度延伸的第一方向,并且术语“横向”是指例如沿着沟槽的宽度延伸的第二方向。纵向和横向方向彼此垂直,并且平行于半导体衬底的上表面延伸。

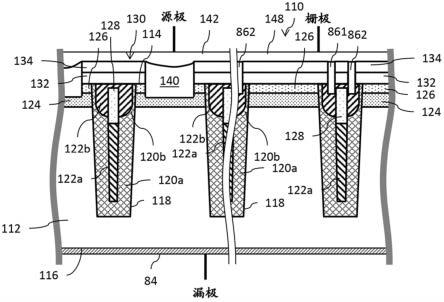

60.现在参照图5,图5示出了功率金属氧化物半导体场效应晶体管(mosfet)器件110的横向横截面。在该示例中,mosfet是在掺杂有n型掺杂剂的半导体衬底112中和半导体衬底112上形成的n沟道(nmos)型器件,其提供晶体管110的漏极。衬底112具有正面114和背面116。多个沟槽118从正面114沿着深度延伸到衬底112中。沟槽118沿着垂直于横截面的方向(即,进出图示页面)纵向地彼此平行延伸期望长度,并且形成条带(这种类型的晶体管器件通常在本领域中被称为条形fet型晶体管)。

61.掺杂有p型掺杂剂的区域124被掩埋在衬底112中与正面114偏移(即,下方)的深度处,并且被定位为在每个沟槽118的相对侧平行于正面114横向延伸。掺杂区域124形成晶体管的主体(沟道)区域,沟槽118完全穿过掺杂主体区域124并且进入掺杂主体区域124下方的衬底112。掺杂有n型掺杂剂的表面注入区域126被提供在衬底112的正面114,并且被定位为在每个沟槽118的相对侧平行于正面114延伸,并且与掺杂主体区域124的顶部接触。掺杂区域126形成晶体管的源极,其中沟槽118完全穿过掺杂源极区域126,并且如上面提到的,完全延伸穿过掺杂主体区域124进一步到达掺杂主体区域124下方的衬底112中。

62.每个沟槽118的侧壁和底部衬有第一绝缘层120a。例如,绝缘层120a可以包括厚氧化物层。沟槽118然后由第一多晶硅材料122a填充,其中绝缘层120a使第一多晶硅材料122a

与衬底112绝缘。第一多晶硅材料122a是重n型掺杂的多晶硅材料(例如磷掺杂的,掺杂浓度为5x10

20

at/cm3)。在制造晶体管110的过程期间,绝缘层120a的上部(其将与掺杂主体区域124和掺杂区域126都相邻)从沟槽118去除,以暴露第一多晶硅材料122a的对应上部。第一多晶硅材料122a的该暴露的上部然后被转换(例如使用热氧化过程)以形成多氧化物区域128,该多氧化物区域128在沟槽118中与第一多晶硅材料122a的剩余(下部)部分竖直对准。第一多晶硅材料122a的这个剩余的下部形成晶体管110的场板电极(也称为多源极区域,因为它通常与源极区域126电短路-该电连接未在附图中明确示出)。然后每个沟槽118的上部的侧壁和底部衬有第二绝缘层120b。例如,绝缘层120b可以包括热生长的氧化物层。每个沟槽118的上部然后由第二多晶硅材料122b填充,其中绝缘层120b使第二多晶硅材料122b与衬底112(包括区域124和126)绝缘。第二多晶硅材料122b形成晶体管110的栅极(也称为多栅区域),并且包括在多氧化物区域128的相对侧的沟槽中纵向延伸的第一(例如左侧)栅极凸角621和第二(例如右侧)栅极凸角622。第一栅极凸角和第二栅极凸角通过在多氧化物区域128上方横向延伸的栅桥部分623连接。绝缘层120b形成栅极氧化物层。

63.层堆叠130在衬底的上表面上方形成。堆叠130包括未掺杂的氧化物(例如原硅酸四乙酯(teos))层132和玻璃(例如硼磷硅玻璃(bpsg))层134。如果需要,堆叠130还可以包括附加的绝缘层和/或势垒层。

64.参照图5的左侧,源极金属触点140延伸穿过堆叠130的层,被定位在相邻沟槽118的位置之间,以与掺杂源极区域126电接触。每个源极金属触点140沿着深度延伸到衬底中,以穿过掺杂源极区域136并且部分进入掺杂主体区域134(从而为被绑定至源极的晶体管110提供主体触点)。源极金属层142在堆叠130和源极金属触点140两者上方延伸,以提供到所有源极金属触点140以及在所有源极金属触点140之间的电连接。堆叠130的层使源极金属层142和源极金属触点140两者与多栅(第二多晶硅区域122b)绝缘。

65.现在参照图5的右侧,每个多栅的栅极金属触点由一对触点861和862形成,其中每个触点861、862延伸穿过堆叠130的层,与多栅的对应凸角621、622(分别)的位置竖直对准定位,以与每个沟槽118中的第二多晶硅区域122b的相应凸角进行电接触。在优选实施方式中,每个栅极金属触点861、862沿着深度至少部分地延伸到桥623的任一侧上的对应凸角621、622的上部中。栅极金属层148在堆叠130和栅极金属触点861、862二者上方延伸,以提供到所有栅极金属触点861、862以及在所有栅极金属触点861、862之间的电连接。堆叠130的层使栅极金属层148和栅极金属触点861、862与源极金属触点和源极区域绝缘。要注意的是,堆叠的一部分用于在堆叠内的层的级别使触点861与触点862横向绝缘。

66.在实践中,图5的左侧和右侧的横截面实际上在垂直于横截面的方向上(即,进出图示页面)纵向地彼此偏移。在该配置中,绝缘分离被提供在源极金属层142和栅极金属层148之间。

67.漏极金属层144在衬底112的背面116上方延伸,以提供到漏极的金属连接。

68.晶体管110可以替代地是pmos型晶体管,其中衬底112和掺杂源极区域126二者都是p型掺杂的并且主体区域124是n型掺杂的。

69.图6a和图6b是用于比较晶体管50和110的布局的平面图(即,向下看向衬底的前表面),其中具体焦点示出了触点86和触点对861和862的相对位置。虚线指示每个纵向延伸沟槽的中心线,并且点划线指示多栅的每个凸角的纵向中心的大致位置。图6a大体上对应于

图2右侧所示的实施方式,而图6b大体上对应于图5右侧所示的实施方式。虽然在图6b中示出仅每个沟槽的一对触点861和862,但是要理解的是,这仅是示例,并且如果需要,每个沟槽可以使用多于一对触点。

70.利用一对并排布置的触点861和862的图5所示的栅极触点结构解决了与可以结合可能包括空隙的多氧化物区域148产生的问题的关注。一对触点861和862的组合大小优选地基本上等于图2所示的栅极触点86的大小,因此将在栅极电阻方面提供基本相同的性能。将每个栅极触点分离为两个部分(触点861和862)并且将每个部分与多栅的对应凸角621、622竖直对准避免了与沟槽的中心部分(即,在栅桥区域的位置处)的多栅接触,从而将用于形成触点开口的蚀刻到达空隙位置的风险最小化。

71.在该图5实施例中,每个触点861、862可以具有介于0.1μm和10μm之间的长度尺寸(在纵向方向上)和介于0.1μm和1μm之间的宽度尺寸(在横向方向上垂直于长度尺寸)。

72.要注意的是,在图5所示的实施方式中,在一对触点861、862的横向并排布置的情况下,给定位置处的横截面沿着沟槽的长度纵向穿过两个触点861、862。具有这种实施方式的器件的制造要求栅极掩模包括非常薄的抗蚀剂部分,该抗蚀剂部分与该给定位置处的相邻触点之间的间隔对准。这个非常薄的抗蚀剂部分可能会在制造期间剥离,并且对形成栅极触点开口的蚀刻操作的准确性产生不利影响。例如,可能会出现针对栅极触点中的每个栅极触点的畸形开口,或者可能会出现将并排的一对触点的两个单独开口合并为一个大开口的合并开口(merger)。这个关注的解决方案是设计栅极掩模,使得用于产生触点861、862的各个掩模开口在垂直于横截面的方向上(即,进出图示页面)彼此纵向偏移。

73.由掩模开口的这种布置产生的晶体管110’结构如图7所示。图7中的相同附图标记是指与图5中相同或类似的部分。图7的左侧对应于图5的左侧。图7的中间和右侧部分图示了针对给定沟槽纵向偏移栅极触点861和862,这是由掩模开口的对应纵向偏移引起的。具体地,图7的中间部分示出了在用于形成第一栅极触点861的掩模开口已经被利用以便与多栅的对应第一(左侧)凸角621进行电接触的位置处的横截面。图7的右侧部分示出了在用于形成第二栅极触点862的掩模开口已经被利用以便与多栅的对应第二(右侧)凸角622进行电接触的位置处的横截面。尽管各个栅极开口有纵向偏移,但要注意的是,沟槽内的多栅的每个栅极触点仍由一对触点861和862形成。

74.在该图7实施例中,每个触点861、862可以具有介于0.1μm和10μm之间的长度尺寸(在纵向方向上)和介于0.1μm和1μm之间的宽度尺寸(在横向方向上垂直于长度尺寸)。要注意的是,由于图7中的触点861、862的纵向偏移,每个单独的触点可以被制造为具有比图5实施例的对应触点更宽的宽度,其中并排布置可以对触点宽度施加约束。

75.图8a示出了晶体管110'的单个单元的扫描电子显微照片(sem)横截面图像,其对应于图7的中部,并且聚焦在用于多栅的凸角621的栅极触点861上。

76.图8b示出了晶体管110'的单个单元的扫描电子显微照片(sem)横截面图像,其对应于图7的右侧,并且聚焦在用于多栅的凸角622的栅极触点862上。

77.图9a和图9b是用于比较晶体管110和110’的布局的平面图(即,向下看向衬底的前表面),其中具体焦点示出了触点对861和862的相对位置。虚线指示每个纵向延伸沟槽的中心线,并且点划线指示多栅的每个凸角的中心的大致位置。要注意的是,每个触点861、862的纵向中心位于对应栅极凸角的纵向中心和沟槽的纵向中心之间。这确保了触点的放置不

会有跨过栅极氧化物的桥接并且使多栅与掺杂源极区域短路的风险。图9a大体上对应于图7右侧所示的实施方式,而图9b大体上对应于图7中部和右侧所示的实施方式。虽然仅每个沟槽的一对触点861和862在图9a和9b中示出,要理解的是,这仅是示例,并且如果需要,每个沟槽可以使用多于一对的触点。通过图9b,要注意的是,给定沟槽的一对触点861和862的纵向偏移使得没有在垂直于沟槽的纵向方向的平面中的沟槽的横截面穿过第一栅极触点和第二栅极触点二者。这通过在沟槽的纵向方向上在第一栅极触点的端部和第二栅极触点的相邻端部之间设置足够的纵向偏移距离d来实现。

78.在实施例中,一种集成电路晶体管器件包括:半导体衬底,提供漏极;第一掺杂区域,被掩埋在半导体衬底中提供主体;第二掺杂区域,在半导体衬底中提供源极,其中第二掺杂区域与第一掺杂区域相邻;沟槽,延伸到半导体衬底中并且穿过第一掺杂区域和第二掺杂区域;沟槽内的多氧化物区域;沟槽内的多栅区域,所述多栅区域包括:多氧化物区域的第一侧上的第一栅极凸角以及多氧化物区域的与所述第一侧相对的第二侧上的第二栅极凸角;绝缘层,在第一掺杂区域和沟槽上方延伸;以及用于所述沟槽的栅极触点对。该栅极触点对包括:第一栅极触点,延伸穿过绝缘层并且进入第一栅极凸角中;以及第二栅极触点,延伸穿过绝缘层并且到第二栅极凸角中。

79.在实施例中,一种集成电路晶体管器件包括:半导体衬底,提供漏极;第一掺杂区域,被掩埋在半导体衬底中提供主体;提供源极的半导体衬底中的第二掺杂区域,其中第二掺杂区域与第一掺杂区域相邻;沟槽,延伸到半导体衬底中并且穿过第一掺杂区域和第二掺杂区域;沟槽内的绝缘多源极区域;多氧化物区域,在沟槽内并且与所述绝缘多源极区域对准,其中所述多氧化物区域包括空隙;多氧化物区域的第一侧的第一绝缘栅极凸角;多氧化物区域的与所述第一侧相对的第二侧的第二绝缘栅极凸角;延伸到第一栅极凸角中的第一栅极触点,所述第一栅极触点与沟槽的纵向中心横向地偏移,使得第一栅极触点的深度不到达所述空隙;以及延伸到第二栅极凸角中的第二栅极触点,所述第二栅极触点与沟槽的纵向中心横向地偏移,使得第二栅极触点的深度不到达所述空隙。

80.虽然本发明已经在附图和前述描述中详细地图示和描述,但是这种图示和描述被认为是说明性的或示例性的,而不是限制性的;本发明不被限于所公开的实施例。通过研究附图、公开内容和所附权利要求,在实践要求保护的本发明时,所公开的实施例的其他变化可以被本领域技术人员理解和实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1