一种抗单粒子烧毁的横向功率器件的制作方法

1.本实用新型涉及功率半导体器件领域,尤其是一种抗单粒子烧毁的横向功率器件。

背景技术:

2.以ldmos为典型的横向功率器件更容易与cmos工艺兼容,同时具有更高的热稳定性、更高的增益、更低的噪音以及恒定的输入阻抗等优点,因此被广泛应用于电力电子系统。但当ldmos器件处于辐照环境中时,衬底中产生的电子空穴对会被漏极和源极收集,增加器件的漏极缓冲电流,使得器件更容易发生单粒子烧毁效应。

技术实现要素:

3.本发明人针对上述问题及技术需求,提出了一种抗单粒子烧毁的横向功率器件,本实用新型的技术方案如下:

4.一种抗单粒子烧毁的横向功率器件,该横向功率器件包括:

5.衬底,p-阱区和n型漂移区形成在所述衬底的上表面,所述p-阱区内部包含第一空腔;p+源区和n+源区形成在所述p-阱区的上表面;n-漏极缓冲区形成在所述n型漂移区的远离所述p-阱区的一侧的上表面,所述n-漏极缓冲区内部包含第二空腔;n+漏区形成在所述n-漏极缓冲区的上表面;

6.所述p-阱区、n型漂移区、p+源区、n+源区、n-漏极缓冲区和n+漏区的表面还形成有器件顶层,所述器件顶层包括源极、漏极、栅极、氧化层和场板。

7.其进一步的技术方案为,所述第一空腔为多边形结构或球形结构或椭球形结构。

8.其进一步的技术方案为,所述p+源区和n+源区形成在所述p-阱区的远离所述n型漂移区的一侧的上表面,所述p-阱区在纵向剖面上为l型结构,所述第一空腔在纵向剖面上也为l型结构。

9.其进一步的技术方案为,所述第一空腔在横向上的长度与所述p-阱区在横向上的长度之间的比例达到第一比例阈值。

10.其进一步的技术方案为,所述第二空腔为多边形结构或球形结构或椭球形结构。

11.其进一步的技术方案为,所述n+漏区形成在所述n-漏极缓冲区的远离所述p-阱区的一侧的上表面,所述n-漏极缓冲区在纵向剖面上为l型结构,所述第二空腔在纵向剖面上也为l型结构。

12.其进一步的技术方案为,所述第二空腔在横向上的长度与所述n-漏极缓冲区在横向上的长度之间的比例达到第二比例阈值。

13.其进一步的技术方案为,所述p-阱区相对于所述p+源区和n+源区外露的区域及其相接的部分区域所述n型漂移区的上表面形成有第一高度的所述氧化层,所述n型漂移区的其余区域的上表面以及所述n-漏极缓冲区相对于所述n+漏区外露的区域的上表面形成有第二高度的所述氧化层;

14.所述p+源区和n+源区的上表面形成有所述第二高度的所述源极,且所述源极与所述氧化层之间形成预定间隔;

15.所述n+漏区的上表面形成有所述第二高度的所述漏极;

16.第一高度的所述氧化层的上表面形成有所述栅极,所述栅极的上表面与所述源极齐平;

17.所述场板形成在所述栅极与第二高度的所述氧化层的相接处的上表面。

18.本实用新型的有益技术效果是:

19.本技术公开了一种抗单粒子烧毁的横向功率器件,该横向功率器件在p-阱区内部制作第一空腔可以有效减少漏端电子的收集量,降低漏极缓冲电流;且在n-漏极缓冲区制作第二空腔可以减少源端对空穴的收集量,防止寄生晶体管导通。两个空腔所形成的隔离可以使得单粒子撞击在器件中产生电子-空穴对无法穿过,从而减少器件电极对载流子的收集,降低器件发生单粒子烧毁效应的可能性,优化抗单粒子烧毁性能。

附图说明

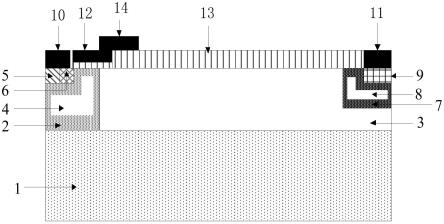

20.图1是本技术的抗单粒子烧毁的横向功率器件的纵向剖面结构示意图。

具体实施方式

21.下面结合附图对本实用新型的具体实施方式做进一步说明。

22.本技术公开了一种抗单粒子烧毁的横向功率器件,请参考图1,该横向功率器件包括衬底1。p-阱区2和n型漂移区3形成在衬底1的上表面。p+源区5和n+源区6形成在p-阱区2的上表面。具体的,如图1所示,p+源区5和n+源区6形成在p-阱区2的远离n型漂移区3的一侧的上表面,p-阱区2的靠近n型漂移区3的一侧的上表面相对于p+源区5和n+源区6外露。

23.n-漏极缓冲区7形成在n型漂移区3的远离p-阱区2的一侧的上表面。n+漏区9形成在n-漏极缓冲区7的上表面。具体的,如图1所示,n+漏区9形成在n-漏极缓冲区7的远离p-阱区2的一侧的上表面,n-漏极缓冲区7的靠近p-阱区2的一侧的上表面相对于n+漏区9外露。

24.p-阱区2、n型漂移区3、p+源区5、n+源区6、n-漏极缓冲区7和n+漏区9的表面还形成有器件顶层,器件顶层包括源极10、漏极11、栅极12、氧化层13和场板14。具体的,p-阱区2相对于p+源区5和n+源区6外露的区域及其相接的部分区域n型漂移区3的上表面形成有第一高度的氧化层13,第一高度的氧化层13覆盖的范围可以自定义设置。n型漂移区3的其余区域的上表面以及n-漏极缓冲区7相对于n+漏区9外露的区域的上表面形成有第二高度的氧化层13。第二高度大于第一高度。p+源区5和n+源区6的上表面形成有第二高度的源极10,且源极10与氧化层13之间形成预定间隔。n+漏区9的上表面形成有第二高度的漏极11。第一高度的氧化层13的上表面形成有栅极12,栅极12的上表面与源极10齐平,因此也与漏极11和第二高度的氧化层13的上表面齐平。场板14形成在栅极12与第二高度的氧化层13的相接处的上表面,场板14覆盖的范围可以自定义设置。

25.p-阱区2内部包含第一空腔4,该第一空腔4完全位于p-阱区2内部而不接触p-阱区2的边界。第一空腔4可以减少源端对空穴的收集量,从而防止寄生晶体管导通,降低器件发生单粒子烧毁效应的可能性。第一空腔4在横向上的长度与p-阱区2在横向上的长度之间的比例达到第一比例阈值,第一比例阈值为预设值,比如70%、75%等等,也即第一空腔4在横

向上有一定长度,且应当尽可能长,从而可以有效降低寄生晶体管导通概率。理论上第一空腔4可以是任意形状的腔体结构,但是考虑到降低加工难度,第一空腔4一般采用规则腔体结构,在一个实施例中,第一空腔4为多边形结构或球形结构或椭球形结构。进一步的,为了便于加工形成,第一空腔4为多边形结构,比如矩形结构。如图1所示,由于p-阱区2的靠近n型漂移区3的一侧的上表面相对于p+源区5和n+源区6外露,因此p-阱区2在纵向剖面上为l型结构,在此情况下,第一空腔4在纵向剖面上也为l型结构,使得源端对空穴的收集量更少,进一步优化抗单粒子烧毁性能。

26.n-漏极缓冲区7内部包含第二空腔8,该第二空腔8完全位于n-漏极缓冲区7内部而不接触n-漏极缓冲区7的边界。第二空腔8可以减少漏端对电子的收集量,从而降低漏极缓冲电流,降低器件发生单粒子烧毁效应的可能性。第二空腔8在横向上的长度与n-漏极缓冲区7在横向上的长度之间的比例达到第二比例阈值,第二比例阈值为预设值,比如70%、75%等等,也即第二空腔8在横向上有一定长度,且应当尽可能长,从而可以有效降低漏极缓冲电流。理论上第二空腔8可以是任意形状的腔体结构,但是考虑到降低加工难度,第二空腔8一般采用规则腔体结构,在一个实施例中,第二空腔8为多边形结构或球形结构或椭球形结构。进一步的,为了便于加工形成,第二空腔8为多边形结构,比如矩形结构。如图1所示,由于n-漏极缓冲区7的靠近p-阱区2的一侧的上表面相对于n+漏区9外露,因此n-漏极缓冲区7在纵向剖面上为l型结构,在此情况下,第二空腔8在纵向剖面上也为l型结构,使得漏端对电子的收集量更少,进一步优化抗单粒子烧毁性能。

27.以上所述的仅是本技术的优选实施方式,本实用新型不限于以上实施例。可以理解,本领域技术人员在不脱离本实用新型的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1