半导体封装支架的制作方法

1.本实用新型涉及半导体封装设备技术领域,尤其涉及半导体封装支架。

背景技术:

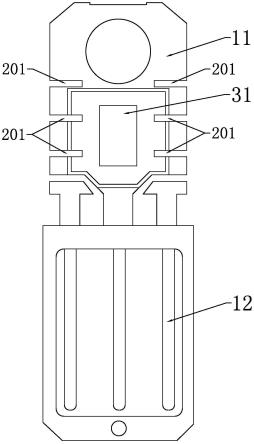

2.如图1所示,封装支架主要包括基岛11和设置在基岛11上的引脚12,是制造集成电路半导体元件的基础部件,为集成电路的芯片提供载体,借助于键合材料实现芯片与外部电路板电信号的连接,同时,为芯片提供热量传导通道,释放热量。

3.然而,在半导体芯片的使用过程中,半导体芯片在应力作用下常常会导致其性能的改变,尤其是薄膜生长的半导体,如gan、gaas、gao等薄膜,在封装过程中,外加应力会直接改变半导体芯片的电性能,更有甚者,会导致芯片性能的失效。

4.如何减少半导体芯片所受到的应力,以确保半导体芯片电性能的稳定性,是目前亟待解决的一项问题。

技术实现要素:

5.本实用新型的一个优势在于提供一种半导体封装支架,其中通过在基岛上设置多条隔离段,比如隔离通孔或者隔离缺口等,能够有效释放半导体封装支架自身所带来的应力,从而防止将封装支架的应力造成的形变传递给半导体芯片,尤其是薄膜类半导体芯片,从而能够有效确保半导体芯片电性能的稳定性,延长半导体芯片的使用寿命,降低使用成本。

6.为达到本实用新型以上至少一个优势,本实用新型提供一种半导体封装支架,包括基岛和设置在所述基岛的同一侧的引脚,其中所述基岛设置有多条隔离段,其中所述隔离段为隔离通孔或隔离缺口。

7.根据本实用新型一实施例,所述隔离段被实施为两个,其中,两个所述隔离段在正对所述引脚的方向的两侧对称分布。

8.根据本实用新型一实施例,所述隔离段被实施为隔离缺口,且所述隔离缺口正对所述引脚。

9.根据本实用新型一实施例,所述隔离段与所述基岛的侧边之间的距离为2mm~6mm,所述隔离段的尺寸为0.2mm~1mm*4mm~10mm。

10.根据本实用新型一实施例,所述隔离段被实施为隔离缺口,且所述隔离缺口背对所述引脚。

11.根据本实用新型一实施例,所述隔离段与所述基岛的侧边之间的距离为1mm~3mm,所述隔离段的尺寸为0.2mm~1mm*10mm~15mm。

12.根据本实用新型一实施例,所述隔离段被实施为至少两条,且至少两条所述隔离段之间并列分布;

13.所述隔离段被实施为隔离缺口,且所述隔离缺口正对所述基岛的侧边。

14.根据本实用新型一实施例,相邻所述隔离段之间的间隔距离为2mm~4mm,所述隔

离段的尺寸为0.2mm~1mm*2mm~6mm。

15.根据本实用新型一实施例,所述隔离段靠近所述基岛用于安装芯片的中部位置。

16.本实用新型的这些和其它目的、特点和优势,通过下述的详细说明,得以充分体现。

附图说明

17.图1示出了现有技术中封装支架的结构示意图。

18.图2示出了本技术一较佳实施例半导体封装支架的结构示意图。

19.图3示出了本技术另一较佳实施例半导体封装支架的结构示意图。

20.图4示出了本技术第三较佳实施例半导体封装支架的结构示意图。

21.附图标记:11-基岛,12-引脚,21-基岛,22-引脚,201-隔离段,31-芯片。

具体实施方式

22.以下描述用于揭露本实用新型以使本领域技术人员能够实现本实用新型。以下描述中的优选实施例只作为举例,本领域技术人员可以想到其他显而易见的变型。在以下描述中界定的本实用新型的基本原理可以应用于其他实施方案、变形方案、改进方案、等同方案以及没有背离本实用新型的精神和范围的其他技术方案。

23.本领域技术人员应理解的是,在说明书的揭露中,术语“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系是基于附图所示的方位或位置关系,其仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此,上述术语不能理解为对本实用新型的限制。

24.可以理解的是,术语“一”应理解为“至少一”或“一个或多个”,即在一个实施例中,一个元件的数量可以为一个,而在另外的实施例中,该元件的数量可以为多个,术语“一”不能理解为对数量的限制。

25.参考图2至图4,依本实用新型一较佳实施例的一种半导体封装支架将在以下被详细地阐述,其中所述半导体封装支架包括基岛21和设置在所述基岛21的同一侧的引脚22,同时,所述基岛21设置有多条隔离段201,其中所述隔离段201为隔离通孔或隔离缺口,以此能够通过所述隔离通孔或隔离缺口释放半导体封装支架自身所带来的应力,从而能够在后期安装半导体芯片31时,防止半导体封装支架将自身的应力传递给半导体芯片31,进而有效确保半导体芯片31电性能的稳定性,尤其是薄膜类半导体芯片,比如使用gan、gaas、gao等薄膜的半导体芯片。

26.优选地,所述隔离段201被实施为两个,其中,两个所述隔离段201在正对所述引脚22的方向的两侧对称分布,从而能够均匀的释放所述半导体封装支架自身的应力,并同时确保所述半导体封装支架的结构稳定性。一般情况下,两个所述隔离段20正对所述基岛21用于安装芯片31的中部位置的两侧对称分布。

27.在一个实施例中,结合图2所示,所述隔离段201被实施为隔离缺口,且所述隔离缺口正对所述引脚22。

28.进一步优选的,所述隔离段201与所述基岛21的侧边之间的距离为2mm~6mm,比如

3mm、3.5mm、4mm或者5mm,其中优选为4mm,该距离尺寸可以根据基岛21的具体尺寸大小进行灵活选择或者设置,此外,所述隔离段201的尺寸,即隔离缺口的尺寸为0.2mm~1mm*4mm~10mm,比如0.3mm*4mm、0.5mm*6mm、0.8mm*8mm或者1mm*10mm等等,其中隔离缺口的尺寸也可以根据实际需要或者基岛21的具体尺寸大小进行灵活选择,以在确保半导体封装支架结构稳定性的同时,还能够充分释放半导体封装支架自身的应力。

29.在另一个实施例中,结合图3所示,所述隔离段201被实施为隔离缺口,且所述隔离缺口背对所述引脚22。

30.进一步优选地,所述隔离段201与所述基岛21的侧边之间的距离为1mm~3mm,比如1mm、1.5mm、2mm或者2.5mm,其中优选为2.5mm,该距离尺寸也可以根据基岛21的具体尺寸大小进行灵活选择或者设置,同时,所述隔离段201的尺寸,即隔离缺口的尺寸为0.2mm~1mm*10mm~15mm,比如0.3mm*12mm、0.5mm*13mm、0.8mm*14mm或者1mm*14mm等等。在该实施例中,与前实施例相比,隔离段201和基岛21的侧边之间的距离,以及隔离缺口的尺寸的设置主要基于基岛21自身的结构,以及隔离段201和基岛21的侧边之间的距离以及隔离缺口的尺寸这两个尺寸数据之间的配合关系进行设置,比如,当隔离缺口为背对引脚,且隔离段201与基岛21的侧边之间的距离较小时,隔离缺口的纵深尺寸相对正对引脚22的情况的纵深尺寸是会大一些的,如10mm~15mm大于4mm~10mm,从而能够充分协调半导体封装支架的结构稳定性和应力释放两者之间的情况。

31.作为第三较佳实施例,结合图4所示,所述隔离段201被实施为至少两条,一般情况下可以是两条或者三条,甚至是四条,且至少两条所述隔离段201之间并列分布;

32.所述隔离段201被实施为隔离缺口,且所述隔离缺口正对所述基岛21的侧边。

33.进一步优选地,相邻所述隔离段201之间的间隔距离为2mm~4mm,比如2.5mm、3mm或者3.5mm,其中优选为3mm,该距离尺寸也可以根据基岛21的具体尺寸大小进行灵活选择,同时,所述隔离段201的尺寸,即隔离缺口的尺寸为0.2mm~1mm*2mm~6mm,比如0.3mm*3mm、0.4mm*3mm、0.6mm*4.5mm、0.8mm*5mm等,其中隔离缺口的尺寸也可以根据实际需要或者基岛21的具体尺寸大小进行灵活选择,以在确保半导体封装支架结构稳定性的同时,还能够充分释放半导体封装支架自身的应力。

34.进一步优选地,所述隔离段201靠近所述基岛21用于安装芯片31的中部位置,以在确保半导体封装支架结构稳定性的同时,尽量释放靠近芯片31位置处的半导体封装支架的应力。

35.本领域的技术人员应理解,上述描述及附图中所示的本实用新型的实施例只作为举例而并不限制本实用新型。本实用新型的优势已经完整并有效地实现。本实用新型的功能及结构原理已在实施例中展示和说明,在没有背离所述原理下,本实用新型的实施方式可以有任何变形或修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1