肖特基二极管元件的制作方法

本技术涉及一种二极管元件,特别是涉及一种肖特基二极管元件。

背景技术:

1、现有技术中,肖特基二极管(schottky diode)是一种导通电压降较低且允许高速切换的二极管,是利用肖特基能障(schottky barrier)特性而产生的电子组件。肖特基二极管的导通电压非常低。一般的二极管在电流流过时,会产生约0.7至1.7伏特的电压降,不过肖特基二极管的电压降只有0.15至0.45伏特,因此可以有效提升系统的效率。

2、再者,肖特基二极管是利用金属-半导体接面作为肖特基能障,以产生整流的效果,其与一般的二极管所采用由半导体-半导体接面产生的p-n接面不同。肖特基能障的特性使得肖特基二极管的导通电压降较低,而且可以提高切换的速度。

3、此外,肖特基二极管与一般的二极管最大的差异在于逆向恢复时间,也就是二极管由流过顺向电流的导通状态,切换到不导通状态所需的时间。对于一般的二极管,其逆向恢复时间大约是几百ns,若是高速二极管则会低于一百ns。然而,肖特基二极管没有逆向恢复时间,因此小信号的肖特基二极管切换的时间约为几十ps,特殊的大容量肖特基二极管切换的时间也才几十ps。一般的二极管在逆向恢复时间内,会因逆向电流而造成emi噪声,然而肖特基二极管可以立即切换,没有逆向恢复时间以及反相电流的问题。

4、另外,肖特基二极管是一种使用多数载流子的半导体组件。若肖特基二极管是使用n型半导体,其二极管的特性是由多数载流子(即电子)所产生。多数载流子快速地由半导体穿过接面,注入另一侧金属的传导带,由于此过程不涉及n型、p型载流子的结合(随机反应而且需要时间较长),因此肖特基二极管停止导通的速度会比传统的二极管速度还要快。这样的特性使得组件所需要的面积可以减少,又进一步的减少切换所需的时间。

5、现有技术中,肖特基二极管最大的缺陷是其逆向偏压较低及逆向漏电流偏大,像使用硅及金属为材料的肖特基二极管,其逆向偏压额定耐压最高只到50v,而逆向漏电流值为正温度特性,容易随着温度升高而急剧变大,实务设计上需注意其热失控的隐忧。同时,在制造肖特基二极管过程中,需要使用多次的光罩制程,不只成本较高、制程繁复而且制造时间也拉长。

技术实现思路

1、本实用新型所欲解决的问题在于,针对现有技术的不足提供一种肖特基二极管元件。

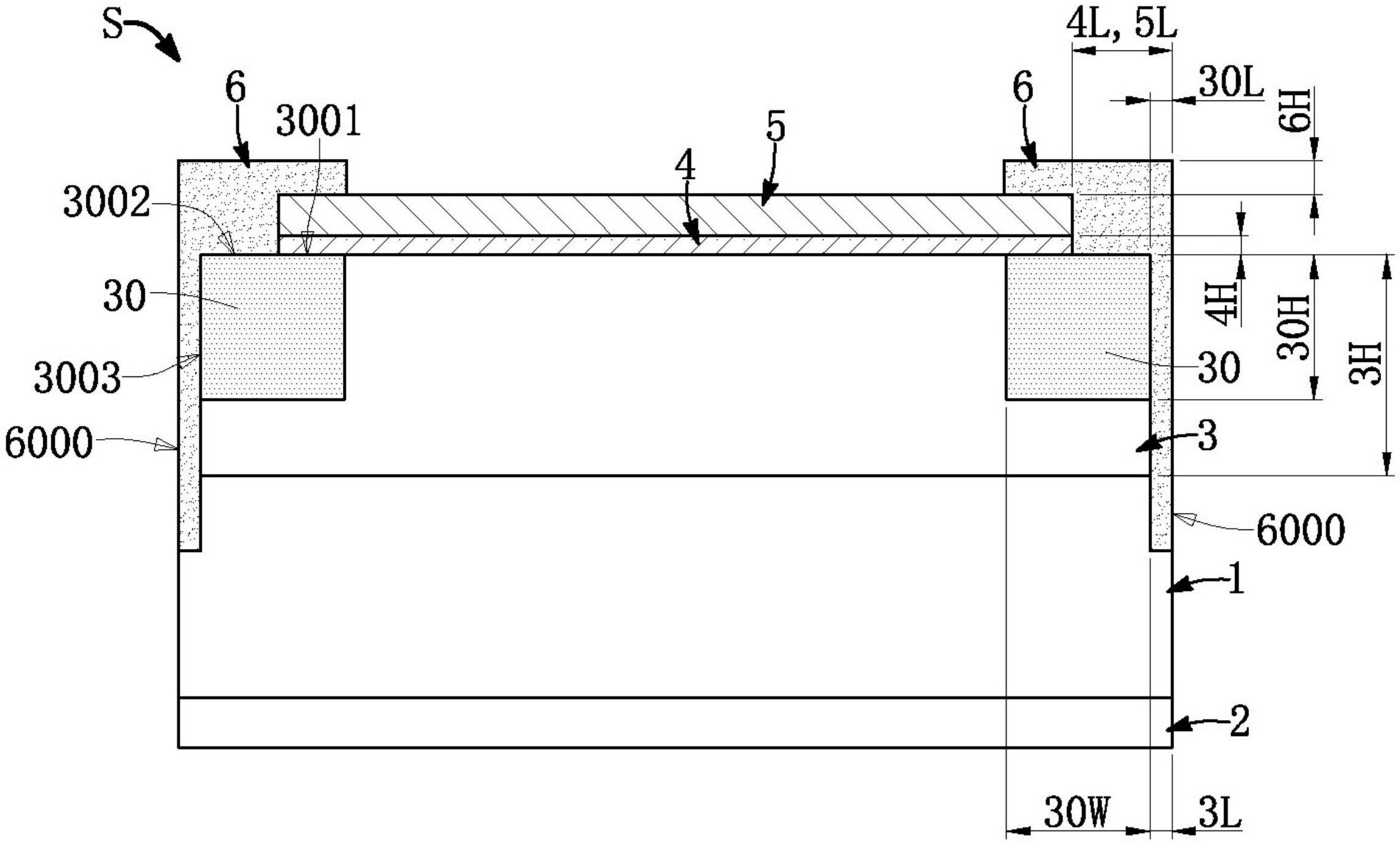

2、为了解决上述的问题,本实用新型所采用的其中一技术手段是提供一种肖特基二极管元件,其包括:一基底、一第一电极层、一磊晶层、一金属硅化物层、一第二电极层以及一介电材料层。所述第一电极层形成在所述基底的底端上。所述磊晶层形成在所述基底的顶端上,其中所述磊晶层具有至少一掺杂区。所述金属硅化物层形成在所述磊晶层上且覆盖所述至少一掺杂区的一部分表面。所述第二电极层形成在所述金属硅化物层上。所述介电材料层从所述基底延伸到所述第二电极层。所述介电材料层覆盖所述至少一掺杂区的另一部分表面且覆盖所述第二电极层的一部分表面。

3、在其中一可行的或者较佳的实施例中,所述基底与所述磊晶层的总厚度实质上介于250至300μm之间,且所述磊晶层的厚度实质上介于3至10μm之间;其中,所述第一电极层为包括有钛层、镍层、银层的一第一多层导电结构,且所述第二电极层为包括有钛层、镍层、银层的一第二多层导电结构;其中,所述金属硅化物层的厚度实质上介于10至90nm之间。

4、在其中一可行的或者较佳的实施例中,所述至少一掺杂区的厚度实质上介于1至3μm之间,且所述至少一掺杂区的宽度实质上介于70至90μm之间;其中,所述至少一掺杂区的一第一部分上表面被所述金属硅化物层所覆盖,且所述至少一掺杂区的一第二部分上表面以及一侧表面被所述介电材料层所覆盖。

5、在其中一可行的或者较佳的实施例中,所述介电材料层为具有聚酰亚胺或者硅胶的一水气阻隔层,且所述介电材料层的顶端相对于所述第二电极层的最小距离实质上介于3至20μm之间。

6、在其中一可行的或者较佳的实施例中,所述介电材料层具有一侧切割面,所述第二电极层相距所述介电材料层的所述侧切割面的最短距离大于5μm,所述金属硅化物层相距所述介电材料层的所述侧切割面的最短距离大于5μm,所述至少一掺杂区相距所述介电材料层的所述侧切割面的最短距离实质上介于5至20μm之间,且所述磊晶层相距所述介电材料层的所述侧切割面的最短距离实质上介于5至20μm之间。

7、在其中一可行的或者较佳的实施例中,所述切割槽的深度实质上介于20至50μm之间,且所述切割槽的宽度实质上介于60至80μm之间。

8、在其中一可行的或者较佳的实施例中,在切割所述初始介电材料层、所述初始基底以及所述初始第一电极层的步骤后,多个肖特基二极管元件被制作完成;其中,每一肖特基二极管元件包括所述基底、所述第一电极层、具有所述掺杂区的所述磊晶层、所述金属硅化物层、所述第二电极层以及所述介电材料层,所述第一电极层形成在所述基底的底端上,所述磊晶层形成在所述基底的顶端上,所述金属硅化物层形成在所述磊晶层上且覆盖所述掺杂区的一部分表面,所述第二电极层形成在所述金属硅化物层上,所述介电材料层从所述基底延伸到所述第二电极层,且所述介电材料层覆盖所述至少一掺杂区的另一部分表面且覆盖所述第二电极层的一部分表面。

9、本实用新型的其中一有益效果在于,本实用新型所提供的肖特基二极管元件,其能通过“所述金属硅化物层形成在所述磊晶层上且覆盖所述至少一掺杂区的一部分表面”以及“所述介电材料层覆盖所述至少一掺杂区的另一部分表面且覆盖所述第二电极层的一部分表面”的技术方案,以使得金属硅化物层能够相距所述介电材料层的所述侧切割面一预定距离,藉此以避免产生漏电的问题。

10、为使能进一步了解本实用新型的特征及技术内容,请参阅以下有关本实用新型的详细说明与附图,然而所提供的附图仅用于提供参考与说明,并非用来对本实用新型加以限制。

技术特征:

1.一种肖特基二极管元件,其特征在于,所述肖特基二极管元件包括:

2.根据权利要求1所述的肖特基二极管元件,其特征在于,所述基底与所述磊晶层的总厚度实质上介于250至300μm之间,且所述磊晶层的厚度实质上介于3至10μm之间;其中,所述第一电极层为包括有钛层、镍层、银层的一第一多层导电结构,且所述第二电极层为包括有钛层、镍层、银层的一第二多层导电结构;其中,所述金属硅化物层的厚度实质上介于10至90nm之间。

3.根据权利要求1所述的肖特基二极管元件,其特征在于,所述至少一掺杂区的厚度实质上介于1至3μm之间,且所述至少一掺杂区的宽度实质上介于70至90μm之间;其中,所述至少一掺杂区的一第一部分上表面被所述金属硅化物层所覆盖,且所述至少一掺杂区的一第二部分上表面以及一侧表面被所述介电材料层所覆盖。

4.根据权利要求1所述的肖特基二极管元件,其特征在于,所述介电材料层为具有聚酰亚胺或者硅胶的一水气阻隔层,且所述介电材料层的顶端相对于所述第二电极层的最小距离实质上介于3至20μm之间。

5.根据权利要求1所述的肖特基二极管元件,其特征在于,所述介电材料层具有一侧切割面,所述第二电极层相距所述介电材料层的所述侧切割面的最短距离大于5μm,所述金属硅化物层相距所述介电材料层的所述侧切割面的最短距离大于5μm,所述至少一掺杂区相距所述介电材料层的所述侧切割面的最短距离实质上介于5至20μm之间,且所述磊晶层相距所述介电材料层的所述侧切割面的最短距离实质上介于5至20μm之间。

技术总结

本技术提供一种肖特基二极管元件。肖特基二极管元件包括一基底、一第一电极层、一磊晶层、一金属硅化物层、一第二电极层以及一介电材料层。第一电极层形成在基底的底端上。磊晶层形成在基底的顶端上,其中磊晶层具有至少一掺杂区。金属硅化物层形成在磊晶层上且覆盖至少一掺杂区的一部分表面。第二电极层形成在金属硅化物层上。介电材料层从基底延伸到第二电极层。介电材料层覆盖至少一掺杂区的另一部分表面且覆盖第二电极层的一部分表面。藉此,以使得金属硅化物层能够相距介电材料层的侧切割面一预定距离,藉此以避免产生漏电的问题。

技术研发人员:袁禧霙,侯竣元,王惠东,张峻玮

受保护的技术使用者:芯沣科技有限公司

技术研发日:20221208

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!