发射辐射的半导体芯片和制造发射辐射的半导体芯片的方法与流程

提出一种发射辐射的半导体芯片和一种用于制造发射辐射的半导体芯片的方法。

背景技术:

技术实现思路

1、要实现的目的在于,提出一种发射辐射的半导体芯片,所述半导体芯片可以特别高效地运行。另一要实现的目的在于,提出一种用于制造这种发射辐射的半导体芯片的方法。

2、发射辐射的半导体芯片例如是发光二极管芯片,所述发光二极管芯片在运行中放射红外光、任意色温的彩色的或白色的光。

3、根据发射辐射的半导体芯片的至少一个实施方式,发射辐射的半导体芯片包括第一掺杂区域。第一掺杂区域借助掺杂的半导体材料形成。例如,第一掺杂区域的半导体材料以及跟随的区域的半导体材料分别是iii-v族化合物半导体材料。总的来说,发射辐射的半导体芯片可以是基于iii-v族化合物半导体材料的半导体芯片。

4、iii-v族化合物半导体材料具有至少一种选自第三主族的元素,例如b、al、ga、in,和选自第五主族的元素,例如n、p、as。尤其,术语“iii-v族化合物半导体材料”包括二元、三元或四元化合物的组,所述化合物包含至少一种出自第三主族的元素和至少一种出自第五主族的元素,例如氮化物化合物半导体和磷化物化合物半导体。这样的二元、三元或四元化合物此外例如可以具有一种或多种掺杂材料以及附加的组成部分。

5、例如,半导体芯片基于材料体系ingaalp或材料体系ingaalas或材料体系ingaaln。

6、第一掺杂区域例如可以是p型掺杂区域和n型掺杂区域。

7、根据发射辐射的半导体芯片的至少一个实施方式,半导体芯片包括有源区域,所述有源区域设为用于产生电磁辐射,尤其光,并且所述有源区域邻接于第一掺杂区域。在发射辐射的半导体芯片的有源区域中,产生电磁辐射,所述电磁辐射由发射辐射的半导体芯片在运行中发射。

8、有源区域对此例如包括多量子系统结构、单量子系统结构或异质结构,例如双异质结构或p-n结。名称量子系统结构在此不展现出关于量子化的维度的意义。因此,量子系统结构尤其包括量子阱、量子线和量子点和这些结构的任意组合。

9、有源区域例如直接邻接于第一掺杂区域。

10、根据发射辐射的半导体芯片的至少一个实施方式,发射辐射的半导体芯片包括第二掺杂区域,所述第二掺杂区域设置在有源区域的背离第一掺杂区域的侧上。第二掺杂区域与第一掺杂区域不同名地掺杂。也就是说,如果第一掺杂区域例如是p型掺杂的,那么第二掺杂区域是n型掺杂的。如果第一掺杂区域例如是n型掺杂的,那么第二掺杂区域是p型掺杂的。

11、根据发射辐射的半导体芯片的至少一个实施方式,第一掺杂区域是结构化的。也就是说尤其地,第一掺杂区域在其形状方面在制造发射辐射的半导体芯片期间通过结构化方法改变。第一掺杂区域于是尤其不是平面的层,所述平面的层在制造公差的范围内主要沿两个空间维度延伸,而且第一掺杂区域可以是三维结构。第一掺杂区域于是尤其具有不平坦的、例如弯曲地伸展的外面。

12、在垂直于半导体芯片的主延伸平面伸展的剖平面中,第一掺杂区域例如可以具有梯形的形状。于是,第一掺杂区域的三维形状在制造公差的范围内可以对应地是棱柱。此外可行的是,第一掺杂区域的三维形状类似于或对应于阶梯棱锥、半球或半柱。

13、根据发射辐射的半导体芯片的至少一个实施方式,有源区域在侧面处和在覆盖面处覆盖第一掺杂区域。也就是说,有源区域不仅作为主要沿两个空间维度延伸的层设置在第一掺杂区域的覆盖面处,而且有源区域至少局部保形地跟随第一掺杂区域,使得第一掺杂区域也在侧面处由有源区域的材料覆盖。

14、在此可行的是,有源区域连续地从第一掺杂区域的侧面延伸至第一掺杂区域的覆盖面。此外可行的是,有源区域不连通地构成并且仅局部地在侧面处和在覆盖面上覆盖第一掺杂区域。

15、第一掺杂区域的覆盖面例如是第一掺杂区域的平行于光电子半导体芯片的主延伸平面伸展的外面。例如,覆盖面在制造公差的范围内平行于衬底的主延伸平面伸展,在所述衬底上制造发射辐射的半导体芯片。

16、第一掺杂区域的侧面在此横向于发射辐射的半导体芯片的主延伸平面伸展。第一掺杂区域在此可以具有两个或更多个这种侧面。侧面可以将第一掺杂区域的覆盖面与第一掺杂区域的背离覆盖面的底面连接。第一掺杂区域的底面例如与衬底或与承载件直接接触,在所述衬底上生长第一掺杂区域,在所述承载件上施加第一掺杂区域。

17、根据发射辐射的半导体芯片的至少一个实施方式,半导体芯片包括第一掺杂区域、有源区域和第二掺杂区域,所述有源区域设为用于产生电磁辐射并且所述有源区域邻接于第一掺杂区域,所述第二掺杂区域设置在有源区域的背离第一掺杂区域的侧上。在此,第一掺杂区域是结构化的并且有源区域在侧面处和在覆盖面处覆盖第一掺杂区域。

18、在此所描述的发射辐射的半导体芯片在此尤其基于以下考量:发射辐射的半导体芯片的效率通常通过小的辐射耦合输出效率和由于不进行辐射的复合被不利地影响。

19、小的辐射耦合输出效率可以归因于全内反射,所述全内反射尤其会在具有平面的光出射面的发射辐射的半导体芯片中出现。这于是也会造成,在发射辐射的半导体芯片中产生的电磁辐射仅能在窄的角度范围内从半导体芯片中射出。

20、现在,在此所描述的发射辐射的半导体芯片尤其基于以下构思:将有源区域设置在结构化的第一掺杂区域下游,使得有源区域除了第一掺杂区域的覆盖面之外也设置在侧面处。以这种方式,产生特别多的电磁辐射,所述电磁辐射的主放射方向垂直于或近似垂直于发射辐射的半导体芯片的辐射耦合输出面伸展,由此减少了在发射辐射的半导体芯片中出现全反射的概率。

21、此外,由此增大由半导体芯片放射电磁辐射的角度范围。在理想情况下,有源区域在其伸展中曲折地并且例如局部地在垂直于光电子半导体芯片的主延伸平面的剖平面中是圆形的。相同内容那么优选地也适用于半导体芯片的辐射耦合输出面。

22、根据发射辐射的半导体芯片的至少一个实施方式,有源区域完全地覆盖第一掺杂区域的侧面。

23、在此情况下,第一掺杂区域的侧面例如可以在制造公差的范围内平面地构成并且有源区域施加在第一掺杂区域的所述平面的侧面上。有源区域于是例如可以连续地从第一掺杂区域的第一侧面延伸至覆盖面。例如,在此可行的是,第一掺杂区域具有至少两个、例如或四个这种侧面。

24、根据发射辐射的半导体芯片的至少一个实施方式,半导体芯片具有主延伸平面并且有源区域局部地倾斜于主延伸平面伸展。例如,半导体芯片的主延伸平面平行于衬底的覆盖面伸展,在所述衬底上产生半导体芯片。

25、主延伸平面例如倾斜于或垂直于生长方向伸展,发射辐射的半导体芯片的区域以所述生长方向外延地生长。

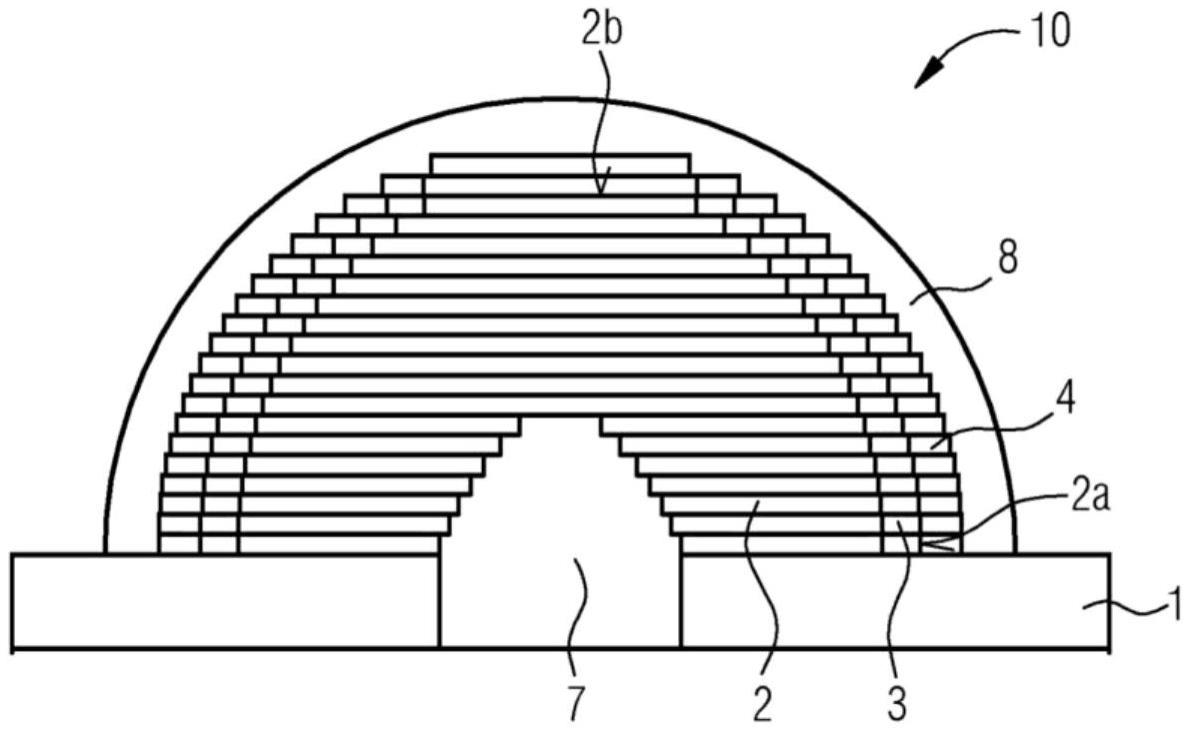

26、有源区域在此可以局部地倾斜于半导体芯片的主延伸平面并且局部地平行于主延伸平面设置在第一掺杂区域上。例如,有源区域在其施加到第一掺杂区域的侧面上的位置处倾斜于主延伸平面伸展并且在其施加到第一掺杂区域的覆盖面上的位置处平行于主延伸平面伸展。

27、根据发射辐射的半导体芯片的至少一个实施方式,有源区域弯曲地伸展。也就是说,在本实施方式中,有源区域可以至少近似地具有弯曲部并且例如跟随球表面的伸展。如果第一掺杂区域具有对应地结构化的外面,那么是这种情况。

28、例如,有源区域可以局部地朝衬底的方向弯曲。有源区域可以与衬底直接接触。例如,有源区域仅局部地与衬底直接接触。尤其,有源区域可以与衬底的电绝缘区域直接接触。

29、根据发射辐射的半导体芯片的至少一个实施方式,第一掺杂区域阶梯式地结构化并且沿垂直于半导体芯片的主延伸平面的方向具有多个平面。也就是说,第一掺杂区域例如可以近似于阶梯棱锥。有源区域于是可以不仅位于第一掺杂区域的横向于或垂直于半导体芯片的主延伸平面伸展的侧面处、而且位于第一掺杂区域的平行于半导体芯片的主延伸平面伸展的面处。

30、根据发射辐射的半导体芯片的至少一个实施方式,第一掺杂区域沿垂直于半导体芯片的主延伸平面的方向渐尖。也就是说,沿垂直于主延伸平面的方向,第一掺杂区域的平行于主延伸平面伸展的横截面的面积减小。

31、根据发射辐射的半导体芯片的至少一个实施方式,发射辐射的半导体芯片包括第一接触部,所述第一接触部导电地与第一掺杂区域连接,其中第一接触部延伸进入到第一传导区域中。

32、第一接触部例如可以借助导电材料、尤其金属材料或透明导电氧化物形成。第一接触部尤其可以在第一掺杂区域的几何中心的区域中延伸到所述第一掺杂区域中。第一接触部在此同样可以构成为,使得其沿垂直于半导体芯片的主延伸平面的方向渐尖。借助这种第一接触部可行的是,特别均匀地接触发射辐射的半导体芯片。

33、根据发射辐射的半导体芯片的至少一个实施方式,半导体芯片是微型发光二极管芯片。发射辐射的半导体芯片于是具有小于或等于20μm的棱边长度。棱边长度于是例如为发射辐射的半导体芯片的具有最小横向延伸的棱边。沿另一方向,发射辐射的半导体芯片于是可以具有大于20μm的棱边长度。

34、根据发射辐射的半导体芯片的至少一个实施方式,半导体芯片具有不平坦的、尤其弯曲地伸展的辐射耦合输出面,在运行中产生的辐射可以通过所述辐射耦合输出面离开半导体芯片。辐射耦合输出面可以通过半导体芯片的外面形成。

35、半导体芯片于是优选地还具有不平坦的、尤其弯曲地伸展的有源区域。有源区域在此可以具有朝向辐射耦合输出面的外面,所述外面类似于或平行于辐射耦合输出面伸展。

36、如果辐射耦合输出面和有源区域是不平坦的,则半导体芯片的电磁辐射优选地可以在有源区域的每个部位处在大的角度范围内发射。

37、此外提出一种用于制造发射辐射的半导体芯片的方法。借助所述方法尤其可以制造在此所描述的发射辐射的半导体芯片。也就是说,所有对于发射辐射的半导体芯片所公开的特征也对于所述方法公开并且反之亦然。

38、在所述方法中,首先提供衬底。所述衬底例如可以是生长衬底,所述生长衬底根据沉积到衬底上的半导体芯片的材料例如可以借助蓝宝石、sic、gaas、si、inp等形成。衬底具有主延伸平面,所述主延伸平面例如平行于衬底的覆盖面伸展,后续的层沉积到所述覆盖面上。在此和在下文中,衬底还可以是生长衬底和/或是外延生长的层,所述层生长到生长衬底上。随后也可以移除生长衬底。

39、衬底可以至少局部电绝缘地构成。换言之,衬底至少局部地具有不导电的区域。例如,衬底电绝缘地构成。

40、根据所述方法的至少一个实施方式,所述方法包括如下方法步骤,在所述方法步骤中沉积第一掺杂区域。第一掺杂区域的沉积例如外延地进行。

41、在此可行的是,第一掺杂区域直接沉积到衬底上,或在衬底和第一掺杂区域之间存在缓冲层。第一掺杂区域例如借助n型掺杂的或p型掺杂的半导体材料形成。

42、根据至少一个实施方式,所述方法包括以下步骤,在所述步骤中进行第一掺杂区域的结构化,使得第一掺杂区域沿背离衬底的方向渐尖。

43、第一掺杂区域的结构化在此例如可以通过材料去除、例如蚀刻进行。此外可行的是,利用掩膜来生长第一掺杂区域。在此可行的是,为了将第一掺杂区域结构化随后使用掩膜,所述掩膜具有彼此不同的掩膜开口,第一有源区域的材料沉积在所述掩膜开口中。例如,于是在第一有源区域生长时可以逐渐减小掩膜开口的尺寸,由此同样实现第一掺杂区域沿背离衬底的方向的渐尖。

44、根据方法的至少一个实施方式,进行有源区域的沉积,使得有源区域覆盖第一掺杂区域的侧面。有源区域于是在制成的半导体芯片中与第一掺杂区域的侧面尤其直接接触。

45、根据至少一个实施方式,所述方法包括以下方法步骤,在所述方法步骤中,进行第二掺杂区域在有源区域上的沉积。第二掺杂区域与第一掺杂区域不同名地掺杂。有源区域和第二掺杂区域可以彼此直接接触。有源区域的沉积尤其同样外延地进行并且可以在与第一掺杂区域的沉积相同的外延设施中进行。

46、第二掺杂区域的沉积同样外延地进行并且可以在与有源区域的沉积相同的外延设施中进行。

47、根据所述方法的至少一个实施方式,所述方法包括以下方法步骤:

48、-提供衬底,

49、-沉积第一掺杂区域,

50、-将第一掺杂区域结构化成,使得第一掺杂区域沿背离衬底的方向渐尖,

51、-沉积有源区域,使得有源区域覆盖第一掺杂区域的侧面,

52、-在有源区域上沉积第二掺杂区域。

53、在此尤其可行的是,方法步骤以与所给出的顺序不同的顺序执行。例如,可以在沉积掺杂区域中的一个掺杂区域之前进行有源区域的沉积。

54、根据所述方法的至少一个实施方式,多次进行第一区域的结构化,使得第一区域阶梯式地结构化并且沿着背离衬底的方向具有多个平面。结构化在此例如可以通过对应地蚀刻第一区域进行或通过在第一区域生长期间借助于掩膜的结构化进行。

55、根据所述方法的至少一个实施方式,在首次沉积第一掺杂区域和第二掺杂区域之前沉积有源区域的一部分。换言之,在方法的该实施方式中,在产生掺杂区域中的一个掺杂区域之前,沉积有源区域的至少一部分。

56、根据所述方法的至少一个实施方式,在沉积第一掺杂区域和第二掺杂区域之前,将有源区域局部地移除。例如,将有源区域大面积地沉积在衬底上。接着,将有源区域局部地移除并且将第一掺杂区域和/或第二掺杂区域的材料沉积到有源区域的这样制造的开口中。

- 还没有人留言评论。精彩留言会获得点赞!