具有降低的碳空穴浓度的半导体器件及其制造方法与流程

本公开涉及包括由包含碳的第一半导体材料,特别地由碳化硅制成的至少一个外延层的半导体器件,其中相对于原生的至少一个外延层的第一半导体材料,外延层的至少一部分具有降低的碳空穴浓度。本公开还涉及用于制造这种半导体器件的方法。

背景技术:

1、us 7 754 589 b2涉及一种用于通过有效地减少或消除原生sic晶体中的载流子俘获中心来提高sic层的质量的方法。

技术实现思路

1、本公开的实施例涉及改进的半导体器件以及用于其制造方法。示例性地,需要具有提高的寿命、低缺陷密度和/或可以使用常规半导体处理步骤以灵活的方式制造的半导体器件。

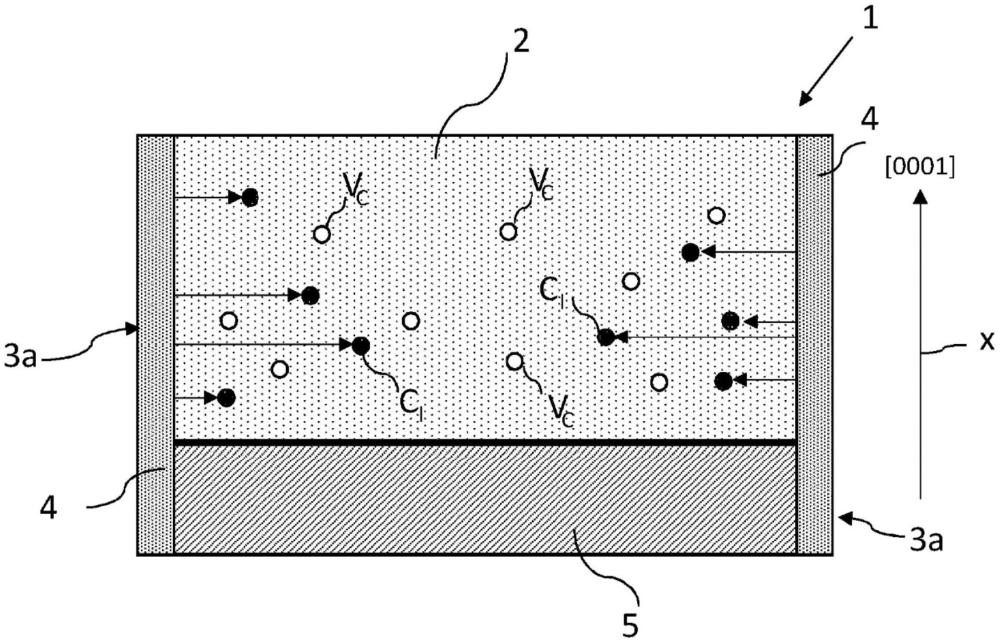

2、根据第一方面,提供了一种半导体器件,该半导体器件包括至少一个外延层,该至少一个外延层由包含碳的第一半导体材料,特别地由碳化硅制成并且具有[0001]晶轴。在外延层的侧壁处形成至少一个注入区,侧壁的法线方向与[0001]晶轴垂直。相对于原生的至少一个外延层的第一半导体材料,外延层的至少一部分具有降低的碳空穴浓度。

3、通过在外延层的侧壁处提供注入区,可以独立于其它处理步骤执行注入,这些步骤通常平行于[0001]晶轴进行,例如在外延层的前面上或穿过外延层的正面进行。同时,改善了注入物质的迁移率,这简化了至少一个外延层的后续退火并导致其中的降低的碳空穴浓度。

4、根据至少一个实施例,至少一个注入区形成在包括至少一个外延层的至少一个半导体芯片的多个侧壁中的一个上。通过半导体芯片的侧壁注入物质允许减少已经分离的、基本上成品的半导体电路部件上的碳空穴。

5、根据至少一个实施例,半导体器件包括至少一个沟槽,该至少一个沟槽具有形成在至少一个外延层中的两个侧壁。至少一个注入区形成在至少一个沟槽的两个侧壁中的至少一个侧壁上。外延层的至少一部分对应于在与[0001]晶轴垂直的平面中延伸的子层,其中子层的厚度对应于或超过至少一个沟槽的深度。沟槽的使用允许在具有相对较大空间范围的外延层的竖直侧壁上注入物质。

6、在至少一个实施例中,半导体器件还包括至少一个电极,该至少一个电极形成在至少一个外延层的顶表面或底表面上,从而形成电活性区,其中至少一个注入区形成在电活性区的外部。例如,至少一个注入区可以被形成为在空间上在半导体器件的电活性区附近。这种空间布置允许减少电活性区中的碳空穴,而不干扰实施半导体器件的功能的电活性区内的任何元件。

7、例如,第一半导体材料可以包括n型4h-sic或n型6h-sic半导体材料中的一种。例如,至少一个注入区可以包括包含碳离子、铝离子和硅离子中的至少一种的注入物质。例如,至少一个注入区可以包括包含非晶硅的注入缺陷区。例如,外延层的至少一部分可以具有低于1010/cm3的碳空穴浓度z1/2。

8、根据不同的实施例,半导体器件可以包括不同的功率电子部件,诸如pin二极管、bjt、igbt或jbs二极管。

9、根据本公开的第二方面,提供了一种用于制造半导体器件的方法。该方法包括:生长至少一个由外延层,该至少一个外延层由包含碳的第一半导体材料(特别是碳化硅)制成并且具有[0001]晶轴;以及通过至少一个外延层的至少一个侧壁注入离子,以在与[0001]晶轴垂直的平面中形成至少一个注入区,从而相对于原生的至少一个外延层,降低第一半导体材料中的碳空穴浓度。

10、上述步骤使得能够制造根据第一方面的半导体器件。它们实现了制造期间的改进的灵活性程度。特别地,注入离子的步骤可以在对至少一个外延层的碳空穴产生负面影响的其他步骤已经完成之后,在制造工艺接近结束时执行。

11、根据至少一个实施例,该方法还包括对至少一个外延层中的至少一个外延层进行退火或质子辐照,以在注入离子之后相对于至少一个外延层进一步降低第一半导体材料中的碳空穴浓度。退火或质子辐照有助于使所生成的碳填隙物扩散。

12、根据至少一个实施例,在通过至少一个侧壁注入离子之前,该方法还包括:执行多个处理步骤以形成包括至少一个外延层的至少一部分的至少一个半导体电路部件;以及分离至少一个半导体电路部件以获得半导体芯片,该半导体芯片具有与[0001]晶轴垂直的顶表面和与顶表面垂直的多个侧壁。通过半导体芯片的侧壁注入离子使得能够减少分离的、基本成品的半导体元件中的碳空穴。

13、根据另一实施例,该方法还包括在至少一个外延层内形成具有两个侧壁的至少一个沟槽,其中通过至少一个侧壁注入离子包括通过至少一个外延层的两个侧壁等离子体浸没离子注入(piii)硼(b)离子、碳(c)离子、铝(al)离子、锗(ge)离子、氮(n)离子、磷(p)离子、砷(as)离子、氧(o)离子、硫(s)离子、氢(h)离子、氩(ar)离子或硅(si)离子中的至少一种。

14、本发明的另外方面、实施例和优点在以下实施例的详细描述以及所附的权利要求组中公开。

15、根据以上描述的第二方面的用于制造半导体器件的方法特别适合于制造根据第一方面的半导体器件。因此,结合半导体器件描述的特征和优点可以用在制造方法中,反之亦然。

16、因此,相对于各方面中的一个描述的每个特征在本文中也相对于另一方面公开,即使在特定方面的上下文中没有明确提及相应的特征。

技术特征:

1.一种半导体器件(1),包括:

2.根据权利要求1所述的半导体器件(1),包括至少一个半导体芯片,所述至少一个半导体芯片包括所述至少一个外延层(2),其中所述至少一个注入区(4)形成在所述至少一个半导体芯片的多个侧壁(3a)中的至少一个侧壁上。

3.根据权利要求1所述的半导体器件(1),包括至少一个沟槽(3),所述至少一个沟槽具有形成在所述至少一个外延层(2)中的两个侧壁(3a),其中

4.根据权利要求1至3中任一项所述的半导体器件(1),还包括:

5.根据权利要求1至4中任一项所述的半导体器件(1),其中所述碳化硅半导体材料包括n型4h-sic或n型6h-sic半导体材料中的至少一种。

6.根据权利要求1至5中任一项所述的半导体器件(1),其中所述至少一个注入区(4)包括注入缺陷区,所述注入缺陷区包括非晶硅。

7.根据权利要求1至6中任一项所述的半导体器件(1),其中所述外延层(2)的所述至少一部分具有超过1012/cm3的深峰值能级浓度,特别是具有超过1012/cm3的on1或on2浓度。

8.根据权利要求1至7中任一项所述的半导体器件(1),其中所述半导体器件(1)包括以下至少之一:

9.一种用于制造半导体器件(1)的方法,包括:

10.根据权利要求9所述的方法,还包括以下至少之一:

11.根据权利要求9或10所述的方法,在通过至少一个侧壁(3a)注入离子之前,所述方法还包括:

12.根据权利要求11所述的方法,包括:

13.根据权利要求11或12所述的方法,其中

14.根据权利要求9或10所述的方法,还包括:

15.根据权利要求14所述的方法,还包括:

16.根据权利要求14所述的方法,还包括:

17.根据权利要求9至16中任一项所述的方法,在通过所述至少一个侧壁(3a)注入离子之前,所述方法还包括:

技术总结

本公开涉及一种半导体器件(1),该半导体器件包括至少一个外延层(2),该至少一个外延层由包含碳的第一半导体材料制成并具有[0001]晶轴。在外延层(2)的侧壁(3a)处形成至少一个注入区(4),其中侧壁(3a)的法线方向与[0001]晶轴垂直。相对于原生的至少一个外延层(2)的第一半导体材料,外延层(2)的至少一部分具有降低的碳空穴(V<subgt;C</subgt;)浓度。本公开还涉及一种用于制造半导体器件(1)的方法,其中通过至少一个外延层(2)的至少一个侧壁(3a)注入离子。

技术研发人员:G·阿尔菲里,L·诺尔

受保护的技术使用者:日立能源有限公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!