用于多电压轨薄栅输出驱动器的静电放电电路的制作方法

本公开一般涉及用于集成电路的接口电路,并且更具体地,涉及可增强接口电路中多电压轨的静电放电保护的电路。

背景技术:

1、电子器件技术在过去几年中已经出现爆炸式增长。例如,更好的通信、硬件、更大的网络和更可靠的协议推动了蜂窝和无线通信技术的发展。无线服务提供商现在能够为他们的客户提供一系列不断扩展的特征和服务,并为用户提供前所未有的访问信息、资源和通信的水平。为了跟上这些服务增强的步伐,移动电子器件(例如,蜂窝电话、平板、膝上型计算机等)变得比以往任何时候都更强大和更复杂。持续的服务增强需要工艺技术进步,这些工艺技术进步可为集成电路(ic)器件提供不断提高的性能和晶体管密度。

2、工艺技术进步趋于减小晶体管栅极长度和ic器件的其它特征尺寸。栅极长度和特征尺寸的减小可增加ic器件对静电放电(esd)事件的敏感性。ic器件通常包括esd保护电路,该esd保护电路可在不同类型的esd事件期间保护接口电路。可测试ic器件,以确保其满足关于esd保护的最低工业标准。ic器件鉴定过程可包括基于人体模型(hbm)或基于esd事件的带电器件模型(cdm)表征来测试ic器件对esd事件的敏感性。一些esd保护电路基于hbm或cdm,或者使用hbm或cdm来评估。hbm旨在表征器件对由人类触摸电子器件导致的±1kv的esd事件所引起损坏的敏感性。cdm旨在表征器件对±250v的esd事件所引起损坏的敏感性,该esd事件与通过直接接触充电或场感应充电突然释放ic芯片或封装件中积累的能量有关。

3、在大规模ic设计和半导体制造工艺的某些方面的变化(包括减小工艺最小特征尺寸)可能会造成ic器件对esd事件的新的或不同的敏感性。因此,需要不断改进ic接口电路的esd保护。

技术实现思路

1、本公开的某些方面涉及可在某些ic器件(包括采用多个电压域的ic器件)中提供增强型esd保护电路的系统、设备、方法和技术。本文所公开的一些示例适用于ic中的接口电路,包括高速低功耗同步动态随机存取存储器中的接口电路。本文所公开的一些示例适用于保护电路,这些电路位于用于实施ic器件的某些核心特征的低电压域与用于器件输入和输出(输入/输出或i/o)的高电压域之间的边界处。

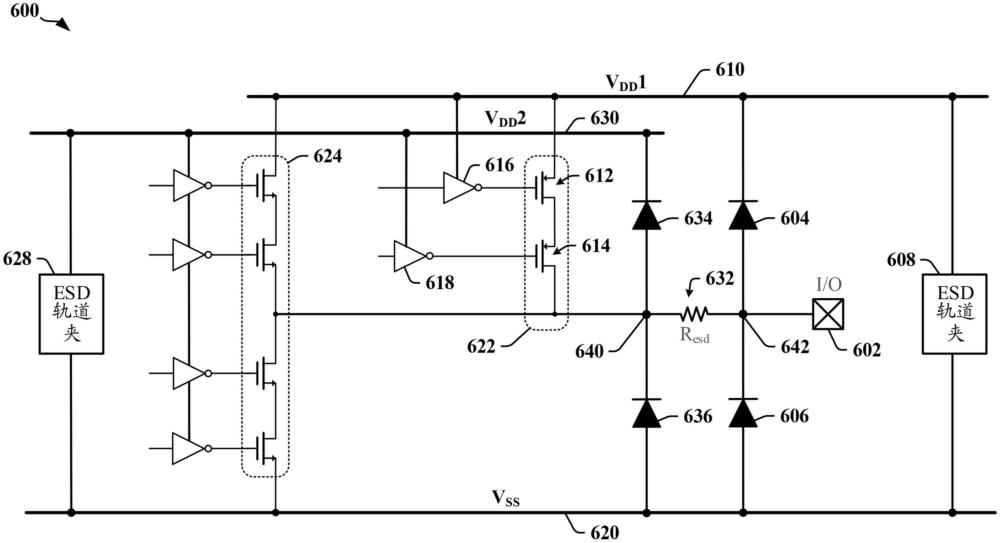

2、在本公开的一个方面,接口电路中的esd保护电路具有:第一二极管,该第一二极管耦合在ic器件的第一电源与该ic器件的i/o焊盘之间;第二二极管,该第二二极管耦合在该ic器件的第二电源与该i/o焊盘之间;和电阻元件,该电阻元件将该第二二极管耦合到该第一二极管和该i/o焊盘。该电源可为驱动电路供电,该驱动电路耦合到该i/o焊盘。该第二电源可为该ic器件的一个或多个核心电路供电。

3、在本公开的一个方面,一种设备具有:用于驱动ic器件的i/o焊盘的装置;用于分流esd电流的第一部分的装置,该esd电流通过该i/o焊盘传导,该装置包括接口电路中的第一二极管,该第一二极管耦合在该ic器件的第一电源与该i/o焊盘之间;和用于分流该esd电流的第二部分的装置,该装置包括该接口电路中的第二二极管,该第二二极管耦合在该集成电路器件的第二电源与该i/o焊盘之间。该第一电源可为用于驱动该i/o焊盘的该装置供电。该第二电源可为该ic器件的一个或多个核心电路供电。该第二二极管的端子可通过电阻元件耦合到该i/o焊盘,该电阻元件耦合到该第一二极管的对应端子。

4、在本公开的一个方面,一种用于提供esd保护的方法包括:将第一二极管耦合在ic器件的第一电源与该ic器件的i/o焊盘之间,该第一二极管被配置为分流esd电流的第一部分,该esd电流通过该i/o焊盘传导;将第二二极管耦合在该ic器件的第二电源与该i/o焊盘之间,该第二二极管被配置为分流该esd电流的第二部分;以及通过电阻元件将该第二二极管耦合到该第一二极管,其中该第二二极管通过该电阻元件耦合到该i/o焊盘。该第一电源可为驱动电路供电,该驱动电路耦合到该i/o焊盘。该第二电源可为该ic器件的一个或多个核心电路供电。

5、在某些示例中,该电阻元件包括互连器,该互连器将该第二二极管的端子耦合到该第一二极管的端子并且具有电阻,在esd事件期间,该电阻在该第二二极管的该端子与该第一二极管的该对应端子之间产生电压差。该电阻元件可包括寄生电阻。

6、在某些示例中,该驱动电路被配置为从该一个或多个核心电路接收控制输入。在一个示例中,该驱动电路可包括晶体管,该晶体管具有栅极,该栅极耦合到预驱动电路的输出端,该预驱动电路从该第二电源接收电力。该晶体管的漏极可耦合到该i/o焊盘。

7、在一个示例中,在esd事件期间,该esd电流通过该i/o焊盘进入该集成电路器件。在该esd电流进入该集成电路器件之前,该第一二极管和该第二二极管可被反向偏置。

8、在一个示例中,该驱动电路的运行电压电平大于该一个或多个核心电路的运行电压电平。

9、在一个示例中,第一箝位电路耦合在该第一电源与该ic器件的接地参考之间,并且第二箝位电路耦合在该第二电源与该接地参考之间。该第一箝位电路可被配置为限制该第一电源与该接地参考之间的电压差的变化。该第二箝位电路可被配置为限制该第二电源与该接地参考之间的电压差的变化。在一个示例中,该接口电路包括低功耗双倍数率同步动态随机存取存储器(lpddr sdram)接口电路。

10、在某些示例中,该驱动电路具有两个pmos上拉晶体管,该两个pmos上拉晶体管串联耦合在该第一电源与该i/o焊盘之间。在一些示例中,该驱动电路具有多个串联耦合的nmos晶体管,该多个串联耦合的nmos晶体管耦合到该i/o焊盘。

11、在一些示例中,该第一二极管通过第三二极管耦合到该ic器件的接地参考。该第三二极管具有第一端子和第二端子,该第一端子耦合到该接地参考,该第二端子耦合到该i/o焊盘。该第二二极管可通过第四二极管耦合到该接地参考。该第四二极管可具有第一端子和第二端子,该第一端子耦合到该接地参考,该第二端子通过电阻元件耦合到该i/o焊盘,该电阻元件耦合到该第三二极管的对应端子。

技术特征:

1.一种接口电路中的静电放电保护电路,所述静电放电保护电路包括:

2.根据权利要求1所述的静电放电保护电路,其中,所述电阻元件包括互连器,所述互连器将所述第二二极管的端子耦合到所述第一二极管的对应端子并且具有电阻,在静电放电事件期间,所述电阻在所述第二二极管的所述端子与所述第一二极管的所述对应端子之间产生电压差。

3.根据权利要求1所述的静电放电保护电路,其中,所述电阻元件包括寄生电阻。

4.根据权利要求1所述的静电放电保护电路,其中,所述驱动电路被配置为从所述一个或多个核心电路接收控制输入。

5.根据权利要求1所述的静电放电保护电路,其中,所述驱动电路包括晶体管,所述晶体管具有栅极,所述栅极耦合到预驱动电路的输出端,所述预驱动电路从所述第二电源接收电力。

6.根据权利要求5所述的静电放电保护电路,其中,所述晶体管的漏极耦合到所述输入/输出焊盘。

7.根据权利要求1所述的静电放电保护电路,其中,在静电放电事件期间,静电放电电流通过所述输入/输出焊盘进入所述集成电路器件。

8.根据权利要求7所述的静电放电保护电路,其中,在所述静电放电电流进入所述集成电路器件之前,所述第一二极管和所述第二二极管被反向偏置。

9.根据权利要求1所述的静电放电保护电路,其中,所述驱动电路的运行电压电平大于所述一个或多个核心电路的运行电压电平。

10.根据权利要求1所述的静电放电保护电路,所述静电放电保护电路还包括:

11.根据权利要求1所述的静电放电保护电路,其中,所述第一二极管通过第三二极管耦合到所述集成电路器件的接地参考,所述第三二极管具有第一端子和第二端子,所述第一端子耦合到所述接地参考,所述第二端子耦合到所述输入/输出焊盘,并且其中所述第二二极管通过第四二极管耦合到所述接地参考,所述第四二极管具有第一端子和第二端子,所述第一端子耦合到所述接地参考,所述第二端子通过所述电阻元件耦合到所述输入/输出焊盘,其中所述电阻元件耦合到所述第三二极管的对应端子。

12.根据权利要求1所述的静电放电保护电路,其中,所述接口电路包括低功耗双倍数率同步动态随机存取存储器(lpddr sdram)接口电路。

13.根据权利要求1所述的静电放电保护电路,其中,所述驱动电路包括:

14.根据权利要求1所述的静电放电保护电路,其中,所述驱动电路包括:

15.一种设备,所述设备包括:

16.根据权利要求15所述的设备,其中,所述电阻元件包括与互连器相关联的电阻,并且被配置为在所述第二二极管的所述端子与所述第一二极管的所述对应端子之间产生电压差。

17.根据权利要求15所述的设备,其中,所述电阻元件包括寄生电阻。

18.根据权利要求15所述的设备,其中,用于驱动所述输入/输出焊盘的所述装置被配置为从所述一个或多个核心电路接收控制输入。

19.根据权利要求15所述的设备,其中,用于驱动所述输入/输出焊盘的所述装置包括晶体管,所述晶体管具有栅极,所述栅极耦合到预驱动电路的输出端,所述预驱动电路从所述第二电源接收电力。

20.根据权利要求19所述的设备,其中,所述晶体管的漏极耦合到所述输入/输出焊盘。

21.根据权利要求15所述的设备,其中,在静电放电事件期间,所述静电放电电流通过所述输入/输出焊盘进入所述集成电路器件。

22.根据权利要求21所述的设备,其中,在所述静电放电电流进入所述集成电路器件之前,所述第一二极管和所述第二二极管被反向偏置。

23.根据权利要求15所述的设备,其中,用于驱动所述输入/输出焊盘的所述装置的运行电压电平大于所述一个或多个核心电路的运行电压电平。

24.根据权利要求15所述的设备,所述设备还包括:

25.根据权利要求15所述的设备,其中:

26.根据权利要求15所述的设备,其中,所述接口电路包括低功耗双倍数率同步动态随机存取存储器(lpddr sdram)接口电路,所述lpddr sdram接口电路包括用于驱动输入/输出焊盘的所述装置。

27.根据权利要求15所述的设备,其中,用于驱动所述集成电路器件的所述输入/输出焊盘的所述装置包括:

28.根据权利要求15所述的设备,其中,用于驱动所述集成电路器件的所述输入/输出焊盘的所述装置包括:

29.一种用于保护接口电路免受静电放电的方法,所述方法包括:

30.根据权利要求29所述的方法,其中,所述电阻元件包括互连器,所述互连器将所述第二二极管的端子耦合到所述第一二极管的对应端子并且具有电阻,在静电放电事件期间,所述电阻在所述第二二极管的所述端子与所述第一二极管的所述对应端子之间产生电压差。

31.根据权利要求29所述的方法,其中,所述电阻元件包括寄生电阻。

32.根据权利要求29所述的方法,所述方法还包括:

33.根据权利要求29所述的方法,所述方法还包括:

34.根据权利要求33所述的方法,所述方法还包括:

35.根据权利要求29所述的方法,其中,在静电放电事件期间,所述静电放电电流通过所述输入/输出焊盘进入所述集成电路器件。

36.根据权利要求29所述的方法,其中,在所述静电放电电流进入所述集成电路器件之前,所述第一二极管和所述第二二极管被反向偏置。

37.根据权利要求29所述的方法,其中,所述驱动电路的运行电压电平大于所述一个或多个核心电路的运行电压电平。

38.根据权利要求29所述的方法,所述方法还包括:

39.根据权利要求29所述的方法,其中,所述第一二极管通过第三二极管耦合到所述集成电路器件的接地参考,所述第三二极管具有第一端子和第二端子,所述第一端子耦合到所述接地参考,所述第二端子耦合到所述输入/输出焊盘,并且其中所述第二二极管通过第四二极管耦合到所述接地参考,所述第四二极管具有第一端子和第二端子,所述第一端子耦合到所述接地参考,所述第二端子通过所述电阻元件耦合到所述输入/输出焊盘,其中所述电阻元件耦合到所述第三二极管的对应端子。

40.根据权利要求29所述的方法,其中,所述接口电路包括低功耗双倍数率同步动态随机存取存储器(lpddr sdram)接口电路,所述lpddr sdram接口电路包括所述驱动电路。

41.根据权利要求29所述的方法,所述方法还包括:

42.根据权利要求29所述的方法,所述方法还包括:

技术总结

接口电路中的ESD保护电路具有:第一二极管,该第一二极管耦合在集成电路器件的第一电源与该集成电路器件的输入/输出焊盘之间;第二二极管,该第二二极管耦合在该集成电路器件的第二电源与该输入/输出焊盘之间;和电阻元件,该电阻元件将该第二二极管耦合到该第一二极管和该输入/输出焊盘。该第一电源为驱动电路供电,该驱动电路耦合到该输入/输出焊盘。该第二电源为该集成电路器件的一个或多个核心电路供电。该电阻元件可实施为互连器,该互连器被配置为提供电阻,在静电放电事件期间,该电阻在该第二二极管的端子与该第一二极管的对应端子之间产生电压差。

技术研发人员:S·克里什纳姆尔迪,Y·U·严,A·塞图拉姆

受保护的技术使用者:高通股份有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!