至多个晶体管源极的自对准的宽背侧电力轨触点的制作方法

本公开内容的实施方式一般涉及到半导体装置。更具体地说,本公开内容的实施方式是针对电力轨(power rail)结构、3d封装和半导体装置的制造方法。

背景技术:

1、半导体处理行业继续努力提高产量,同时提高沉积在具有较大表面积的基板上的层的均匀性。这些同样的因素与新材料相结合,也为基板的单位面积提供了更高的电路集成度。随着电路集成度的提高,对更大的均匀性和层厚度的工艺控制的需求也在增加。因此,各种技术已经被开发出来,以一种具有成本效益的方式在基板上沉积层,同时保持对层的特性的控制。

2、半导体装置通常是通过在半导体基板上依次沉积绝缘层或介电层、导电层和半导体材料层,并使用光刻(lithography)对各种材料层进行图形化,以形成其上的电路部件和元素。导电层有利于各种电气部件的电气布线,包括晶体管、放大器、逆变器、控制逻辑、存储器、功率管理电路、缓冲器、过滤器、谐振器、电容器、电感器、电阻器和类似者。

3、晶体管是大多数集成电路的关键部件。由于晶体管的驱动电流(并且因而速度)与晶体管的栅极(gate)宽度成正比,因此更快的晶体管通常需要更大的栅极宽度。因此,在晶体管的尺寸和速度之间存在权衡,而“鳍式”场效应晶体管(finfets)已经被开发出来,以解决具有最大驱动电流和最小尺寸的晶体管的冲突目标。finfets的特点是有鳍状沟道区域,它大大增加了晶体管的尺寸,而没有明显增加晶体管的占地面积,而现在正被应用于许多集成电路。然而,finfets也有自己的缺点。

4、随着晶体管装置的特征尺寸不断缩小以实现更大的电路密度和更高的性能,有必要改进晶体管装置结构,以改善静电耦合并减少负面效应,如寄生电容和断态漏电(off-state leakage)。晶体管装置结构的例子包括平面结构、鳍式场效应晶体管(finfet)结构和水平环绕式栅极(hgaa)结构。hgaa装置结构包括几个晶格匹配的沟道,以堆叠的配置悬挂(suspend)并由源极/漏极区连接。hgaa结构提供了良好的静电控制,并可在互补金属氧化物半导体(cmos)晶片制造中得到广泛采用。

5、将半导体连接到电力轨上通常是在电池的正面进行,这需要大量的电池面积。因此,有着使用较少电池面积将半导体装置连接到电力轨上的需要。

技术实现思路

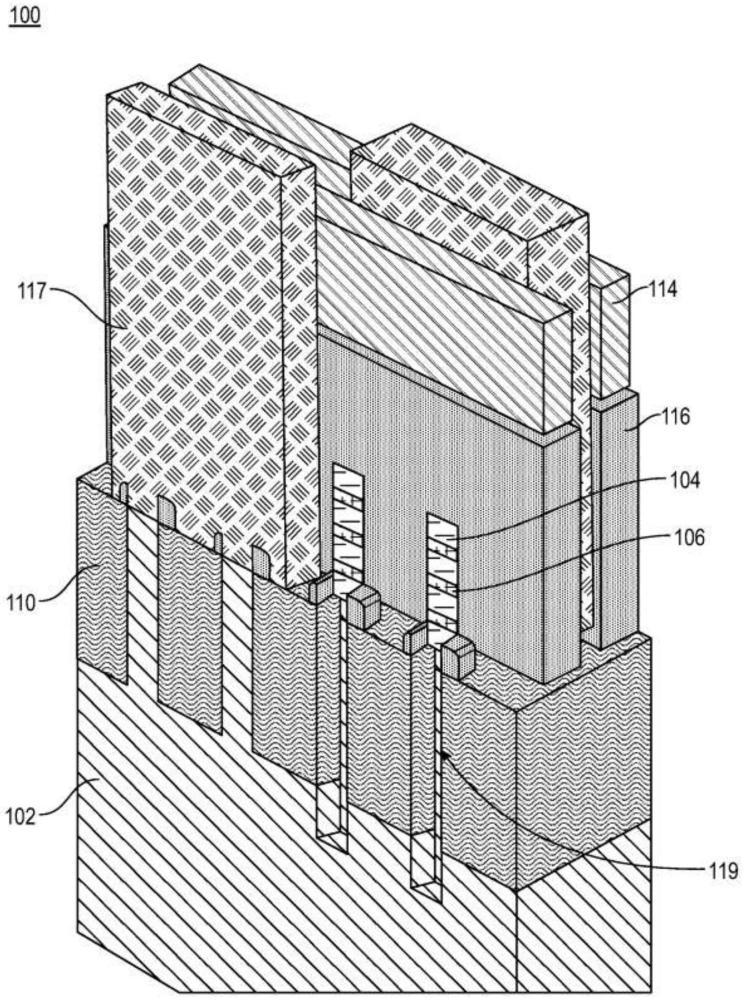

1、公开内容的一个或多个实施方式是针对形成半导体装置的方法。在一个或多个实施方式中,形成半导体装置的方法包括:在基板的顶表面上形成超晶格结构,超晶格结构包括交替排列成多个堆叠对的多个水平沟道层和相应多个半导体材料层;在基板上超晶格结构附近形成多个源极沟槽和多个漏极沟槽;扩大多个源极沟槽的至少一者和多个漏极沟槽的至少一者以形成源极空腔和漏极空腔;在源极空腔和漏极空腔中沉积牺牲材料;形成源极区和漏极区;形成与源极区和漏极区电连接的ct和cg;形成穿过基板的镶嵌沟槽;至少部分地移除牺牲材料以形成延伸至镶嵌沟槽的至少一个开口;以及在至少一个开口和镶嵌沟槽中沉积金属。

2、公开内容的额外实施方式是针对形成半导体装置的方法。在一个或多个实施方式中,形成半导体装置的方法包括:在基板的顶表面上形成超晶格结构,超晶格结构包括交替排列成多个堆叠对的多个水平沟道层和相应多个半导体材料层;在超晶格结构的顶表面上形成栅极结构;在基板上超晶格结构附近形成多个源极沟槽和多个漏极沟槽;扩大多个源极沟槽的至少一者和多个漏极沟槽的至少一者以形成源极空腔和漏极空腔;在源极空腔和漏极空腔中沉积牺牲材料;在多个水平沟道层的各个水平沟道层上形成内间隔物层;形成源极区和漏极区;在基板上形成层间介电层;形成替换金属栅极;形成与源极区和漏极区电连接的ct和cg;形成第一金属线;将半导体装置旋转180度;平坦化基板;平坦化基板;在基板上沉积层间电介质材料;在基板中形成背侧电力轨通孔;扩大背侧电力轨通孔以形成镶嵌沟槽;移除牺牲材料以形成至少一个开口;以及在至少一个开口和镶嵌沟槽中沉积金属。

技术特征:

1.一种形成半导体装置的方法,所述方法包括以下步骤:

2.如权利要求1所述的方法,其中扩大所述多个源极沟槽的至少一者和所述多个漏极沟槽的至少一者的步骤包括以下步骤:在所述多个源极沟槽的至少一者上和在所述多个漏极沟槽的至少一者上沉积硬掩模,且不在所述多个源极沟槽的至少一者和所述多个漏极沟槽的至少一者上沉积所述硬掩模,并蚀刻未掩蔽的源极沟槽和未掩蔽的漏极沟槽以形成源极空腔和漏极空腔。

3.如权利要求1所述的方法,其中所述牺牲材料被完全移除。

4.如权利要求1所述的方法,其中所述牺牲材料包括硅锗(sige)。

5.如权利要求4所述的方法,其中所述硅锗(sige)的锗(ge)含量在从30%至50%的范围内。

6.如权利要求4所述的方法,其中所述硅锗(sige)掺杂有掺杂剂,所述掺杂剂选自由硼(b)、镓(ga)、磷(p)、砷(as)及其组合所构成的组。

7.如权利要求1所述的方法,其中形成所述镶嵌沟槽的步骤包括以下步骤:蚀刻至少一个通孔进入所述基板并扩大所述通孔以形成所述镶嵌沟槽。

8.如权利要求1所述的方法,其中所述多个半导体材料层和所述多个水平沟道层独立地包括硅锗(sige)和硅(si)的一者或多者。

9.如权利要求1所述的方法,其中形成所述源极区和所述漏极区的步骤包括以下步骤:在其上生长外延层。

10.如权利要求1所述的方法,其中所述源极区和所述漏极区独立地掺杂有磷(p)、砷(as)、硼(b)和镓(ga)的一者或多者。

11.如权利要求1所述的方法,进一步包括以下步骤:在所述超晶格结构的顶表面上形成栅极结构。

12.如权利要求11所述的方法,进一步包括以下步骤:在所述栅极结构上和在所述超晶格结构上形成介电层。

13.如权利要求12所述的方法,其中所述栅极结构包括钨(w)、钴(co)、钼(mo)、钌(ru)、氮化钛(tin)、氮化钽(tan)、钛铝(tial)和n型掺杂多晶硅中的一者或多者。

14.如权利要求1所述的方法,其中所述金属包括钛(ti)、氮化钛(tin)、钽(ta)、氮化钽(tan)、钨(w)、钼(mo)、钴(co)、铜(cu)和钌(ru)中的一者或多者。

15.一种形成半导体装置的方法,所述方法包括以下步骤:

16.如权利要求15所述的方法,其中扩大所述多个源极沟槽的至少一者和所述多个漏极沟槽的至少一者的步骤包括以下步骤:在所述多个源极沟槽的至少一者上和在所述多个漏极沟槽的至少一者上沉积硬掩模,且不在所述多个源极沟槽的至少一者和所述多个漏极沟槽的至少一者上沉积所述硬掩模,并蚀刻未掩蔽的源极沟槽和未掩蔽的漏极沟槽以形成源极空腔和漏极空腔。

17.如权利要求15所述的方法,其中所述牺牲材料包括硅锗(sige)。

18.如权利要求17所述的方法,其中所述硅锗(sige)的锗(ge)含量在从30%至50%的范围内。

19.如权利要求17所述的方法,其中所述硅锗(sige)掺杂有掺杂剂,所述掺杂剂选自由硼(b)、镓(ga)、磷(p)、砷(as)及其组合所构成的组。

20.如权利要求15所述的方法,其中形成所述源极区和所述漏极区的步骤包括以下步骤:在其上生长外延层。

技术总结

描述了半导体装置和其制造方法。方法包括正面处理以形成深的源极/漏极空腔,并用牺牲材料填充空腔。然后在背侧处理过程中移除牺牲材料,以形成填充有金属填料的背侧电力轨通孔。

技术研发人员:苏克图·阿伦·帕里克,阿希什·派欧,埃尔·迈赫迪·巴齐兹,安德鲁·杨,妮琴·K·英吉,阿尔文·桑德拉扬,徐源辉,马蒂纳斯·玛丽亚·贝尔肯斯,萨梅尔·A·德什潘德,B·普拉纳瑟提哈兰,杨雁筑

受保护的技术使用者:应用材料公司

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!