一种减小寄生电容couple影响的阵列基板及其制作方法与流程

本发明涉及显示器,具体地涉及一种减小寄生电容couple影响的阵列基板及其制作方法。

背景技术:

1、对于tft-lcd显示器而言,一般把与画素电极相连的tft一侧叫做漏极,漏极与栅极金属之间形成的电容叫做寄生电容cgd。tft器件的栅极与横向分布的栅极线连接,用于控制tft器件的开与关;tft器件的源极与纵向分布的数据线连接,用于往tft器件写入想要显示的数据电压;当tft打开时,源极与漏极导通,数据电压进入漏极再由画素电极到达液晶电容cst,调节液晶的透光率;当tft关闭时,源极与漏极截止断开,源极的数据电压就不能进入漏极。源极的数据电压是呈周期性地正负极性变化,是使液晶产生正负极性的偏转电压。

2、结合图1与图2,在tft关闭的瞬间,栅极电压vg从高电平的vhigh瞬间下降到低电平的vlow,由于寄生电容cgd的存在会将vg的瞬间变化耦合到漏极,由于寄生电容couple影响(耦合影响),导致漏极电压下降,又由于此时tft器件已关闭,画素电极与漏极之间产生的电压差会造成画素电极的电压发生跳变,这个跳变量δv我们称之为feedthrough电压。在图2的波形图之中,vg是栅极电压,vd是理想状态的漏极电压,是实际提供的公共电极电压即实际提供的正负极性偏转电压的中心点,vp(t)是实际的像素电极电压,vcom是当前使液晶在正负极性状态下保持两端电压一样的理想状态的公共电极电压,voffset是理想状态的公共电极电压与实际提供的公共电极电压的偏离量,tf是tft器件的开关周期,vlc>vcom是像素电极电压大于当前理想状态的公共电极电压的区域,vlc<vcom是像素电极电压小于当前理想状态的公共电极电压的区域。

3、如图2所示,由于feedthrough电压的存在,会导致理想状态的公共电极vcom点位偏离实际提供的正负极性偏转电压的中心位置,即理想状态的公共电极电压发生变化,但实际提供正负极性偏转电压不变,这就导致液晶在正负极性状态下的两端电压不一样,这样就会造成正负极性下液晶的偏转角度不一样,从而阵列基板的通光量不一样,造成液晶显示器画面的闪烁。所以减小feedthrough电压是目前应该解决的问题。

技术实现思路

1、本发明要解决的技术问题,在于提供一种减小寄生电容couple影响的阵列基板及其制作方法,通过在漏极上方设置导电层,导电层的电位高低与栅极的电位高低相反,栅极对于漏极的耦合效应和导电层对于漏极的耦合效应相互抵消,减小寄生电容couple影响,从而减小feedthrough电压。

2、本发明是这样实现的:

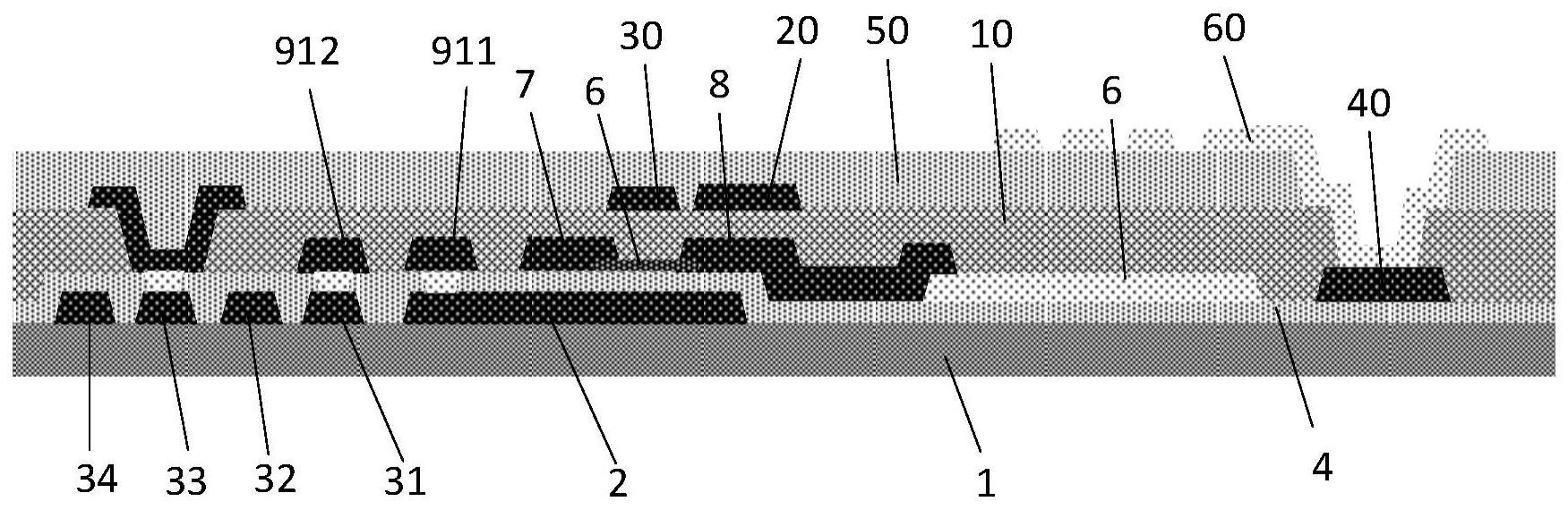

3、一种减小寄生电容couple影响的阵列基板,包括:

4、玻璃衬底;

5、第一金属层,镀在所述玻璃衬底的上表面,形成了间隔分布的栅极、第一ck信号走线与第三ck信号走线,所述第一ck信号走线的电位高低与所述第三ck信号走线的电位高低相反;

6、栅绝缘层,镀在所述玻璃衬底与所述第一金属层的上表面,所述栅绝缘层开设有第一挖孔、第二挖孔与第三挖孔,所述栅极露出于所述第一挖孔,所述第一ck信号走线露出于所述第二挖孔,所述第三ck信号走线露出于所述第三挖孔;

7、画素电极,镀在所述栅绝缘层的上表面,还位于所述栅极的侧方;

8、第一电极块,镀在所述第一挖孔,还与所述栅极连接;

9、第二电极块,镀在所述第二挖孔,还与所述第一ck信号走线连接;

10、第三电极块,镀在所述第三挖孔,还与所述第三ck信号走线连接;

11、所述第一电极块、第二电极块、第三电极块与所述画素电极的材料相同;

12、有源层,镀在栅极绝缘层的上表面,还位于所述栅极的正上方;

13、第二金属层,镀在所述栅绝缘层的上表面,形成了间隔分布的源极、漏极与第一信号连接线,所述源极与所述有源层的左端连接,所述漏极与所述有源层的右端连接,所述漏极还与所述画素电极连接,所述第一信号连接线的右端与所述第一电极块连接,所述第一信号连接线的左端与所述第二电极块连接;

14、钝化层,镀在所述栅绝缘层、有源层、第二金属层、画素电极的上表面,所述钝化层开设有第四挖孔,所述第三电极块露出于所述第四挖孔;

15、导电层,镀在所述钝化层的上表面,还位于所述漏极的正上方,所述钝化层的上表面还镀有第二信号连接线,所述导电层与所述第二信号连接线的右端连接,所述第二信号连接线的左端穿过所述第四挖孔与所述第三电极块连接;

16、遮光金属层,镀在所述钝化层的上表面,还位于所述有源层的沟道正上方,所述遮光金属层与所述导电层、第二信号连接线间隔设置;

17、所述遮光金属层、导电层、第二信号连接线与所述第一金属层的材料相同。

18、进一步地,还包括:

19、所述第二金属层还形成了间隔分布的tp走线;

20、外绝缘层,镀在所述导电层、遮光金属层、钝化层的上表面,所述外绝缘层开设有第五挖孔,所述第五挖孔穿透所述钝化层,所述tp走线露出于所述第五挖孔;

21、公共电极,镀在所述外绝缘层的上表面,所述公共电极还穿过所述第五挖孔与所述tp走线连接。

22、进一步地,所述第一金属层、第二金属层、导电层、第二信号连接线、遮光金属层都是ti/al/ti三层结构或者mo/al/mo三层结构。

23、进一步地,所述栅绝缘层是siox单层结构或者sinx/siox双层结构,所述钝化层是sio2材质,所述外绝缘层是siox或者sino或者sinx材质。

24、进一步地,所述有源层是igzo材质,所述画素电极、第一电极块、第二电极块、第三电极块与公共电极都是ito材质。

25、进一步地,所述第一金属层还形成了间隔分布的第二ck信号走线与第四ck信号走线,所述第二ck信号走线的电位高低与所述第四ck信号走线的电位高低相反;

26、所述第一ck信号走线是与第一行的阵列基板的栅极连接,所述第二ck信号走线是与第二行的阵列基板的栅极连接,所述第三ck信号走线是与第一行的阵列基板的导电层连接,所述第四ck信号走线是与第二行的阵列基板的导电层连接。

27、进一步地,所述第一ck信号走线的信号时序相位比所述第二ck信号走线的信号时序相位提早四分之一周期,所述第三ck信号走线的信号时序相位比所述第四ck信号走线的信号时序相位提早四分之一周期。

28、一种减小寄生电容couple影响的阵列基板的制作方法,包括以下步骤:

29、s1、将第一金属层镀在玻璃衬底的上表面,形成间隔分布的栅极、第一ck信号走线与第三ck信号走线,所述第一ck信号走线的电位高低与所述第三ck信号走线的电位高低相反;

30、s2、将栅绝缘层镀在所述玻璃衬底与所述第一金属层的上表面;

31、s3、在所述栅绝缘层开设第一挖孔、第二挖孔与第三挖孔,所述栅极露出于所述第一挖孔,所述第一ck信号走线露出于所述第二挖孔,所述第三ck信号走线露出于所述第三挖孔;

32、s4、将画素电极镀在所述栅绝缘层的上表面,所述画素电极还位于所述栅极的侧方;

33、将第一电极块、第二电极块、第三电极块分别镀在所述第一挖孔、第二挖孔、第三挖孔,所述第一电极块与所述栅极连接,所述第二电极块与所述第一ck信号走线连接,所述第三电极块与所述第三ck信号走线连接;

34、所述第一电极块、第二电极块、第三电极块与所述画素电极的材料相同;

35、s5、将有源层镀在所述栅绝缘层的上表面,所述有源层位于所述栅极的正上方;

36、s6、将第二金属层镀在所述栅绝缘层的上表面,形成间隔分布的源极、漏极与第一信号连接线,所述源极与所述有源层的左端连接,所述漏极与所述有源层的右端连接,所述漏极还与所述画素电极连接,所述第一信号连接线的右端与所述第一电极块连接,所述第一信号连接线的左端与所述第二电极块连接;

37、s7、将钝化层镀在所述栅绝缘层、有源层、第二金属层、画素电极的上表面;

38、在所述钝化层开设第四挖孔,所述第三电极块露出于所述第四挖孔;

39、s8、将导电层、第二信号连接线与遮光金属层镀在所述钝化层的上表面,所述导电层还位于所述漏极的正上方,所述导电层与所述第二信号连接线的右端连接,所述第二信号连接线的左端穿过所述第四挖孔与所述第三电极块连接,所述遮光金属层还位于所述有源层的沟道正上方,所述遮光金属层与所述导电层、第二信号连接线间隔设置;

40、所述遮光金属层、导电层与所述第一金属层的材料相同。

41、进一步地,还包括:

42、在所述s6之中,所述第二金属层还形成了间隔分布的tp走线;

43、s9、将外绝缘层镀在所述导电层、遮光金属层、钝化层的上表面,所述外绝缘层开设第五挖孔,所述第五挖孔穿透所述钝化层,所述tp走线露出于所述第五挖孔;

44、s10、将公共电极镀在所述外绝缘层的上表面,所述公共电极的引线穿过所述第五挖孔与所述tp走线连接。

45、进一步地,所述第一金属层、第二金属层、导电层、第二信号连接线、遮光金属层都是ti/al/ti三层结构或者mo/al/mo三层结构。

46、本发明的优点在于:1、在漏极上方设置导电层,导电层与漏极之间形成补充电容,栅极的信号由第一ck信号走线提供,导电层的信号由第三ck信号走线提供,导电层的电位高低与栅极的电位高低相反,栅极对于漏极的耦合效应和导电层对于漏极的耦合效应相互抵消,减小画素电极与漏极之间产生的电压差,减小寄生电容couple影响,从而减小feedthrough电压,降低液晶显示器的画面闪烁;当补充电容与寄生电容大小相等时,消除feedthrough电压,提高液晶显示器的画面显示稳定性。2、导电层是设置在靠近漏极与有源层接触的位置,该位置的场强会更大,这样就可以降低有源层半导体和漏极的金属线接触形成的肖特基势垒,可以降低接触电阻,从而增大开态电流。3、ito具有良好的导电性和透光性,本发明的画素电极、第一电极块、第二电极块与第三电极块的选材都是ito,所以画素电极、第一电极块、第二电极块与第三电极块可以在同一道工艺中成膜,这样就可以简化基板结构,提高产能。4、通过在栅绝缘层预先开设第一挖孔、第二挖孔与第三挖孔,然后分别填充第一电极块、第二电极块与第三电极块,避免了后序制程蚀刻对第一金属层的金属造成影响。5、导电层没有覆盖到有源层的沟道,但是在有源层的沟道正上方镀有浮空的遮光金属层,可以起到遮光作用,提高tft器件的稳定性。

- 还没有人留言评论。精彩留言会获得点赞!