半导体器件及其制造方法与流程

本发明的实施例涉及半导体器件及其制造方法。

背景技术:

1、由于各种电子组件(例如晶体管、二极管、电阻器、电容器等)的集成密度不断提高,半导体工业经历了快速增长。在大多数情况下,集成密度的这种改进来自于最小部件尺寸的反复减小,这允许将更多不同和/或相同的组件集成到给定区域中。

技术实现思路

1、本发明的一些实施例提供了一种半导体器件,该半导体器件包括:衬底;第一栅极区域,延伸到衬底中并且具有第一u形的至少部分;沟道区域,延伸到衬底中并且具有第二u形;以及第二栅极区域,延伸到衬底中并且具有井形;其中,井形设置在第二u形之间,并且第二u形还设置在第一u形之间。

2、本发明的另一些实施例提供了一种半导体器件,该半导体器件包括:第一结型场效应晶体管,该第一结型场效应晶体管包括:第一栅极区域,延伸到衬底中并且具有第一导电类型;第一沟道区域,延伸到衬底中并且具有与第一导电类型相反的第二导电类型,其中,第一沟道区域具有由第一栅极区域围绕的下边界;以及第二栅极区域,延伸到衬底中并且具有第一导电类型,其中,第二栅极区域具有由第一沟道区域围绕的下边界。

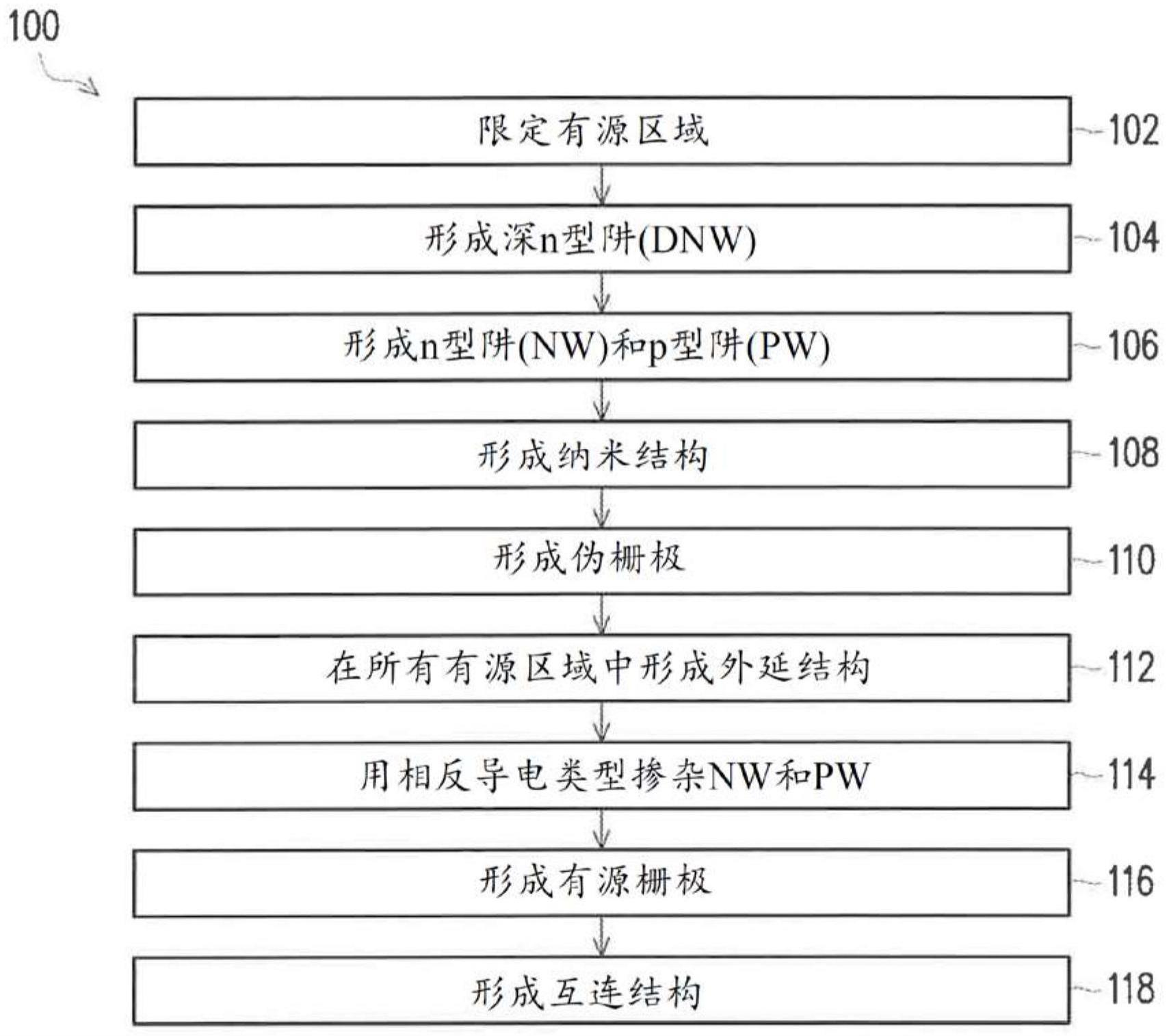

3、本发明的又一些实施例提供了一种制造半导体器件的方法,包括:(a)形成延伸到衬底中并且具有第一u形的至少垂直部分的第一栅极区域,其中,第一栅极区域具有第一导电类型;(b)形成延伸到衬底中并且具有由第一u形围绕的第二u形的沟道区域,其中,沟道区域具有第二导电类型;(c)形成分别耦接至第一栅极区域的端部部分的一对第一外延结构,其中,第一外延结构具有第一导电类型;(d)形成分别耦接至沟道区域的端部部分的一对第二外延结构,其中,第二外延结构具有第二导电类型;(e)形成具有第一导电类型并且由第二u形围绕的第三外延结构;以及(f)形成延伸到衬底中并且设置在第三外延结构之下的第二栅极区域,其中,第二栅极区域具有第一导电类型。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中,所述第一栅极区域具有第一导电类型,所述沟道区域具有与所述第一导电类型相反的第二导电类型,并且所述第二栅极区域具有所述第一导电类型,从而形成结型场效应晶体管。

3.根据权利要求2所述的半导体器件,其中,所述第一栅极区域具有第一掺杂浓度,并且所述第二栅极区域具有第二掺杂浓度,所述第二掺杂浓度显著高于所述第一掺杂浓度。

4.根据权利要求1所述的半导体器件,还包括:

5.根据权利要求1所述的半导体器件,还包括:

6.根据权利要求5所述的半导体器件,其中,所述第一外延结构、所述第二外延结构、所述第三外延结构和所述第四外延结构在一个或多个外延工艺中同时形成。

7.根据权利要求5所述的半导体器件,还包括将所述第二外延结构中的一个外延结构电耦接至所述第四外延结构中的一个外延结构的一个或多个互连结构。

8.根据权利要求1所述的半导体器件,其中,所述第一栅极区域和第二栅极区域被配置为沿着所述沟道区域共同地生成耗尽区域。

9.一种半导体器件,包括:

10.一种制造半导体器件的方法,包括:

技术总结

半导体器件包括衬底。该半导体器件包括延伸到衬底中并且具有第一U形的至少部分的第一栅极区域。该半导体器件包括延伸到衬底中并且具有第二U形的沟道区域。该半导体器件包括延伸到衬底中并且具有井形的第二栅极区域。井形设置在第二U形之间,并且第二U形还设置在第一U形之间。本发明的实施例还提供了制造半导体器件的方法。

技术研发人员:陈家忠,苏子昂,刘雅芸,郑仪侃

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!